Buffering method of SDH class logical simulation excitation data

A technology for logic simulation and excitation data, applied in the field of communication or electronics, it can solve the problems of slow SDH logic simulation speed, inconvenient parameter configuration and modification, etc., to achieve the effect of improving efficiency, improving automation and fast access.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

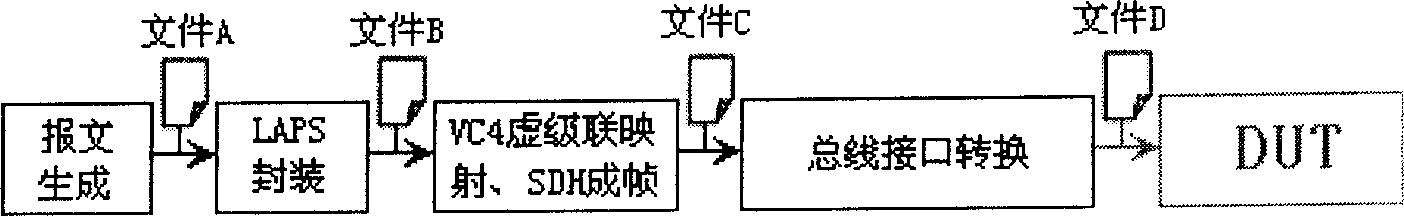

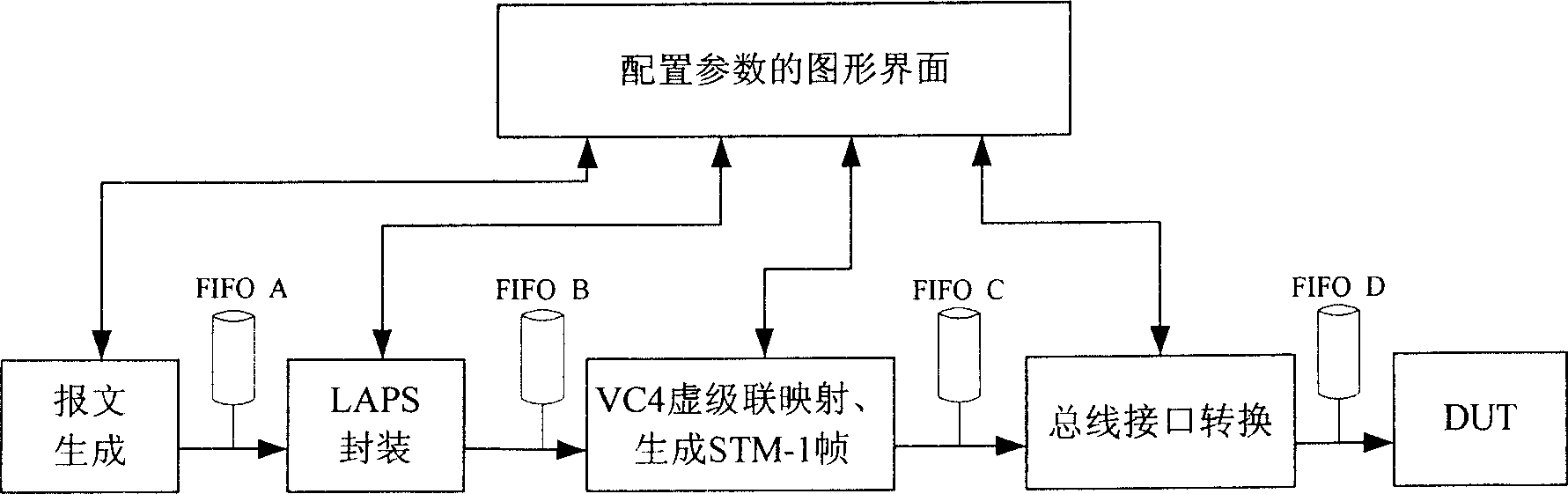

[0021] The technical solution provided by the present invention is different from the prior art solution in that: one is to consider all the modules produced by the SDH logic simulation excitation as a whole, and each module is no longer independent of each other, but is related before and after; The second is to use a FIFO (First Input First Output) device (the storage medium can be the memory of the computer) to replace the files in the original technical solution (the storage medium is the hard disk of the computer), which can greatly speed up the access of the incentive generation program to the intermediate data Speed, and all configured parameters are stored in the memory, and the value of the parameters involved in each module can be dynamically accessed by designing a corresponding graphical interface.

[0022] The work process that the SDH class logic simulation stimulus data of the present invention produces is as follows figure 2 As shown, the description is as fol...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More