Flash memory unit, flash memory unit array and mfg. method thereof

A memory cell array and memory cell technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., can solve the problems of slow operation speed of memory cells, small reading current of memory cells, and inability to improve device performance, etc. , to achieve the effect of improving operation speed and performance, improving gate coupling rate, and high electron injection efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

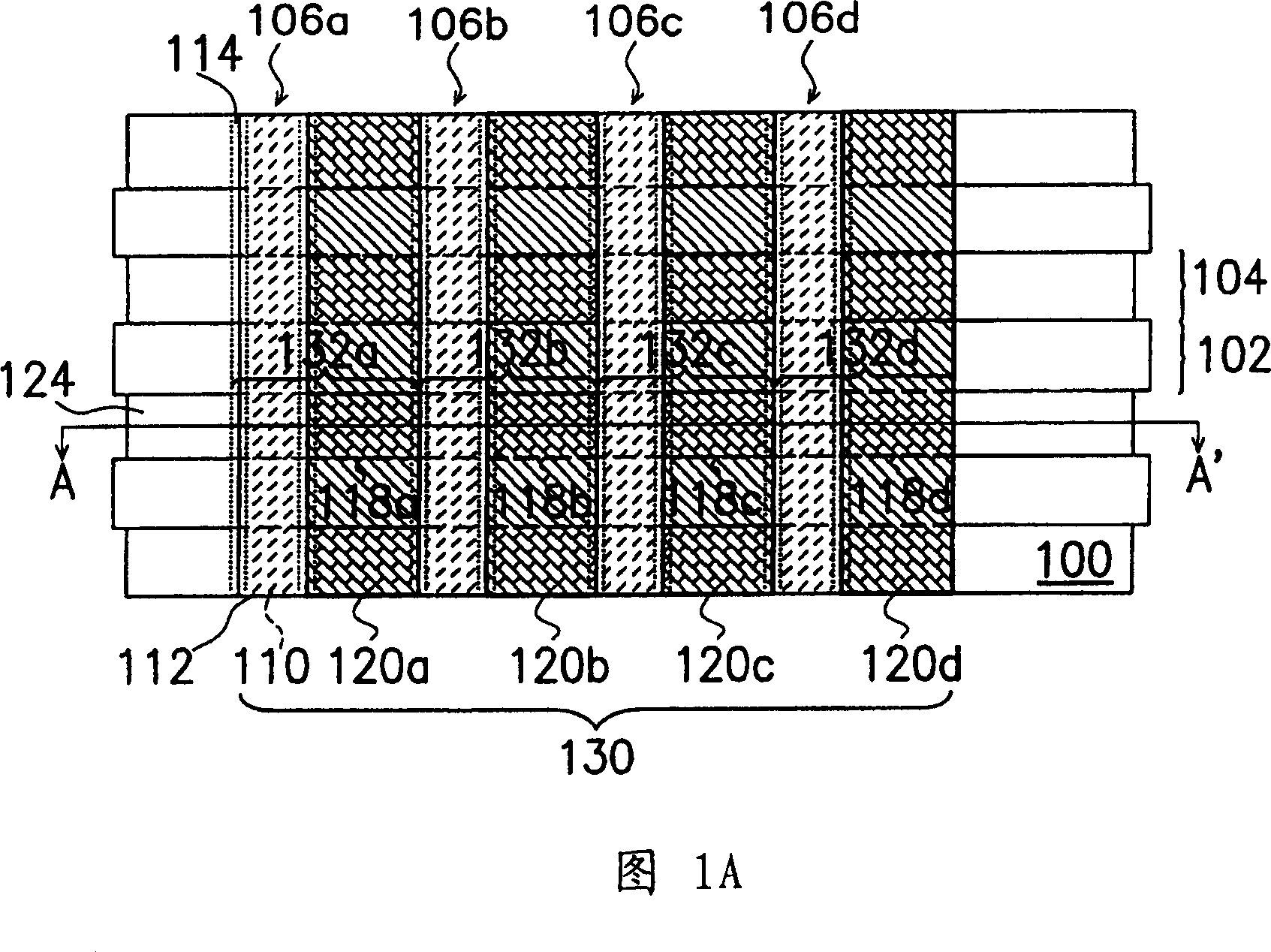

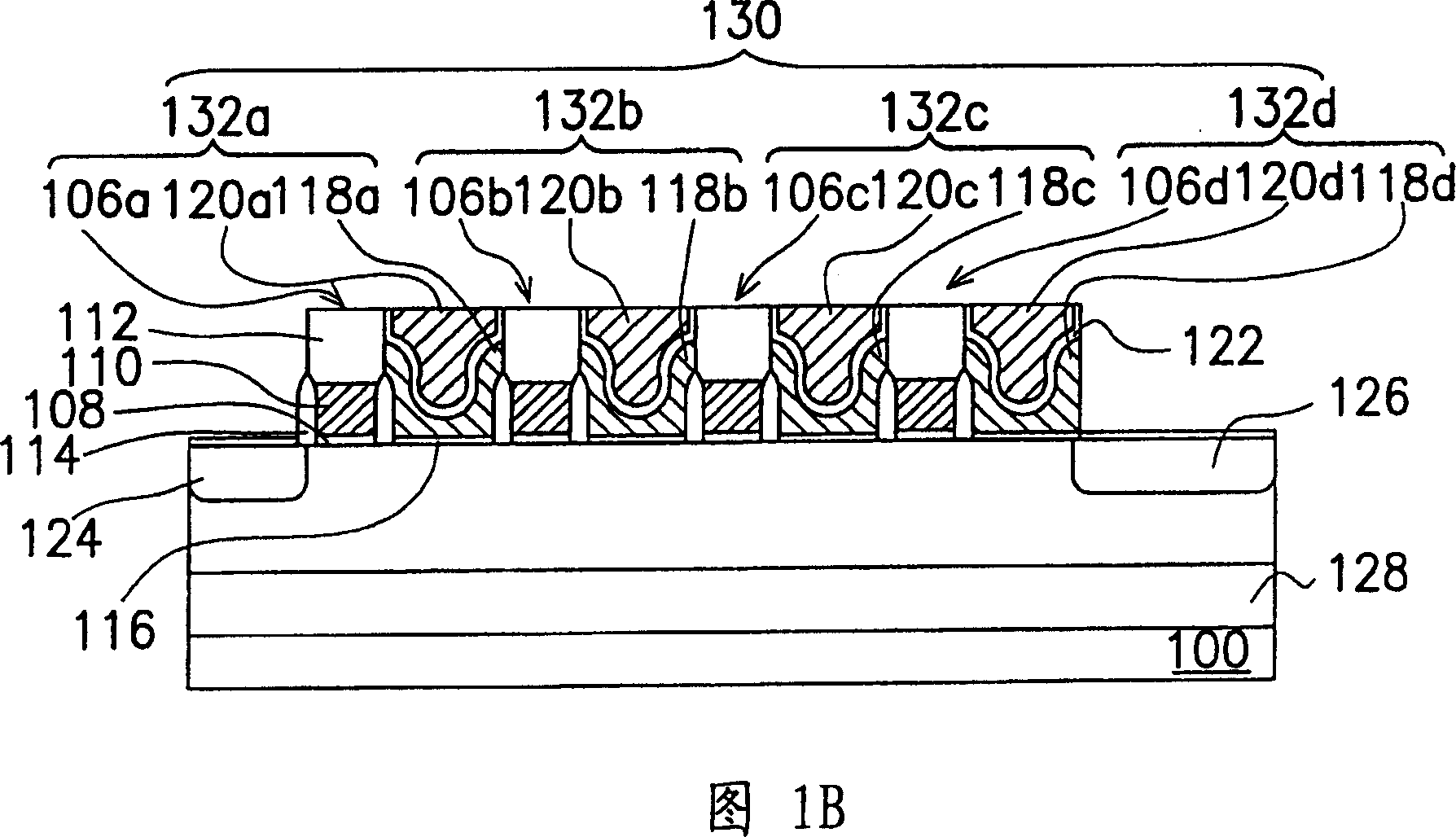

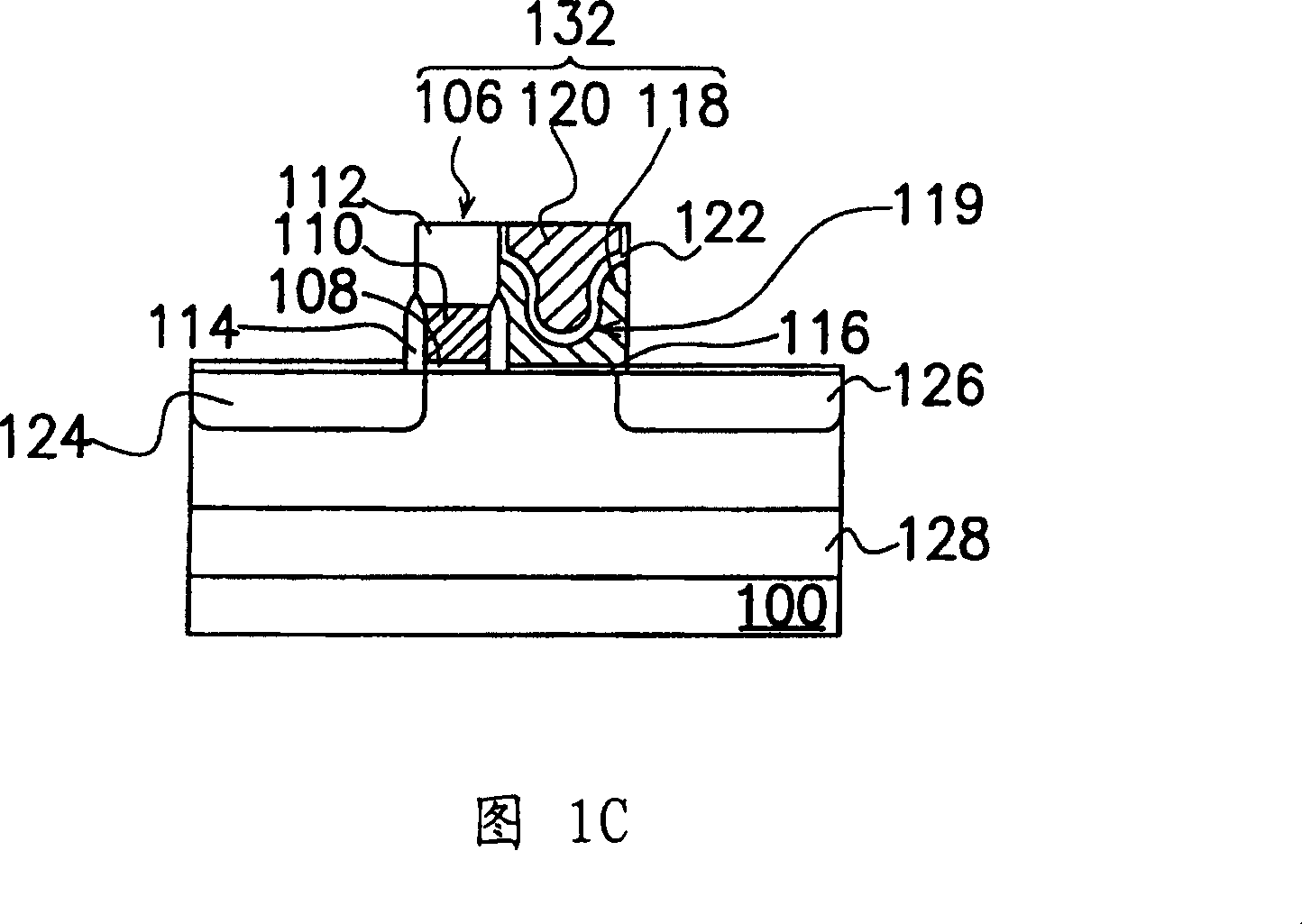

[0045] FIG. 1A is a top view showing a NAND type flash memory cell array of the present invention. Fig. 1B is a cross-sectional view showing the structure along line A-A' in Fig. 1A.

[0046] Please refer to FIG. 1A and FIG. 1B at the same time. The flash memory cell array structure of the present invention is at least composed of a substrate 100, an element isolation structure 102, an active region 104, and a plurality of stacked gate structures 106a-106d (each stacked gate structure 106a-106d are sequentially from the substrate 100 the selection gate dielectric layer 108, the selection gate 110, the top cover layer 112), the spacer 114, the tunneling dielectric layer 116, and a plurality of floating gates 118a-118d , a plurality of control gates 120 a - 120 d , an inter-gate dielectric layer 122 , a drain region 124 , and a source region 126 .

[0047] The substrate 100 is, for example, a P-type silicon substrate, and a deep N-type well region 128 is provided in the substra...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More