Patents

Literature

73results about How to "Improve gate coupling ratio" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

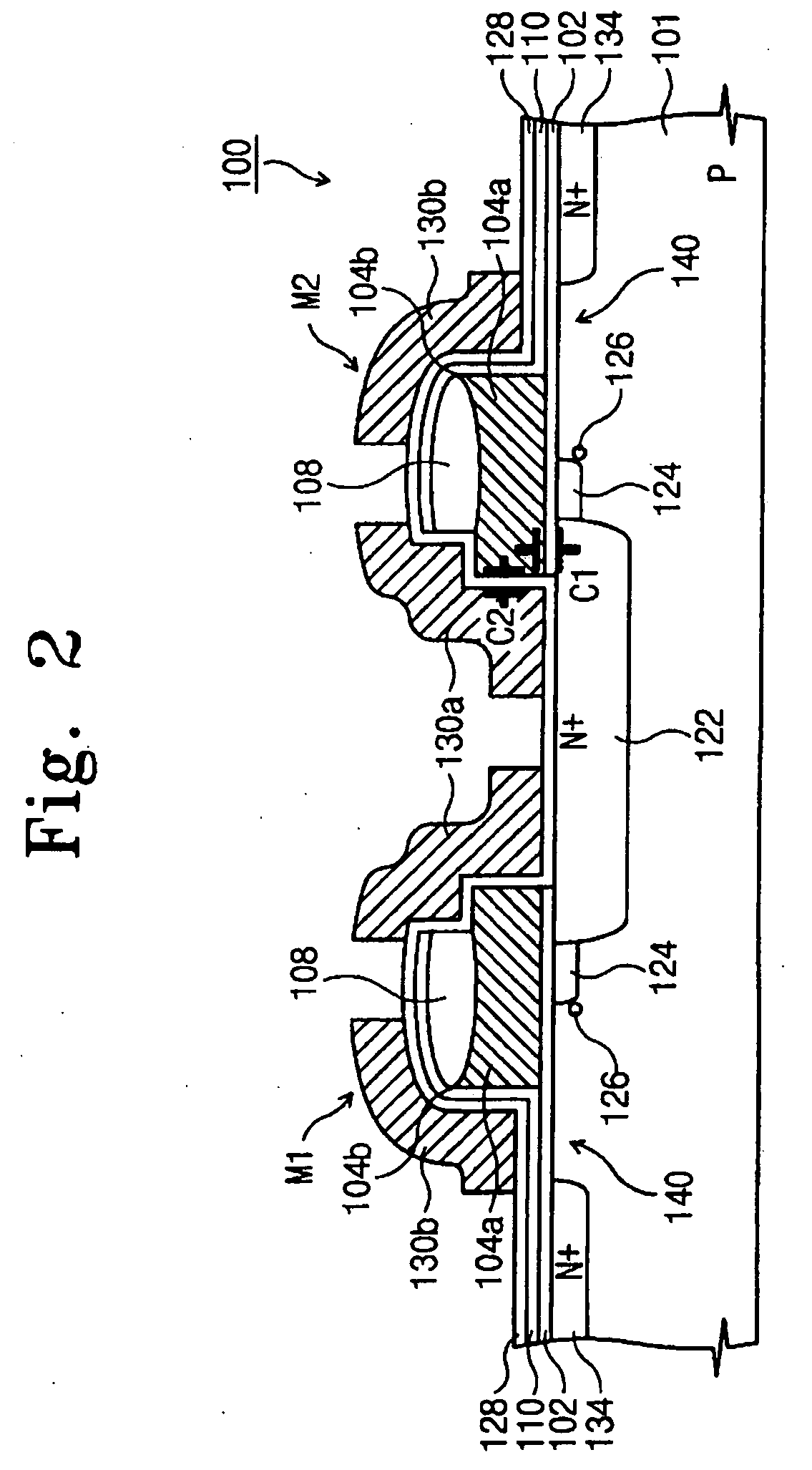

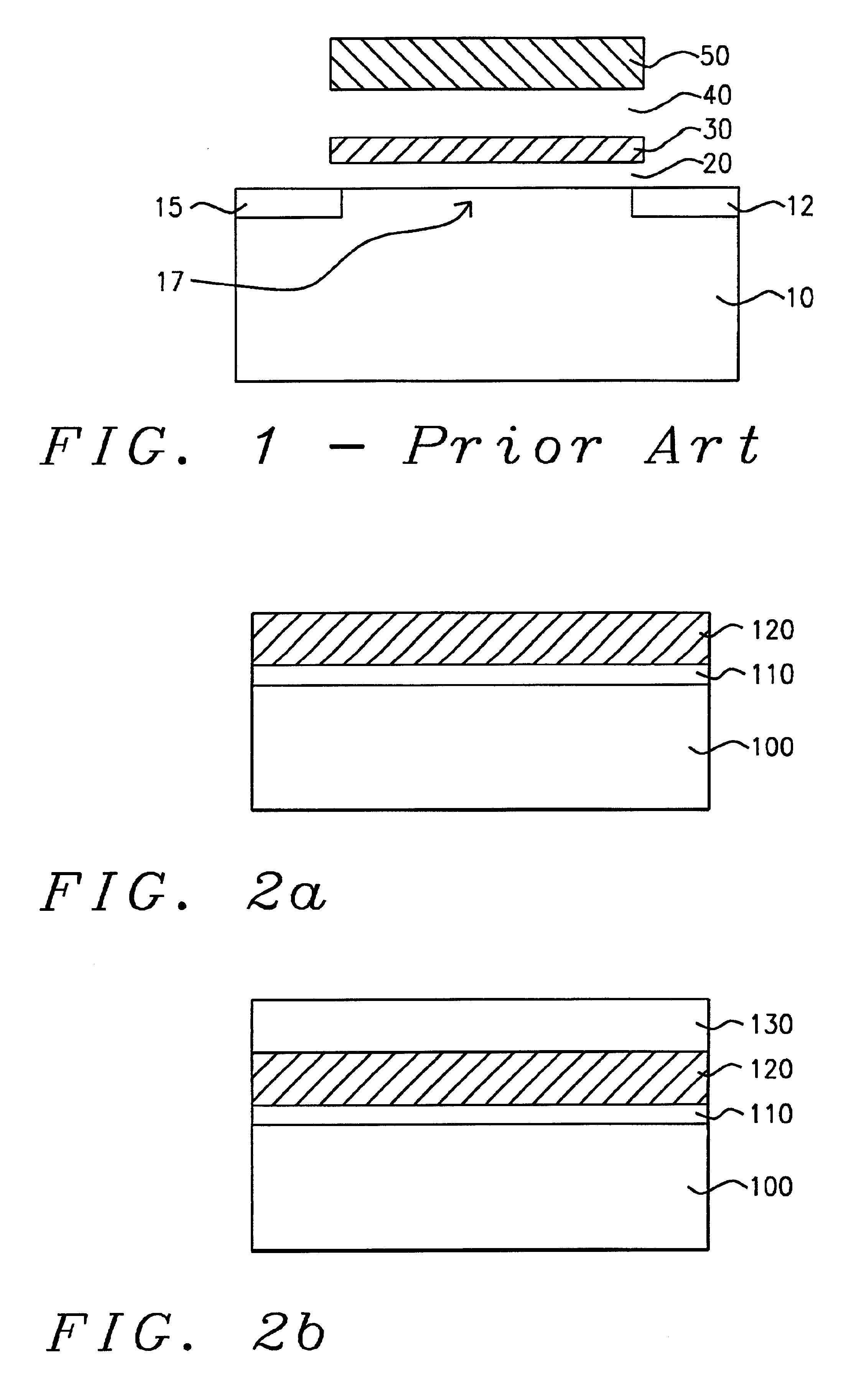

Split gate non-volatile memory devices and methods of forming same

InactiveUS20060202255A1Increased floating gate coupling ratioAccelerated programTransistorSolid-state devicesCoupling ratioEngineering

Non-volatile memory devices and methods for fabricating non-volatile memory devices are disclosed. More specifically, split gate memory devices are provided having frameworks that provide increased floating gate coupling ratios, thereby enabling enhanced programming and erasing efficiency and performance.

Owner:SAMSUNG ELECTRONICS CO LTD

Split gate non-volatile memory devices and methods of forming the same

InactiveUS20080093647A1Increased floating gate coupling ratioAccelerated programTransistorCoupling ratioEngineering

Non-volatile memory devices and methods for fabricating non-volatile memory devices are disclosed. More specifically, split gate memory devices are provided having frameworks that provide increased floating gate coupling ratios, thereby enabling enhanced programming and erasing efficiency and performance.

Owner:SAMSUNG ELECTRONICS CO LTD

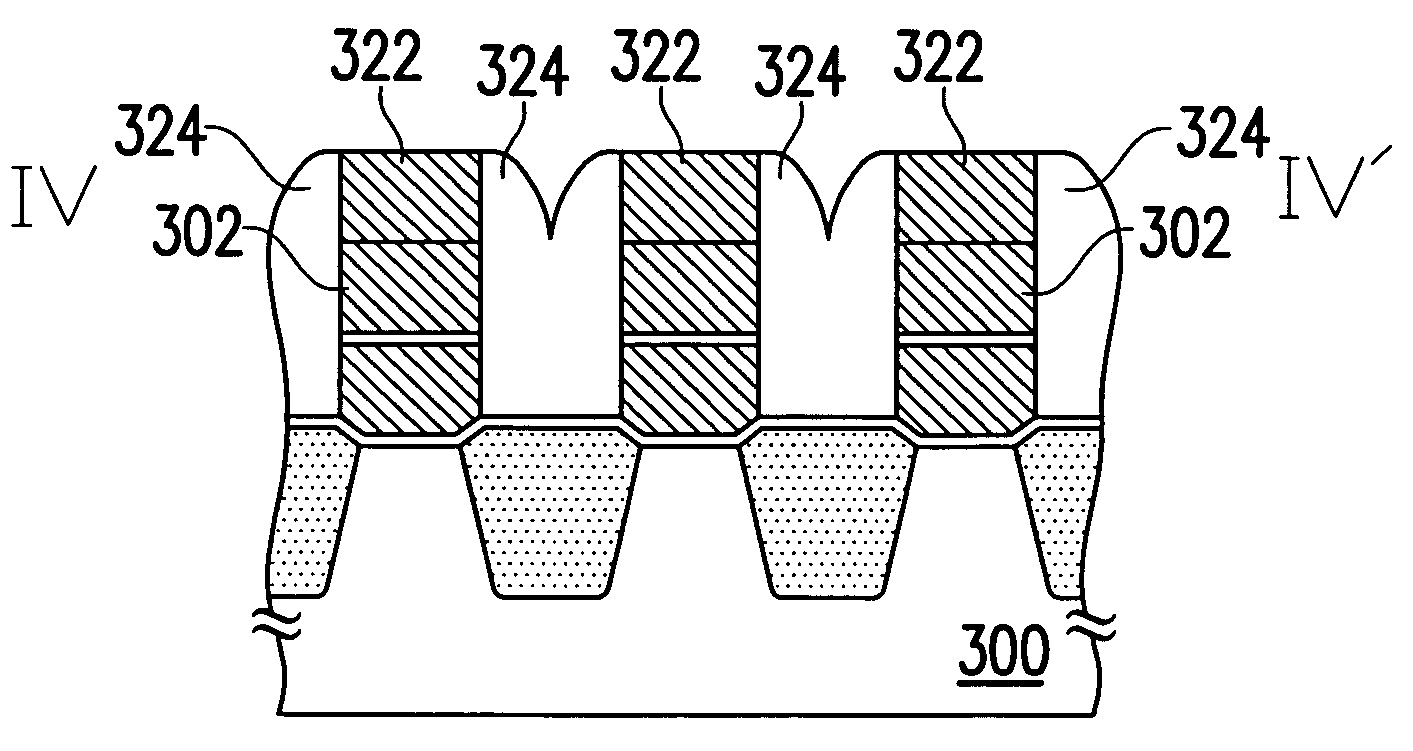

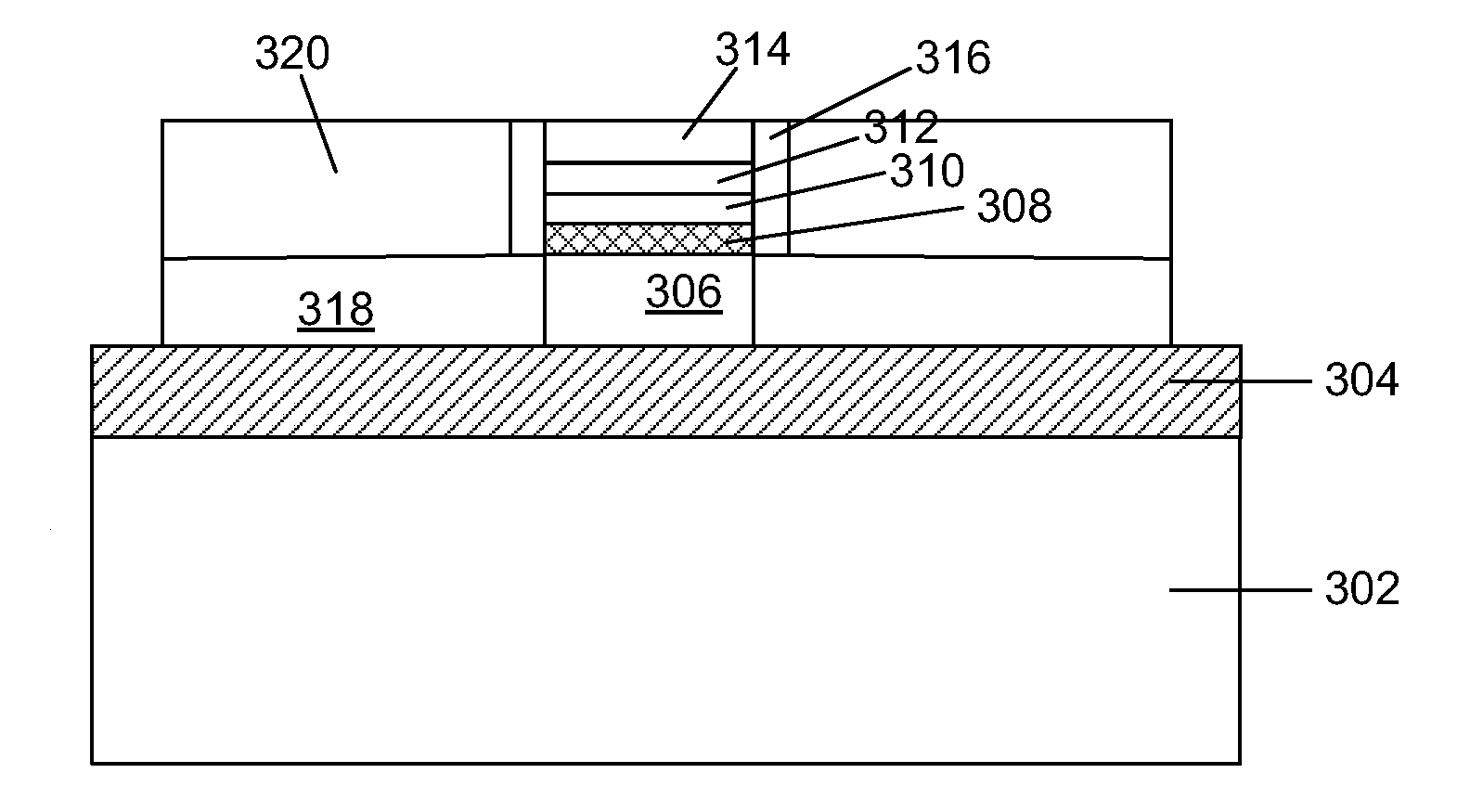

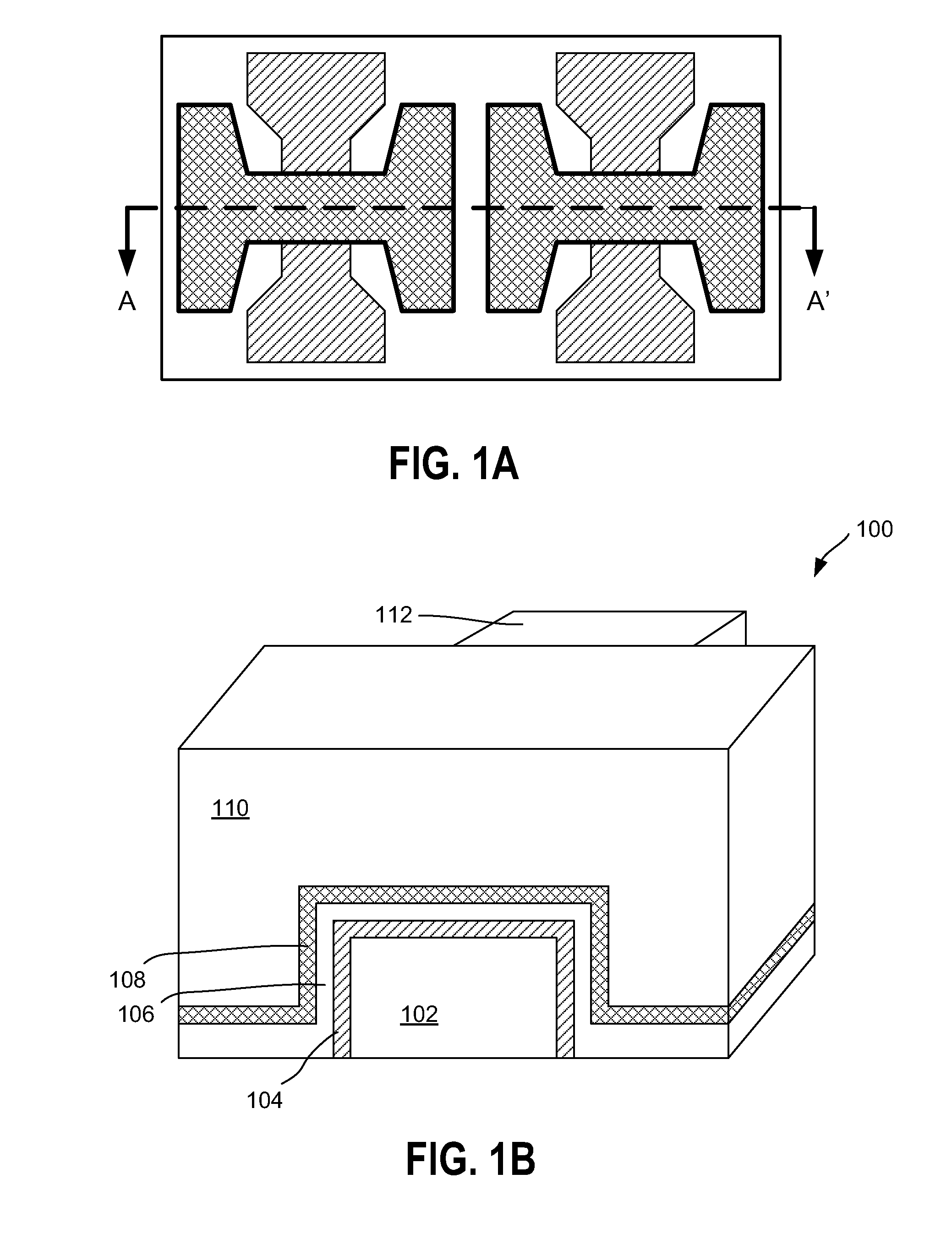

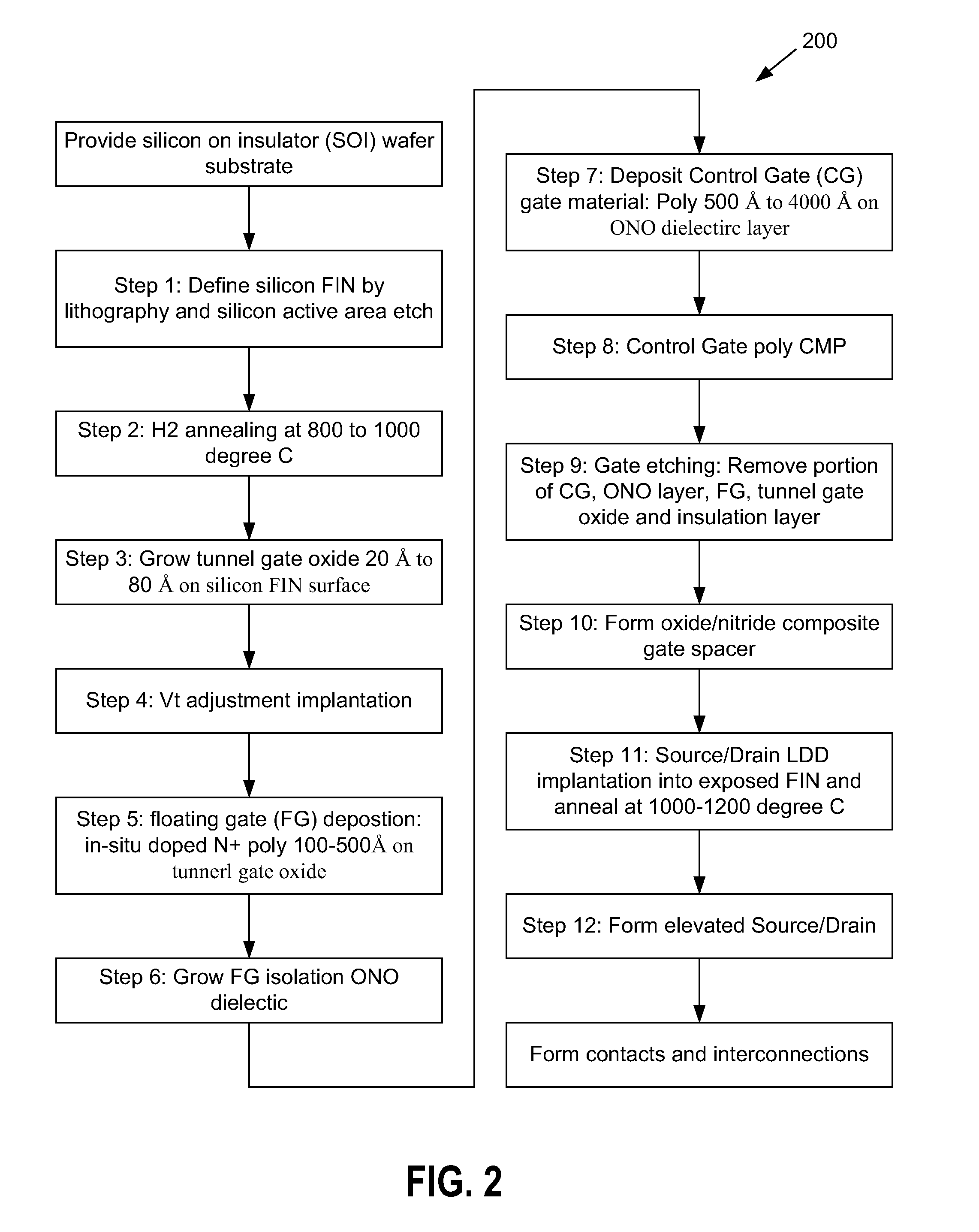

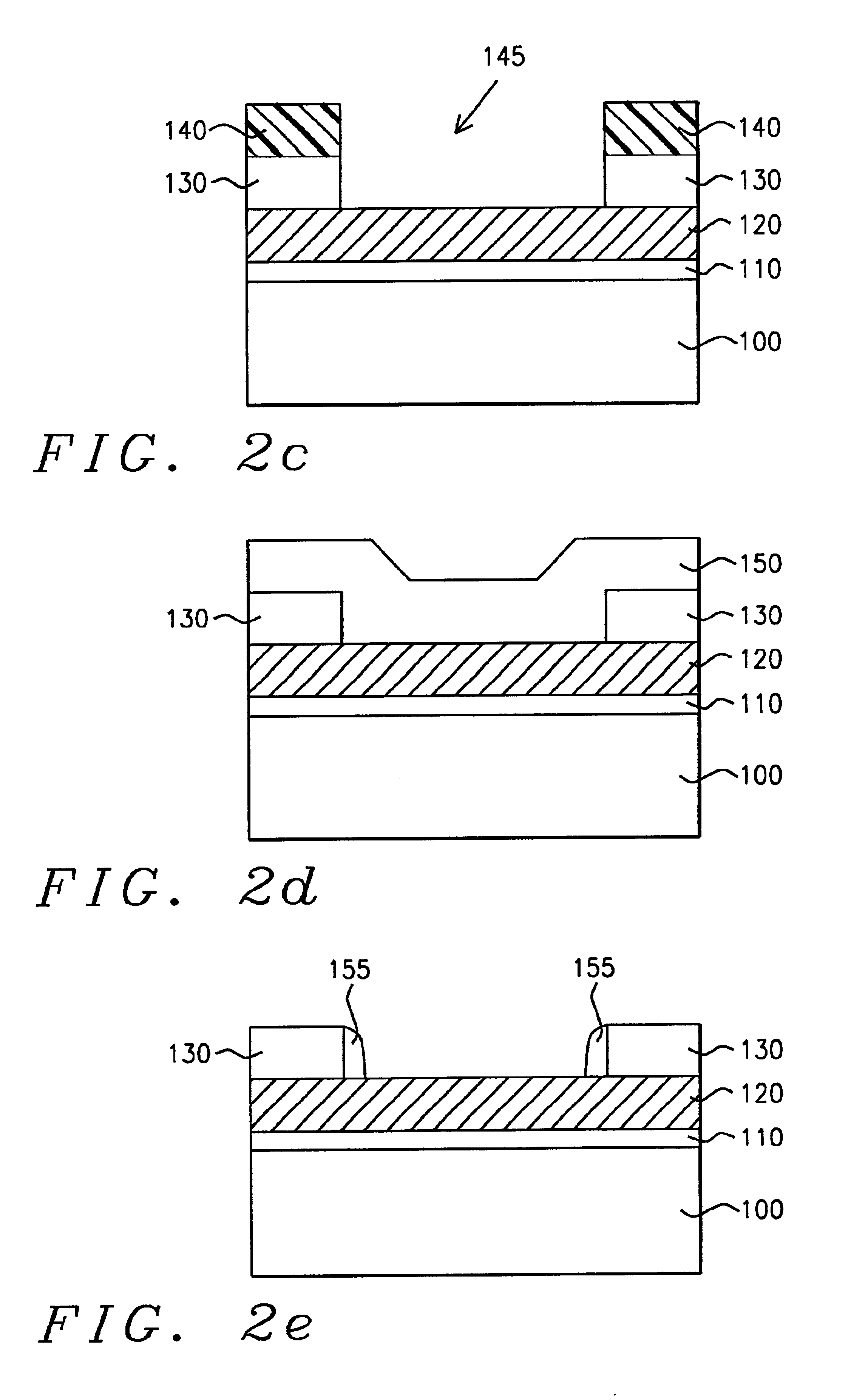

Surrounding stacked gate multi-gate fet structure nonvolatile memory device

ActiveUS20110163369A1Suppression of short channel effectsLower average currentTransistorSolid-state devicesPower flowNitride

Nonvolatile memory devices having a low off state leakage current and an excellent data retention time characteristics. The present invention provides a surrounding stacked gate fin field effect transistor nonvolatile memory structure comprising a silicon-on-insulator substrate of a first conductivity type and a fin active region projecting from an upper surface of the insulator. The structure further includes a tunnel oxide layer formed on the fin active region and a first gate electrode disposed on the tunnel oxide layer and upper surface of the insulator. Additionally, the structure includes an oxide / nitride / oxide (ONO) composite layer formed on the first gate electrode, a second gate electrode formed on the ONO composite layer and patterned so as to define a predetermined area of the ONO composite layer. The structure further includes a dielectric spacer formed on a sidewall of the second gate electrode and source / drain regions formed in the fin active region on both sides of the second gate electrode.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Split gate flash memory cell and manufacturing method thereof

ActiveUS20060234444A1Raise the ratioReliability of the tunneling dielectric layer is thereby increasedSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricEngineering

A split gate flash memory cell includes a substrate having a device isolation structure; a selective gate structure disposed on the substrate; an interlayer dielectric layer having an opening disposed on the substrate, wherein the opening exposes a portion of the selective gate structure, the substrate and the device isolation structure; a floating gate disposed in the opening and extended to cover a surface of the interlayer dielectric layer; a tunneling dielectric layer disposed between the floating gate and the selective gate structure; a gate dielectric layer disposed between the floating gate and the control gate; a source region disposed in the substrate on one side of the control gate that is not adjacent to the selective gate structure, and a drain region disposed in the substrate on one side of the selective gate that is not adjacent to the control gate.

Owner:POWERCHIP SEMICON MFG CORP

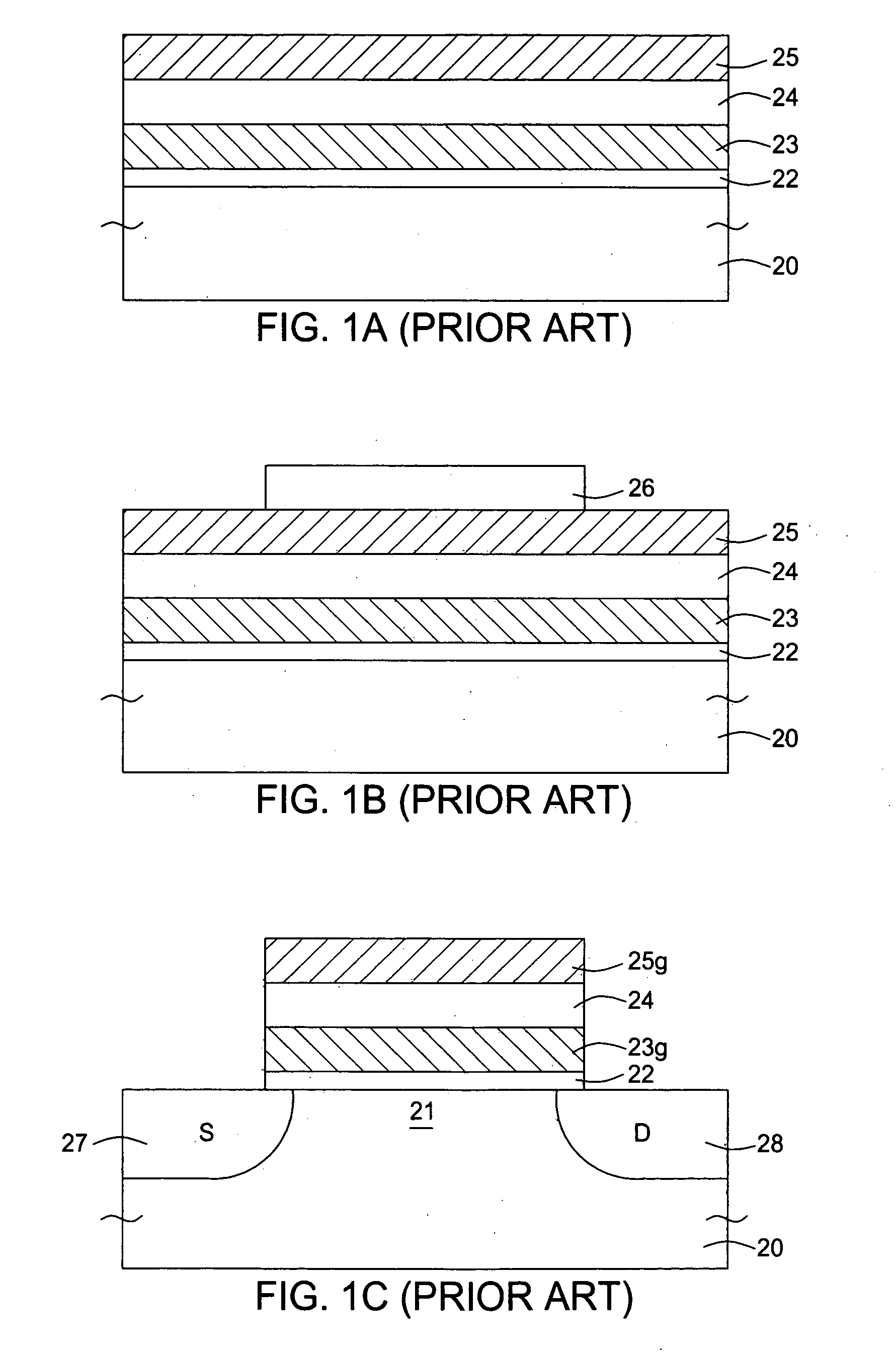

Flash memory cell and fabrication thereof

InactiveUS6906377B2Improve gate coupling ratioIncrease the areaTransistorSolid-state devicesGate dielectricPhysics

A flash memory cell is described, including at least a substrate, a tunnel oxide layer, a floating gate, an insulating layer, a control gate and an inter-gate dielectric layer. The tunnel oxide layer is disposed on the substrate. The floating gate is disposed on the tunnel oxide layer, and is constituted by a first conductive layer on the tunnel oxide layer and a second conductive layer on the first conductive layer. The second conductive layer has a bottom lower than the top surface of the first conductive layer, and has a bowl-like cross section. The insulating layer is disposed between the floating gates, and each control gate is disposed on a floating gate with an inter-gate dielectric layer between them.

Owner:WINBOND ELECTRONICS CORP

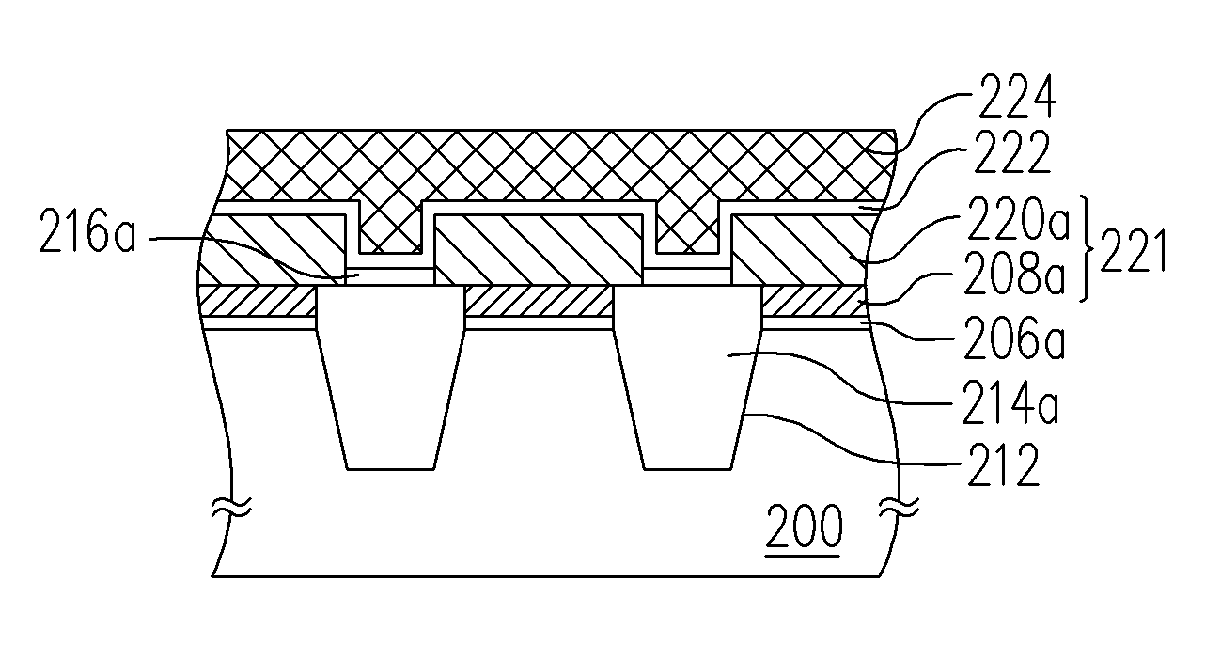

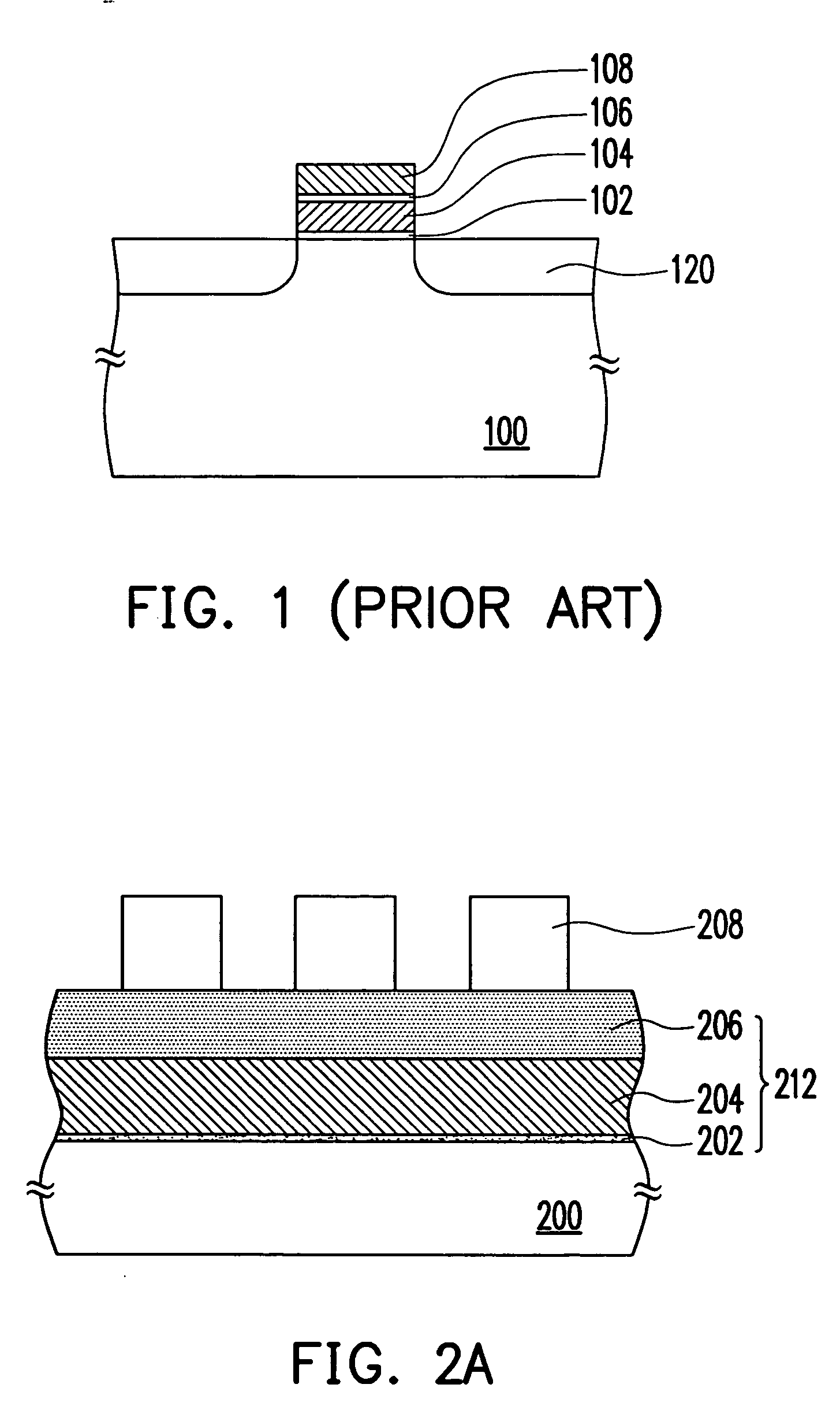

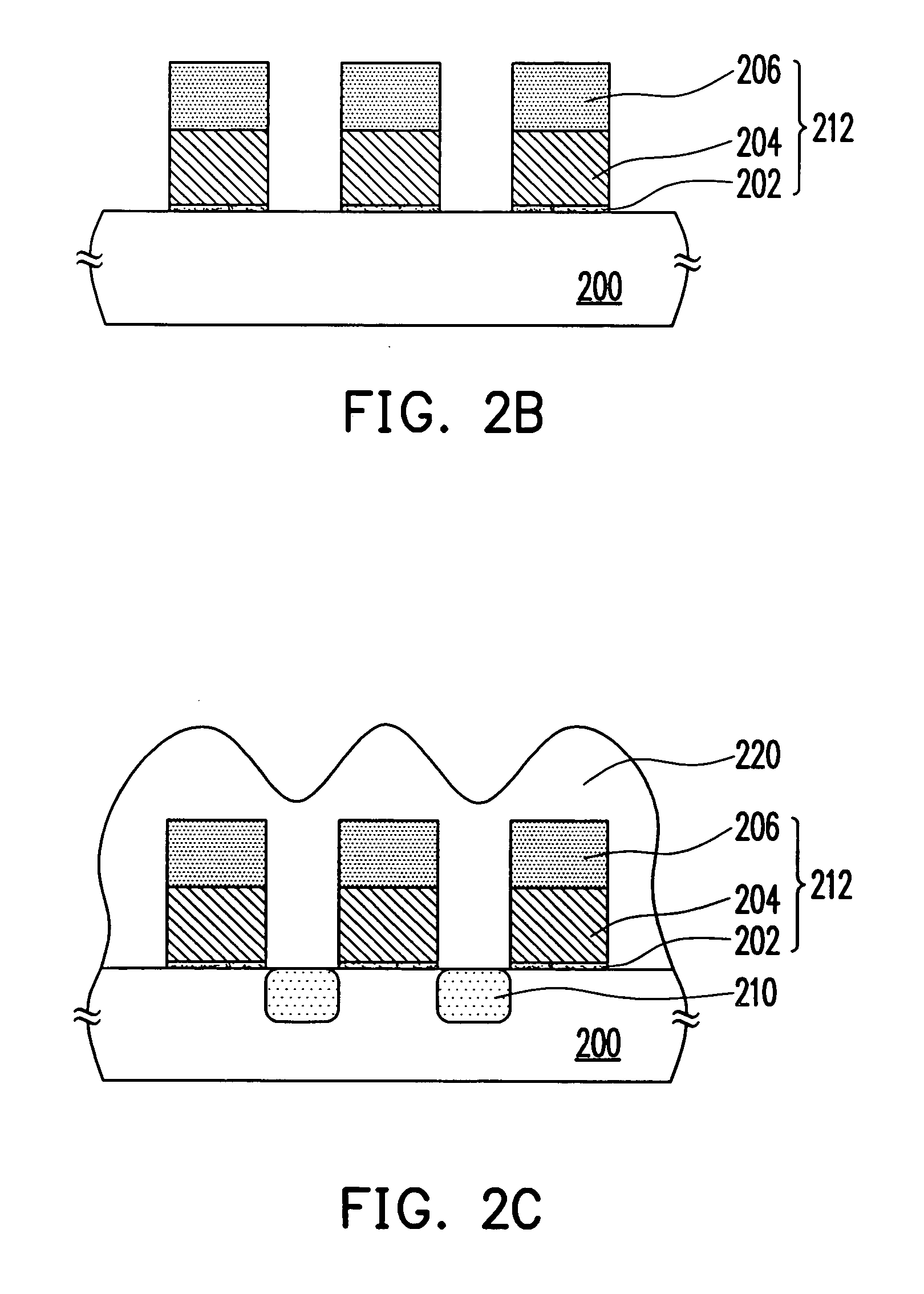

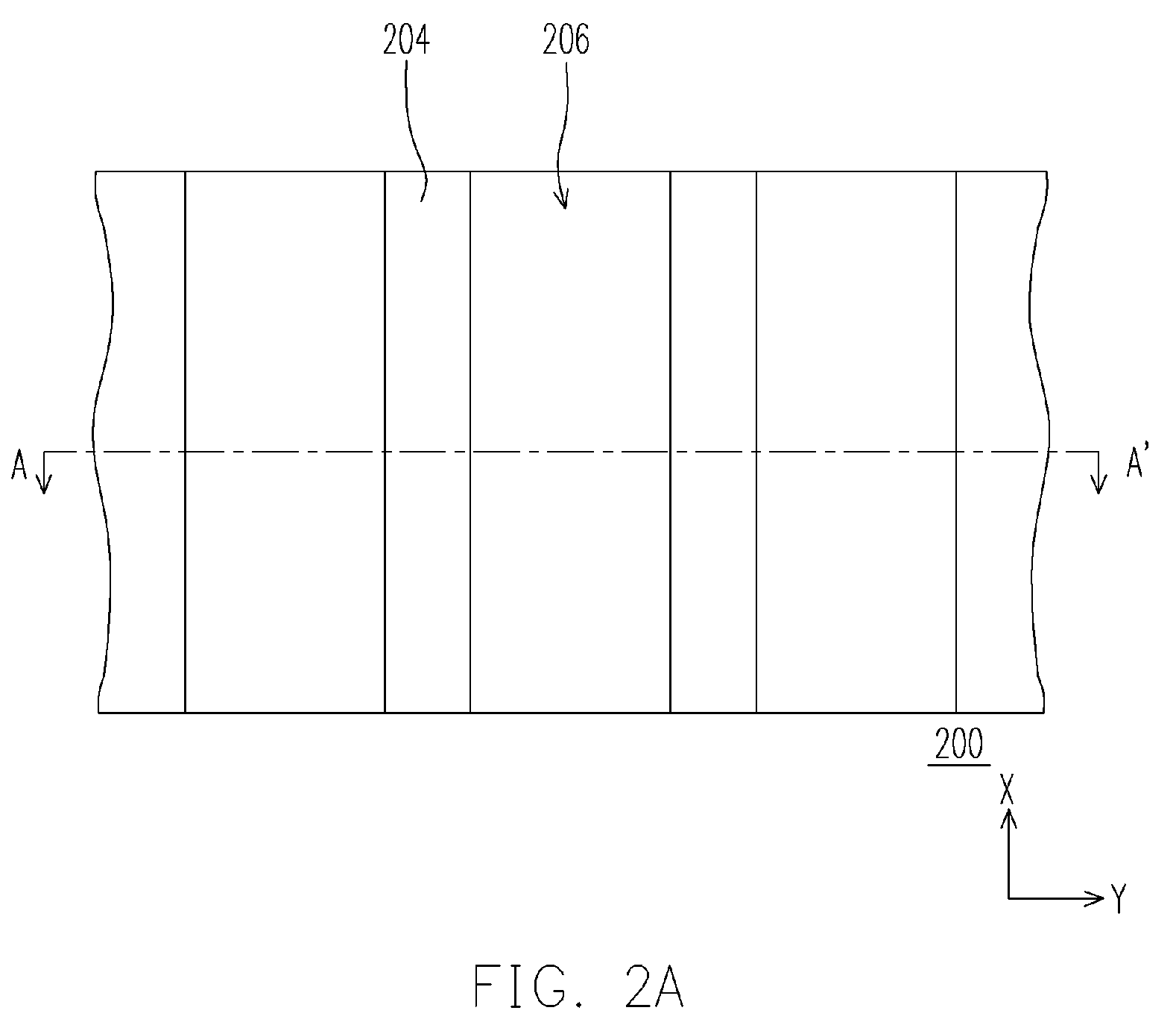

Method of fabricating a flash memory

ActiveUS6893918B1Improve gate coupling ratioImprove device performanceSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricEngineering

A method of fabricating a flash memory is provided. A substrate having several device isolation structures for defining an active region is provided. A tunneling dielectric layer and a patterned mask layer are sequentially formed over the active region of the substrate. A sacrificial layer is formed on the substrates. Thereafter, the sacrificial layer is patterned to retain a part of sacrificial layer on the device isolation structures. The patterned mask layer is removed, and a conductive layer that exposed the top section of the sacrificial layers is formed over the substrate. After removing the sacrificial layer, an inter-gate dielectric layer is formed over the substrate. A control gate is formed over the inter-gate dielectric layer. Finally, a source region and a drain region are formed in the substrate on each side of the control gate.

Owner:POWERCHIP SEMICON MFG CORP

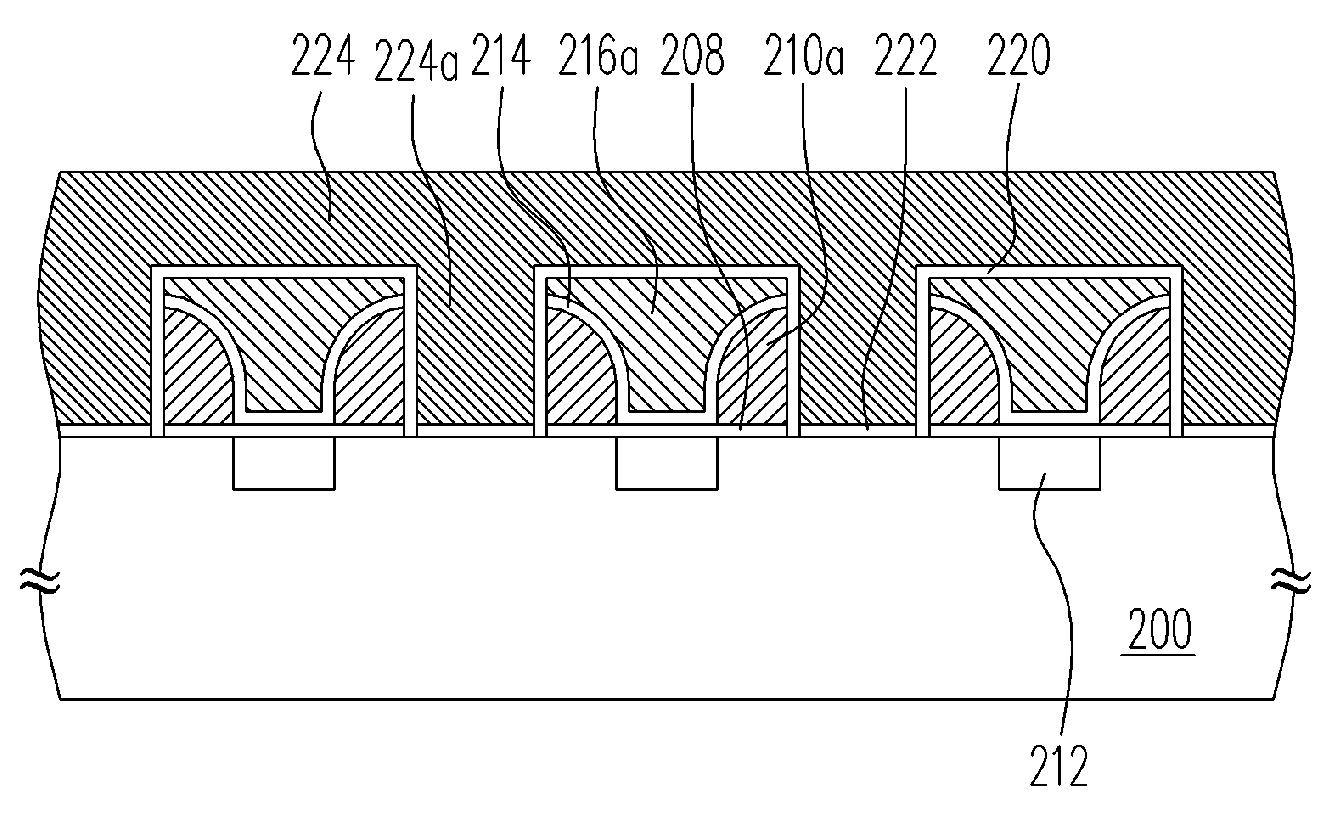

Flash memory device and manufacturing method thereof

InactiveUS20060131635A1Simplify the manufacturing processImprove gate coupling ratioTransistorSolid-state devicesInter layerCoupling ratio

A method of manufacturing a flash memory device is provided. Multiple stack structures each comprising a tunneling oxide layer and a first conductive layer are formed over a substrate. Thereafter, multiple embedded doping regions is formed in the substrate between the stack structures. A dielectric layer is formed over the substrate to cover the stack structures and then the dielectric layer is etched back and a portion of dielectric layer is remained on the stack structures. Using a portion of the remaining dielectric layer as a mask, a portion of the first conductive layer is removed. An inter-layer dielectric layer and a second conductive layer are sequentially formed over the first conductive layer. Because a self-aligned process is used to define the floating gate and the floating gate has a narrow-top / wide-bottom configuration, the fabrication process is simplified and the coupling ratio of the stack gate is increased.

Owner:MACRONIX INT CO LTD

Method of fabricating flash memory

InactiveUS20060102948A1Simplifies fabricationGate couple ratio be increaseTransistorSolid-state devicesElectrical and Electronics engineeringMask layer

A method of fabricating a flash memory is provided. The method includes forming a mask layer with first openings on the substrate. A tunneling dielectric layer is formed at bottom in the first openings. Strips of conductive spacers are formed on sidewalls of the first openings, and source / drain regions are formed in the substrate within the first openings. The strips of conductive spacers are patterned to form floating gates. A first inter-gate dielectric layer is formed over the substrate. Control gates are formed on the substrate to fill the first openings. Mask layer is removed to form second openings. Gate dielectric layer is formed at bottom of second openings, and second inter-gate dielectric layer is formed on the sidewalls of floating gates, and the sidewalls and top surface of the control gates. Word lines are formed to fill second openings disposed between the floating gates and cover the control gates.

Owner:POWERCHIP SEMICON CORP

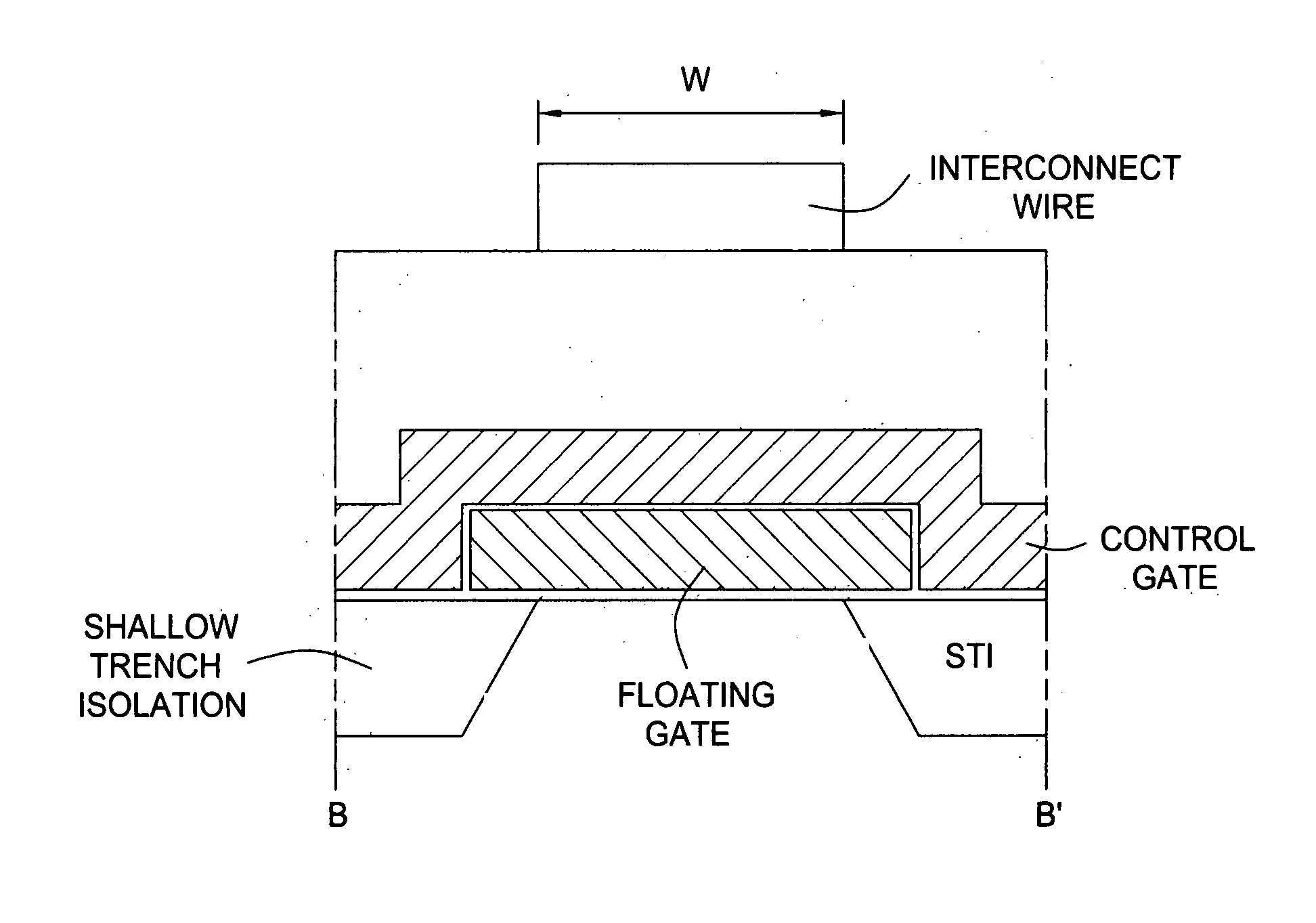

Method and structure to improve the gate coupling ratio (GCR) for manufacturing a flash memory device

InactiveUS6897116B2Increase the overlapping areaImprove gate coupling ratioSolid-state devicesSemiconductor/solid-state device manufacturingElectrical conductorCoupling ratio

Method and structure to improve the gate coupling ratio (GCR) for manufacturing a flash memory device are provided. The method and structure include the following steps. A gate oxide layer, a first semiconductor layer, and an insulating layer are formed sequentially over a provided semiconductor substrate. An etching process is used to etch the insulating layer. A semiconductor spacer is then deposited and used as a self-aligned etching mask. After the self-aligned etching, the insulating layer is removed and an insulating stacked structure is deposited. Finally, a second semiconductor layer is deposited and etched to form the control gate region.

Owner:UNITED MICROELECTRONICS CORP

Split gate non-volatile memory devices and methods of forming same

InactiveUS20060199336A1Improve gate coupling ratioImprove efficiencySolid-state devicesRead-only memoriesCoupling ratioEngineering

Non-volatile memory devices and methods for fabricating non-volatile memory devices are disclosed. More specifically, split gate memory devices are provided having frameworks that provide increased floating gate coupling ratios, thereby enabling enhanced programming and erasing efficiency and performance.

Owner:SAMSUNG ELECTRONICS CO LTD

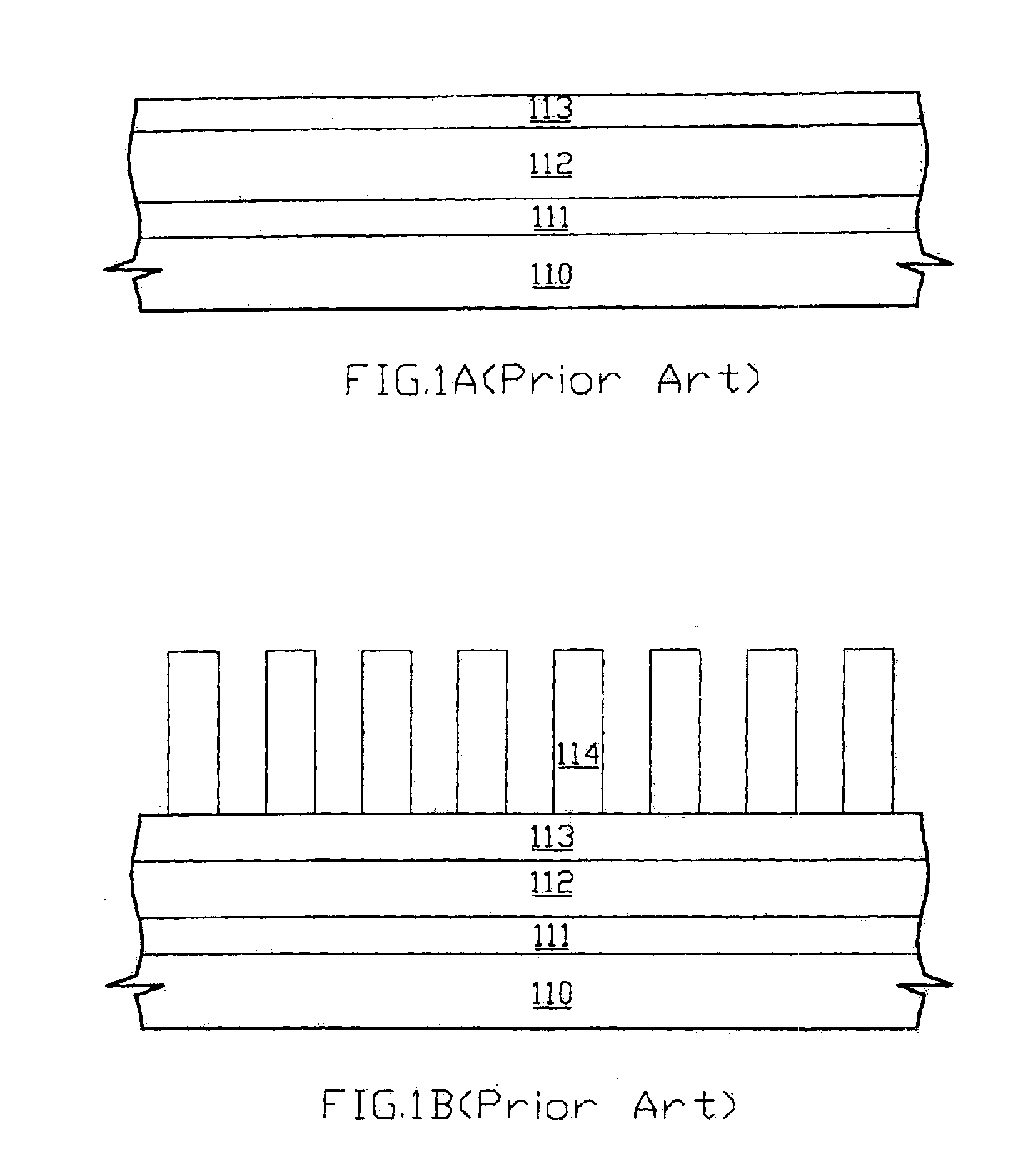

Step-shaped floating poly-si gate to improve a gate coupling ratio for flash memory application

InactiveUS6838725B2Increase the overlapping areaAccelerated programTransistorSemiconductor/solid-state device manufacturingDielectricCoupling ratio

A stacked-gate flash memory cell is provided having step-shaped poly-gates with increased overlap area between them in order to increase the coupling ratio and hence the program speed of the cell. The floating gate is first formed with a step and the intergate dielectric is conformally shaped thereon followed by the forming of the control gate thereon. The increase in the-overlap area can be achieved by forming gates with multiply connected surfaces of different shapes.

Owner:TAIWAN SEMICON MFG CO LTD

Method and structure to improve the gate coupling ratio (GCR) for manufacturing a flash memory device

InactiveUS20050056879A1Increase the overlapping areaImprove gate coupling ratioSolid-state devicesSemiconductor/solid-state device manufacturingElectrical conductorCoupling ratio

Method and structure to improve the gate coupling ratio (GCR) for manufacturing a flash memory device are provided. The method and structure include the following steps. A gate oxide layer, a first semiconductor layer, and an insulating layer are formed sequentially over a provided semiconductor substrate. An etching process is used to etch the insulating layer. A semiconductor spacer is then deposited and used as a self-aligned etching mask. After the self-aligned etching, the insulating layer is removed and an insulating stacked structure is deposited. Finally, a second semiconductor layer is deposited and etched to form the control gate region.

Owner:UNITED MICROELECTRONICS CORP

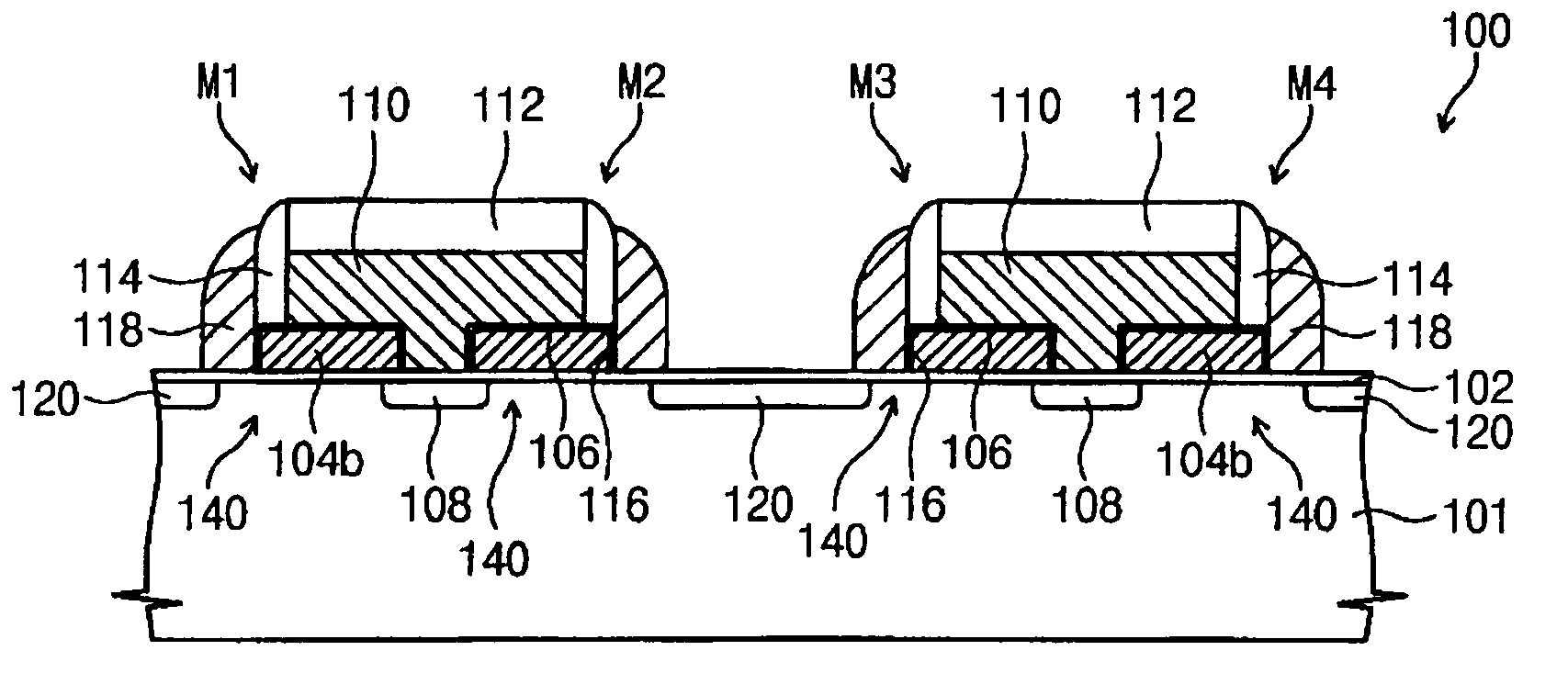

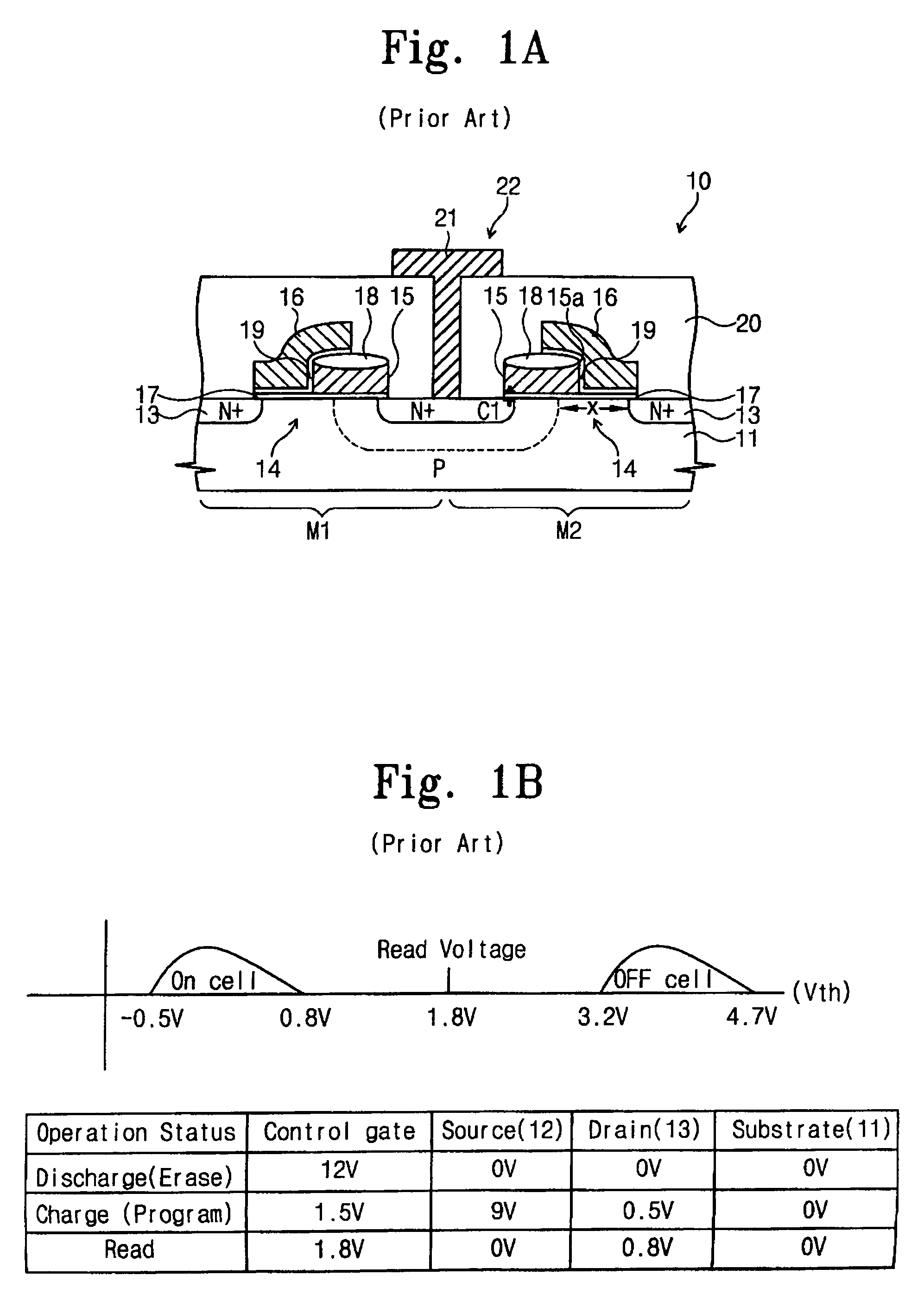

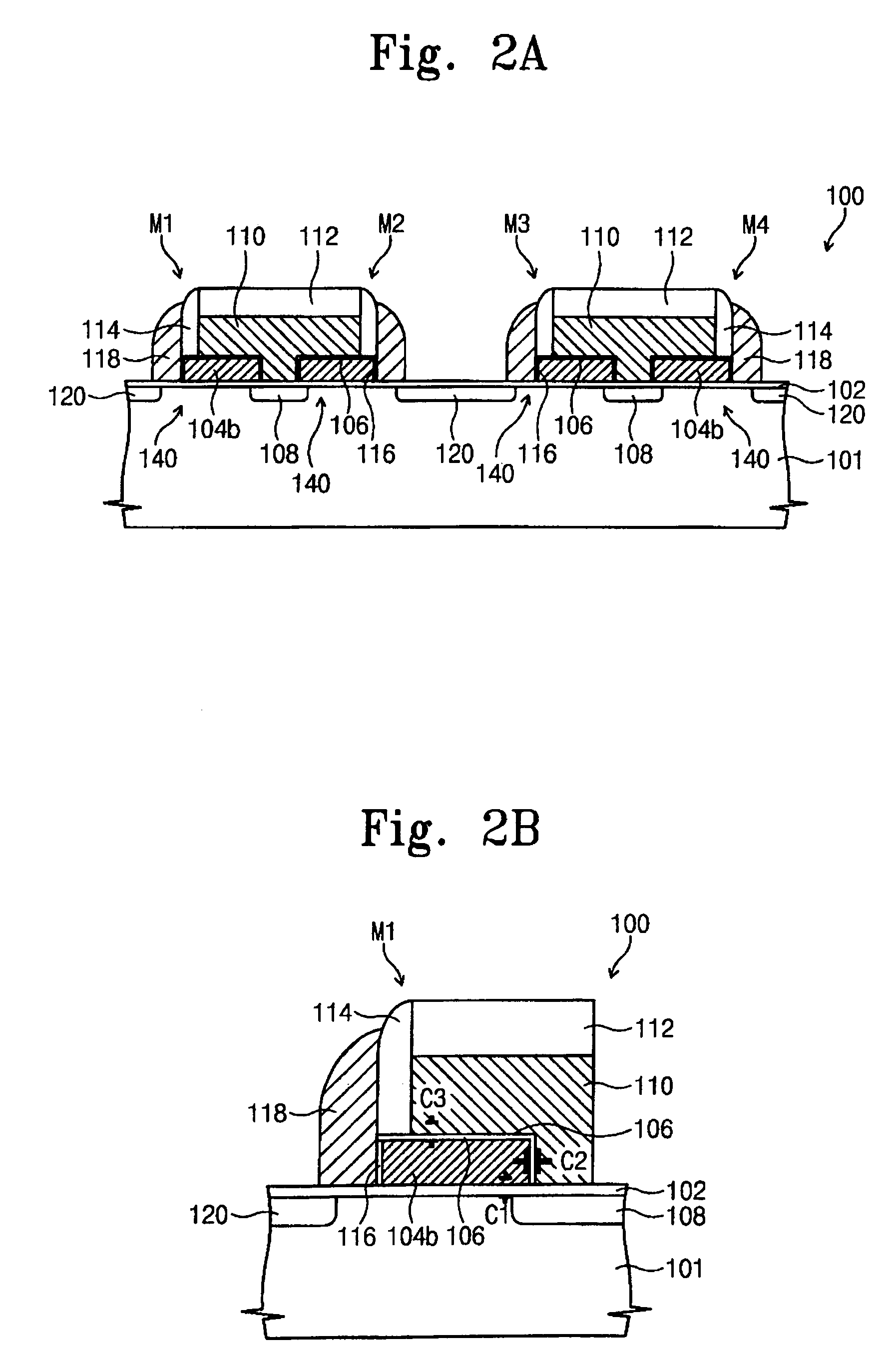

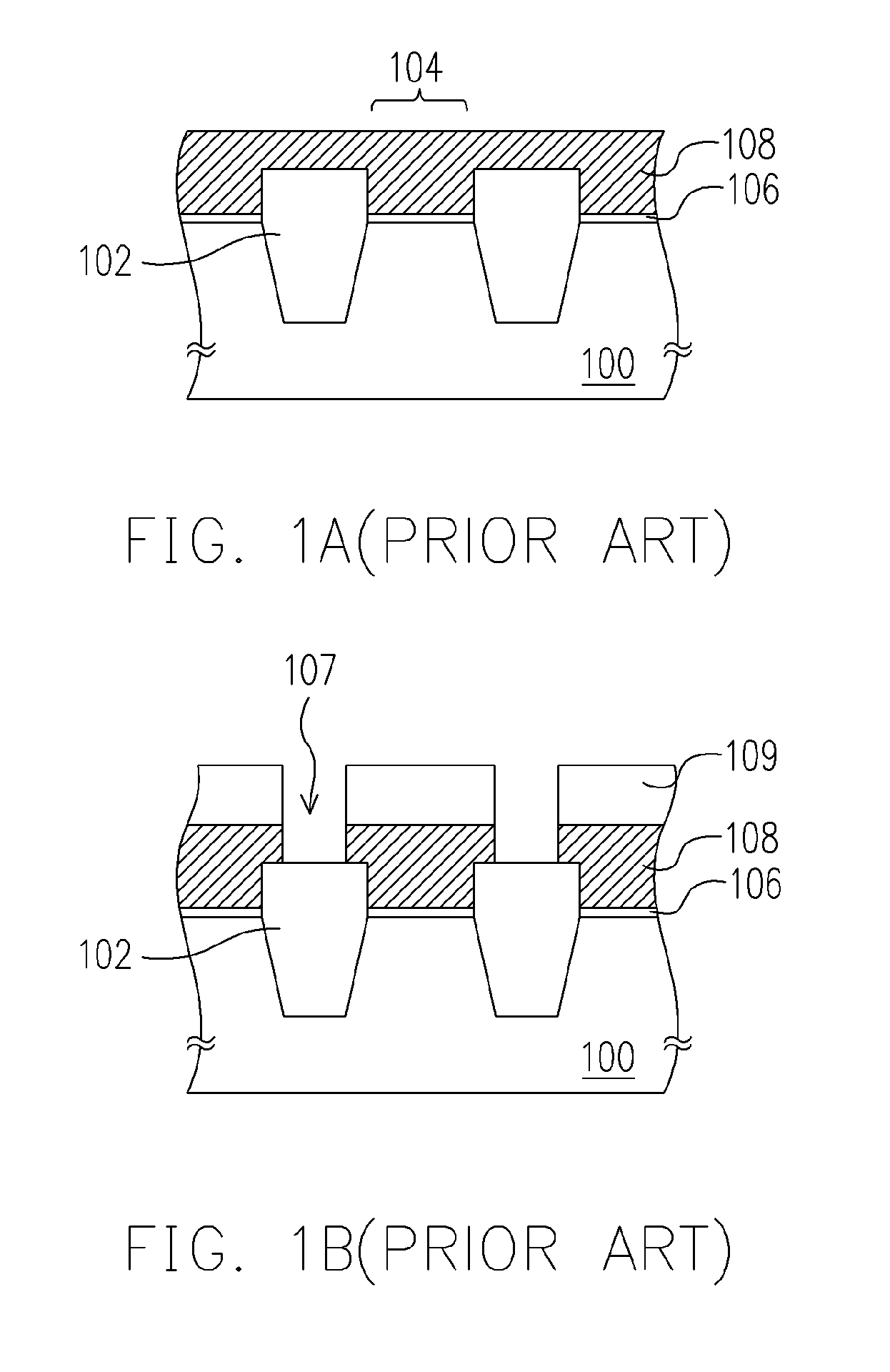

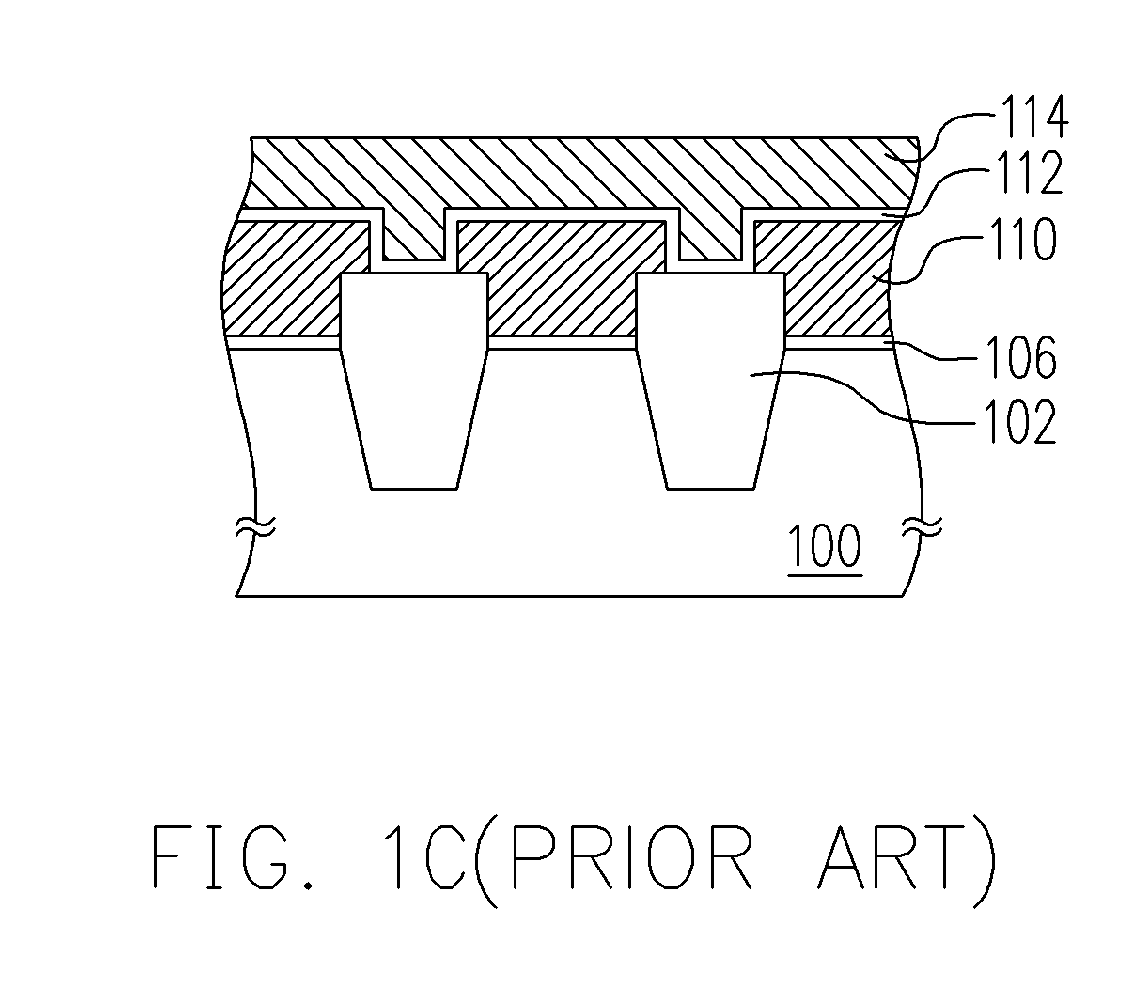

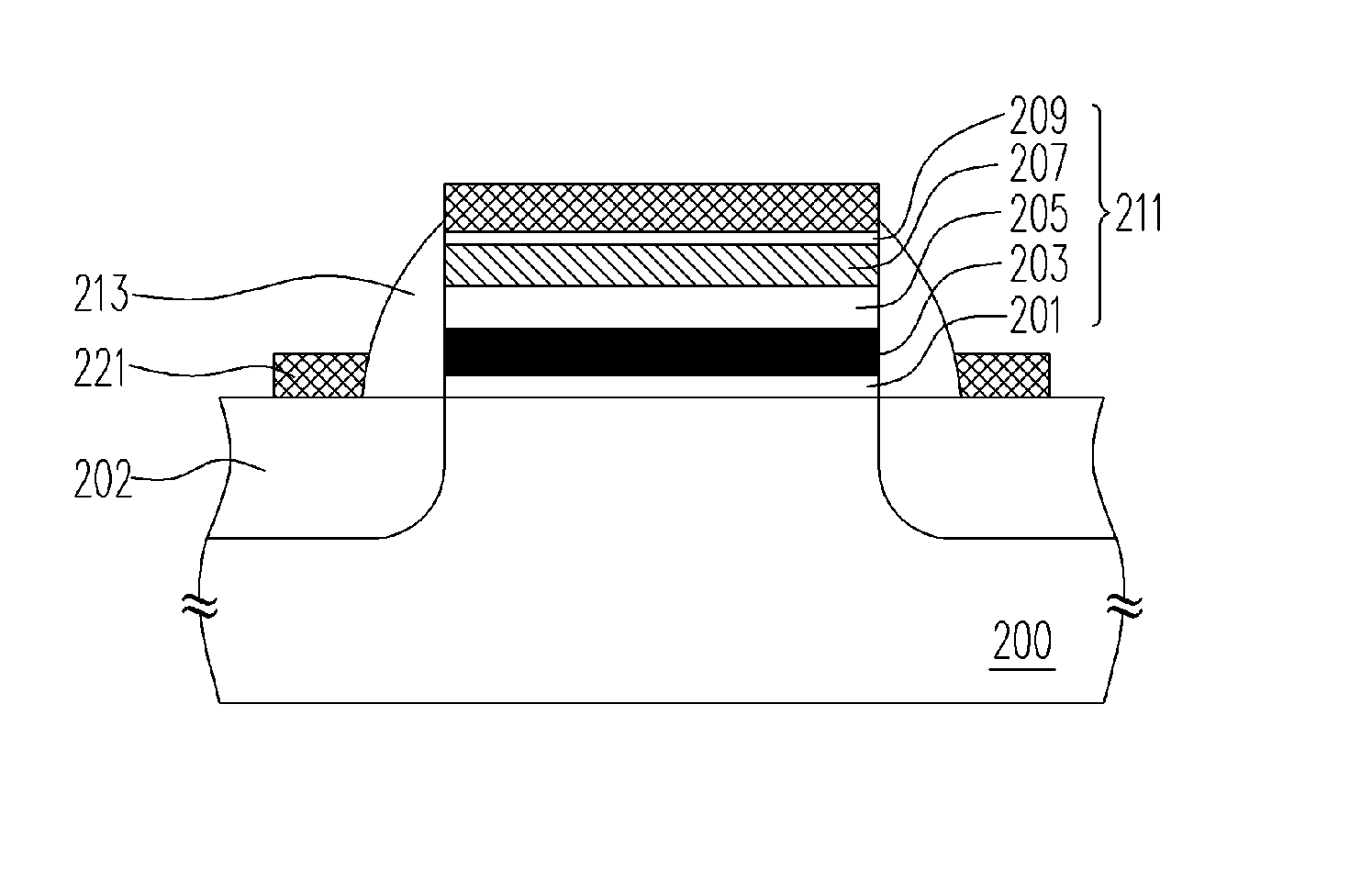

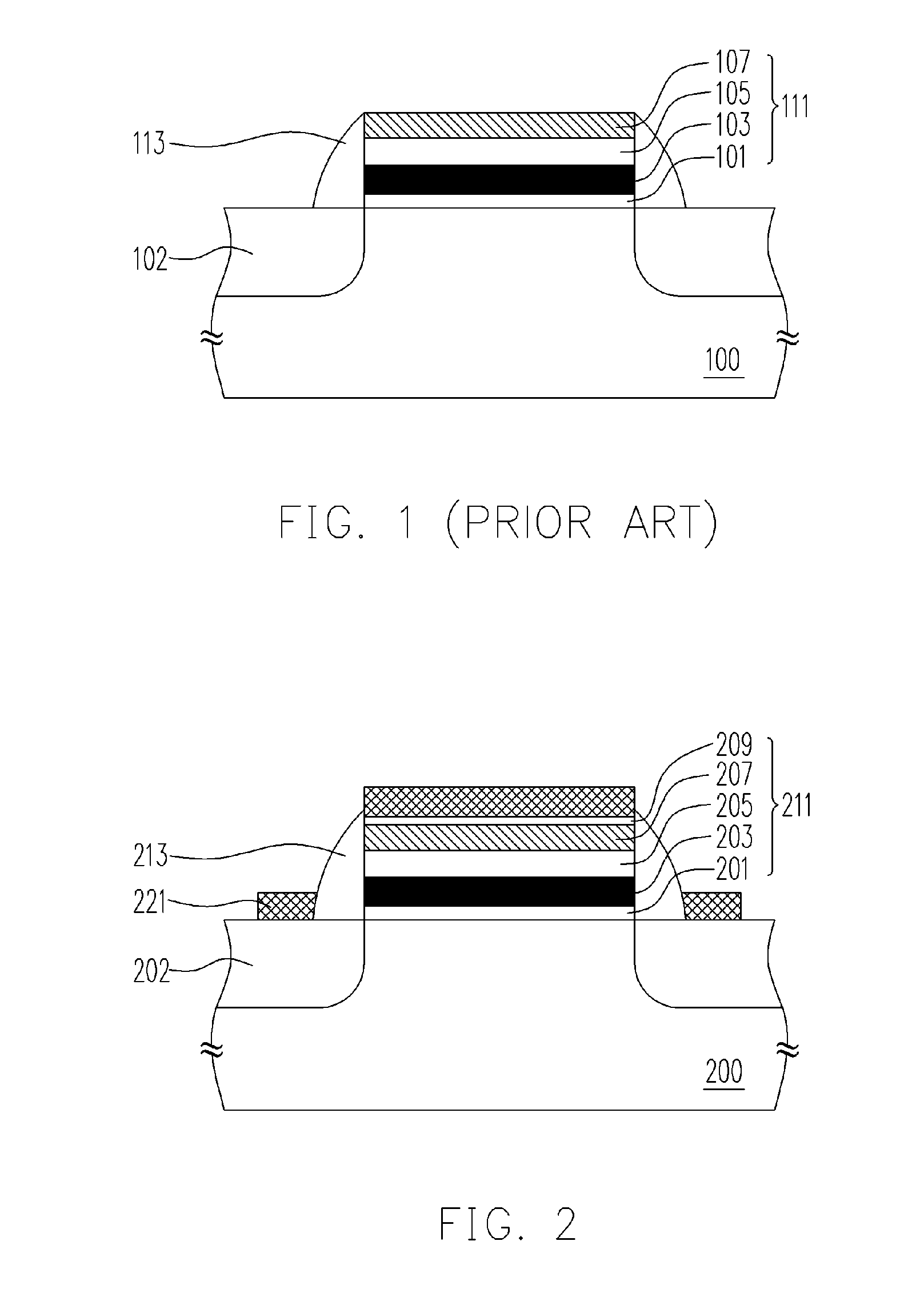

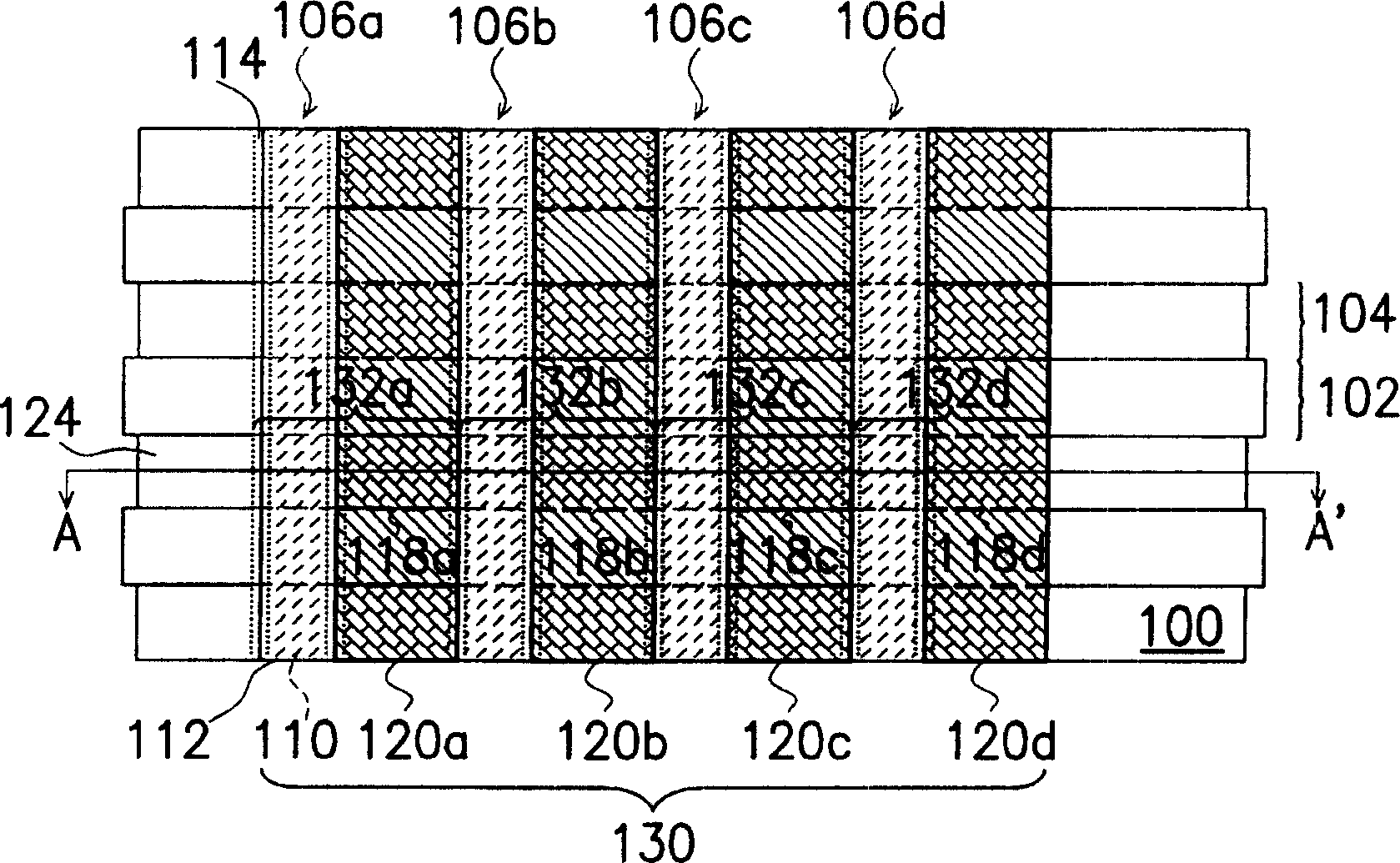

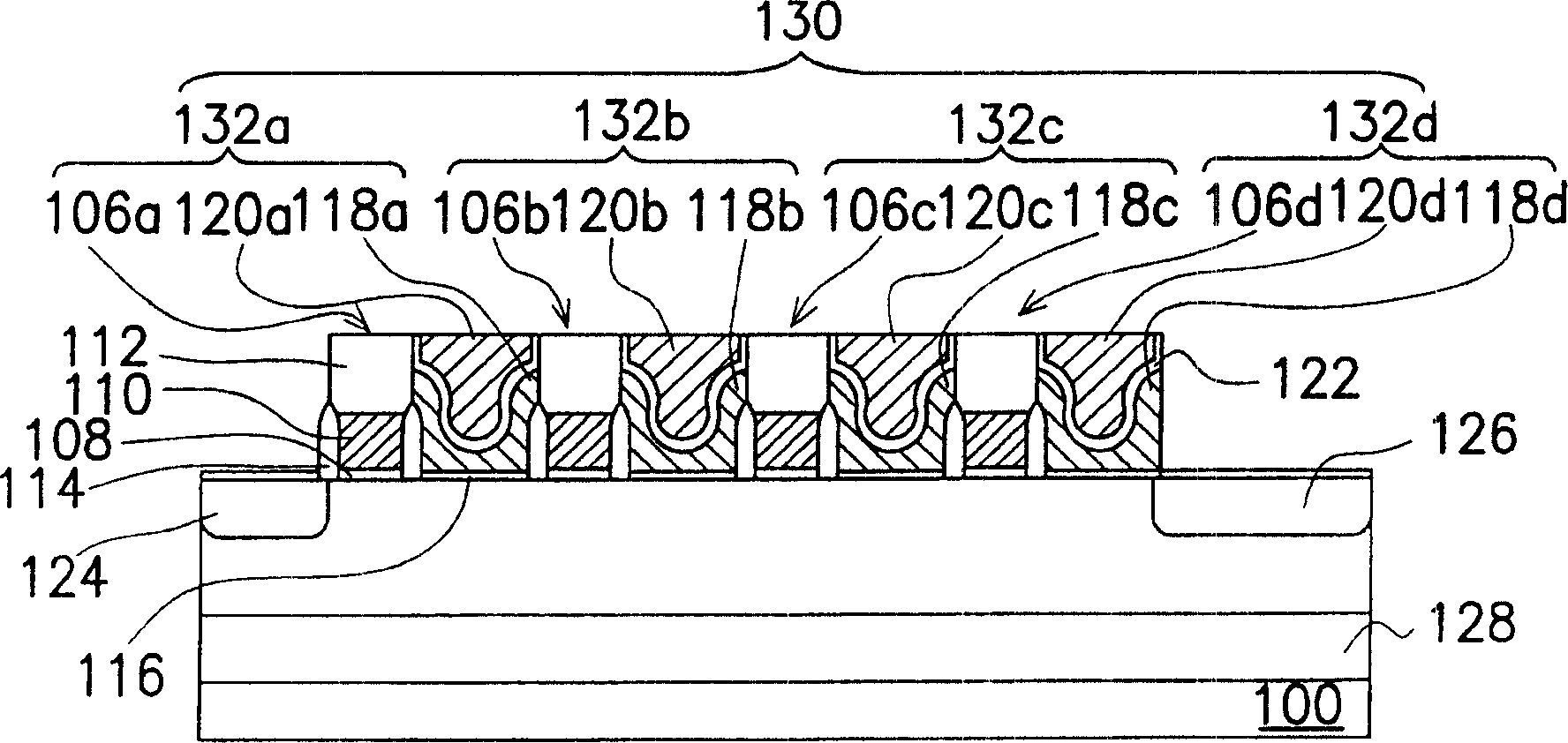

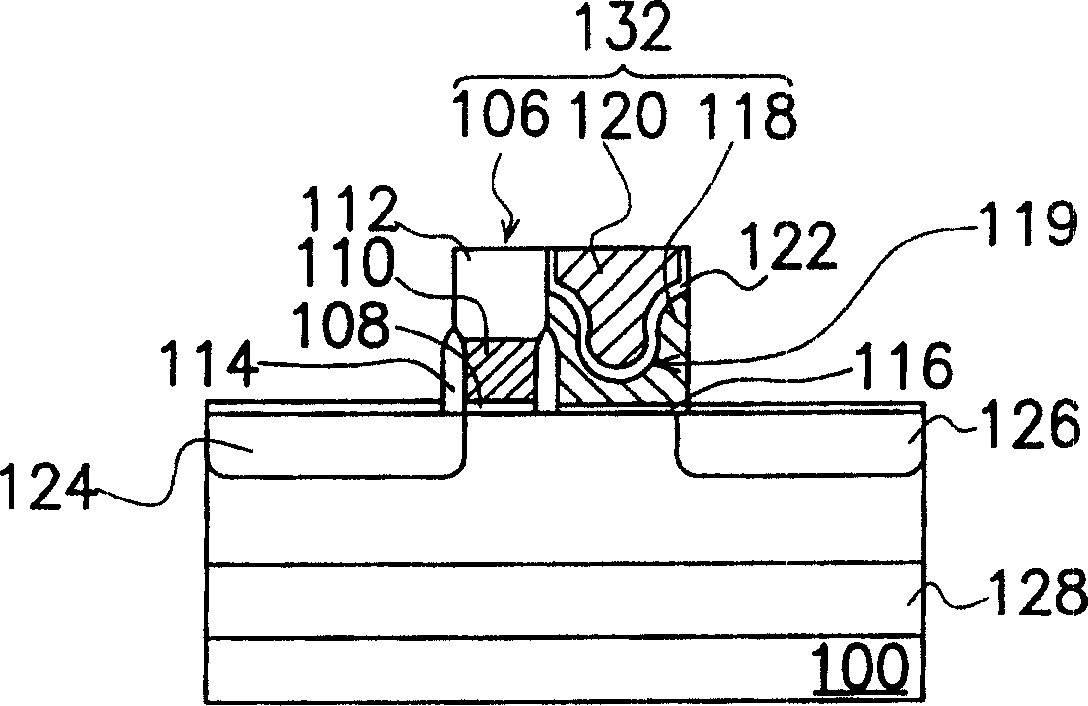

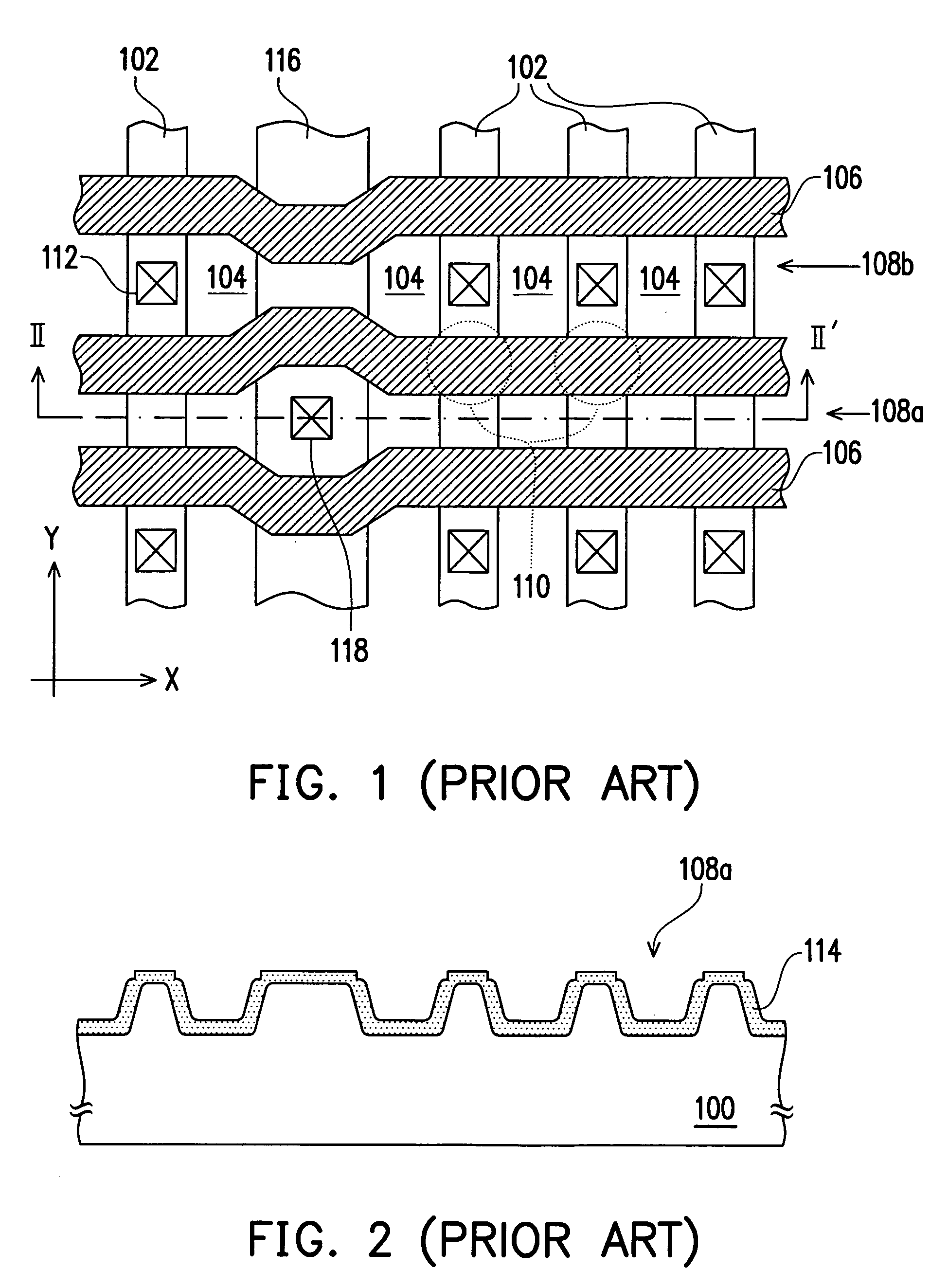

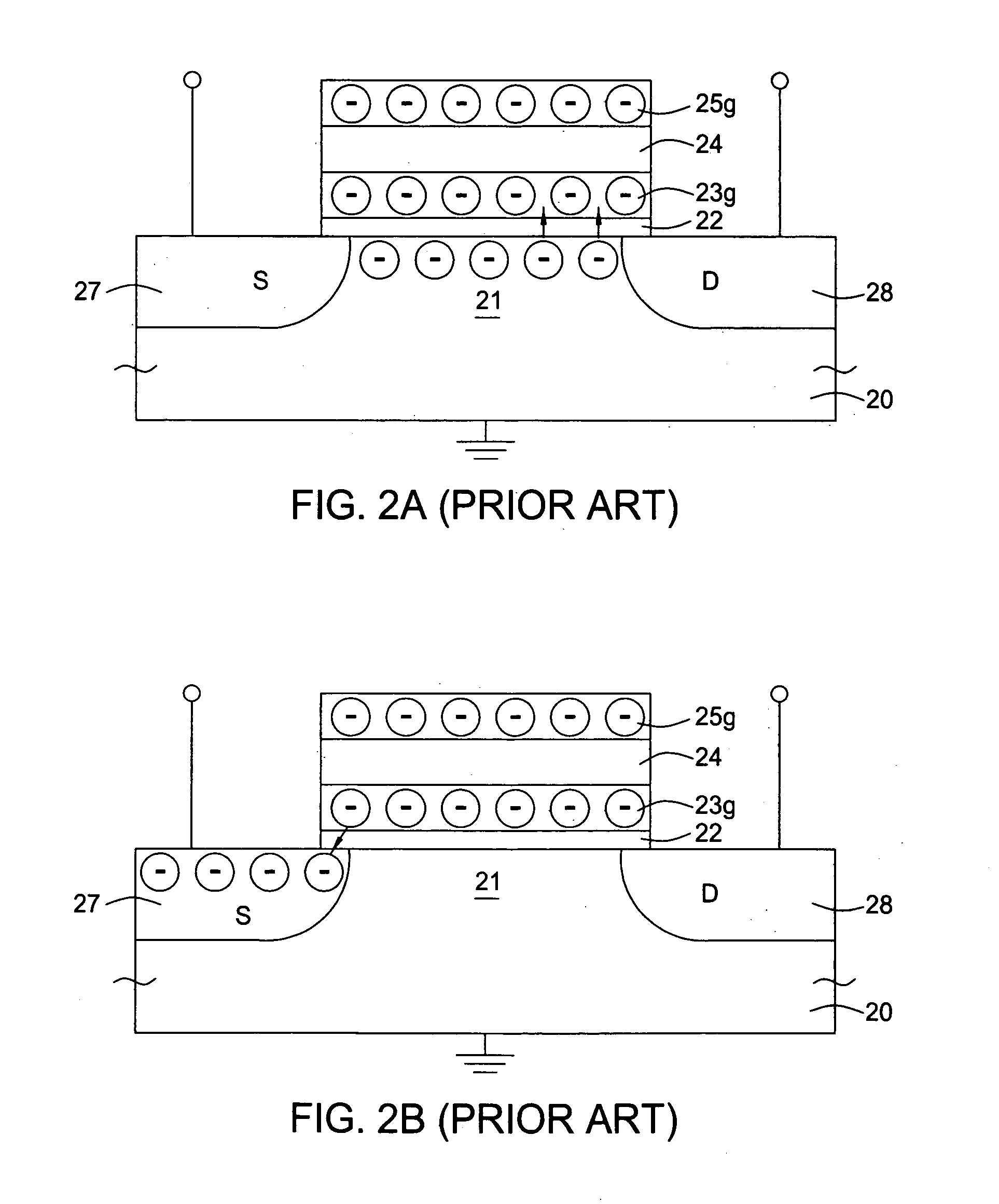

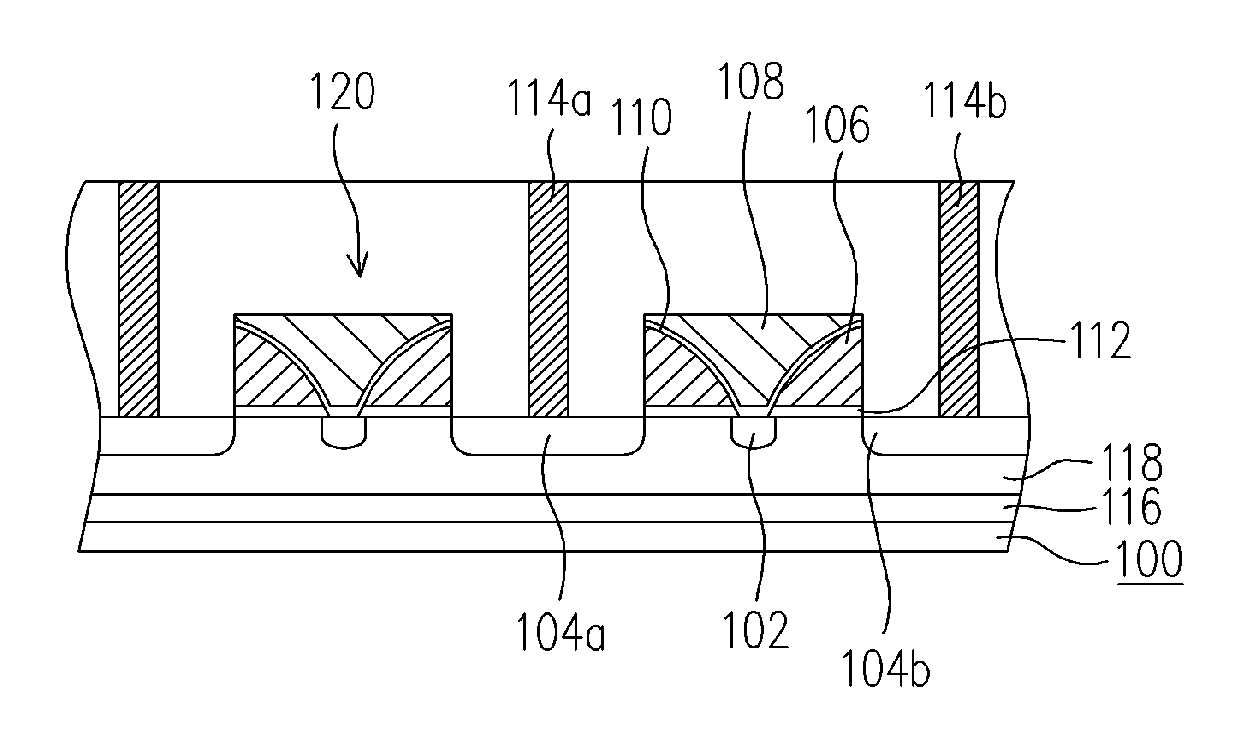

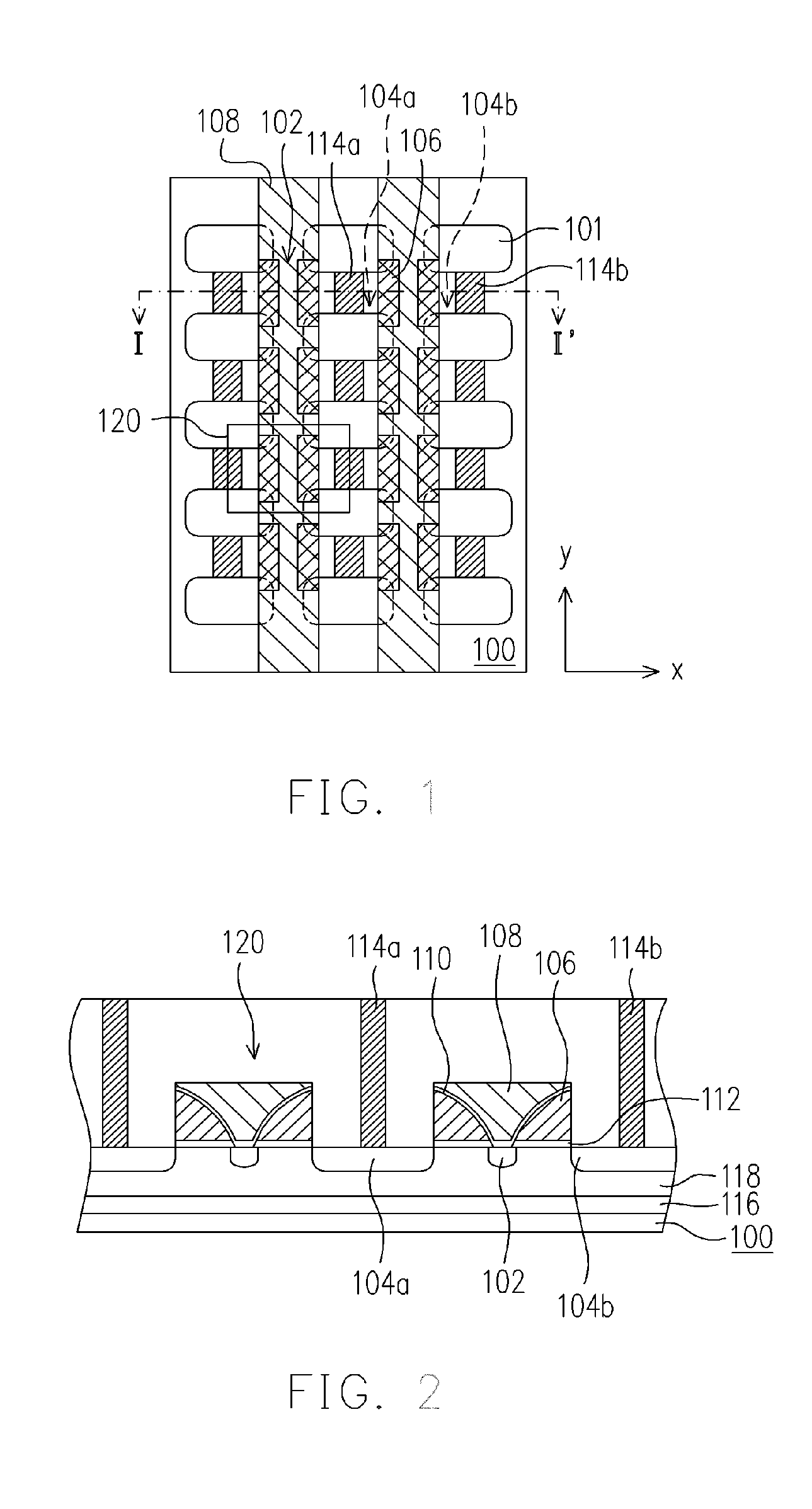

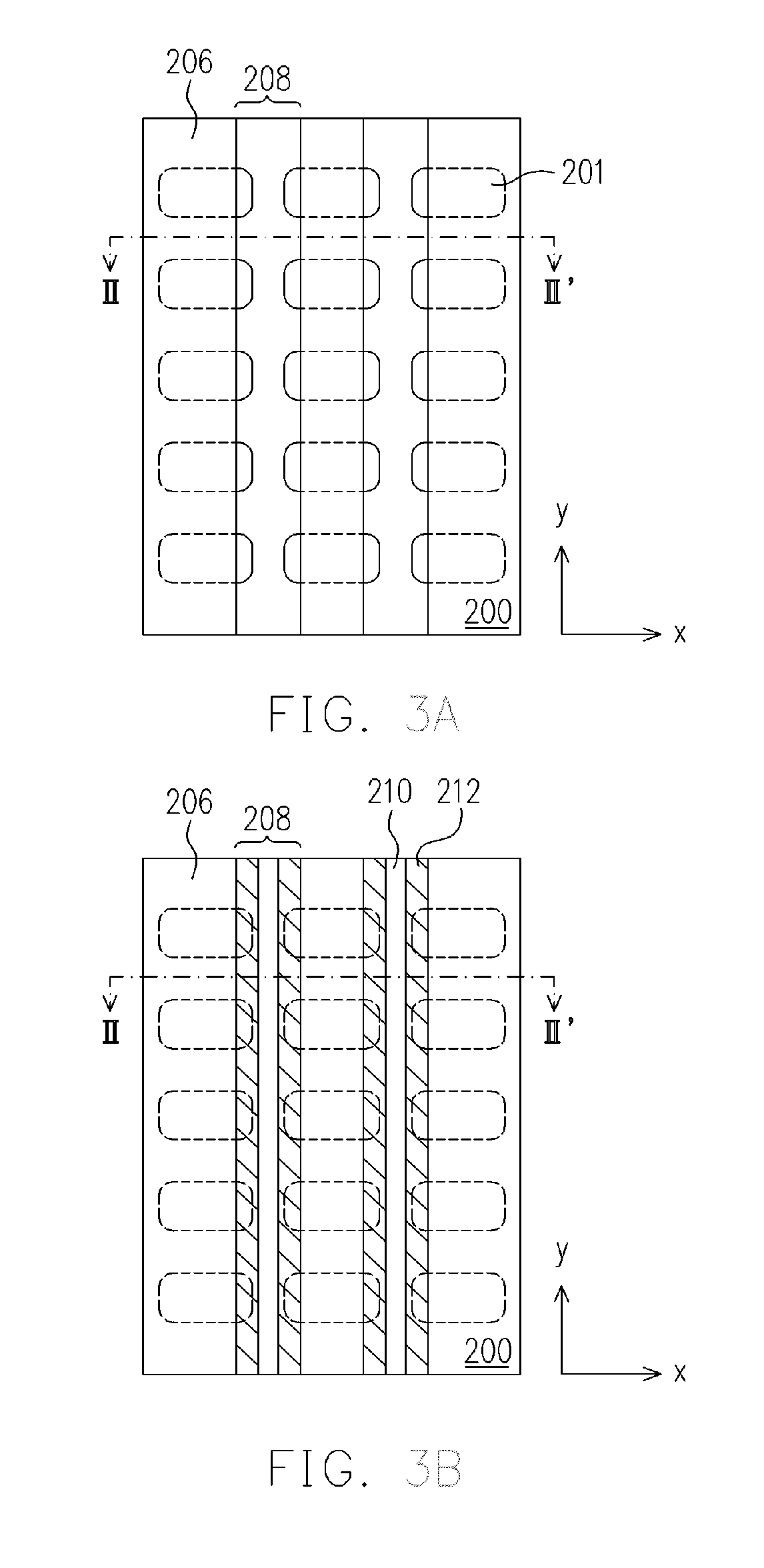

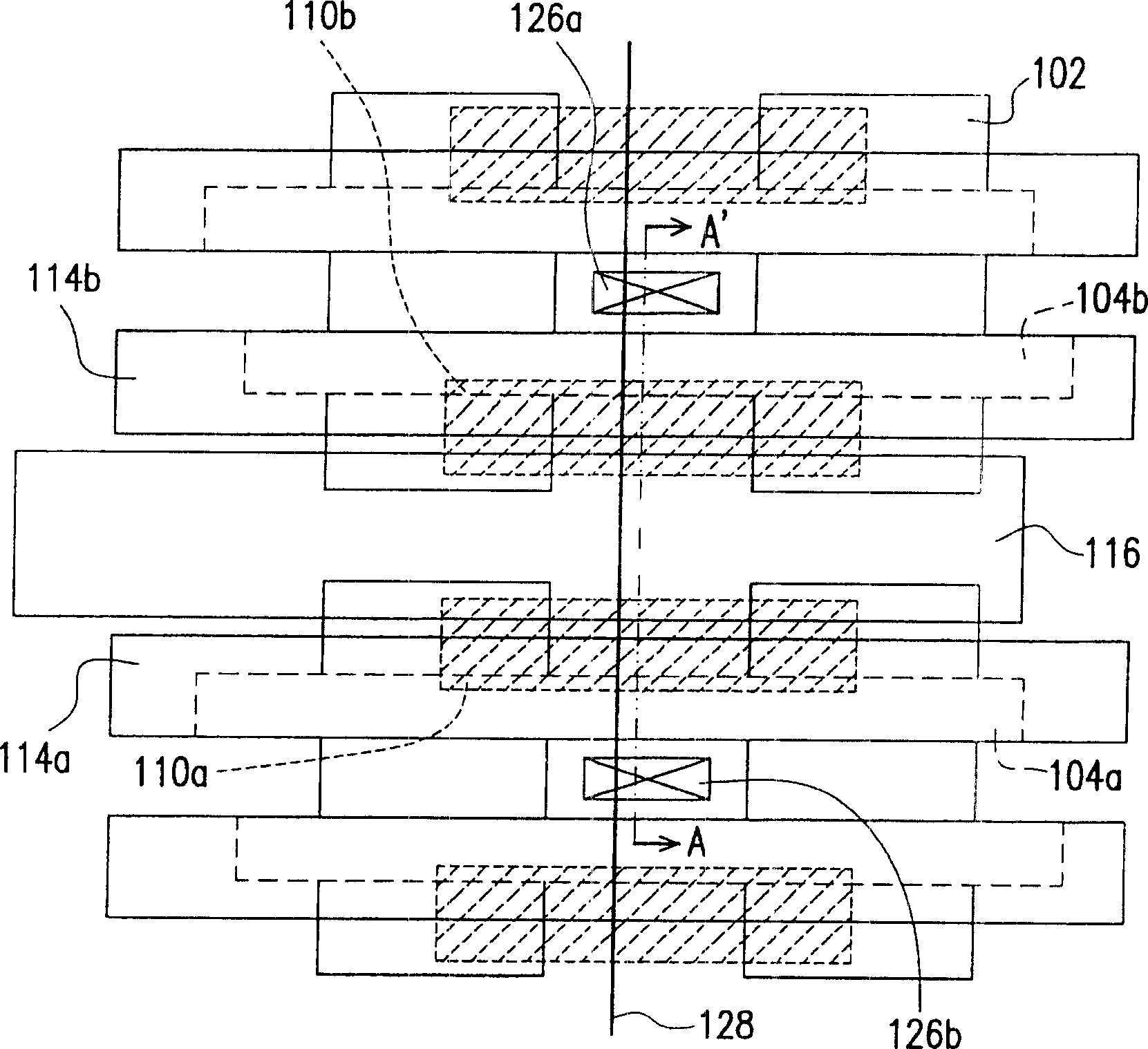

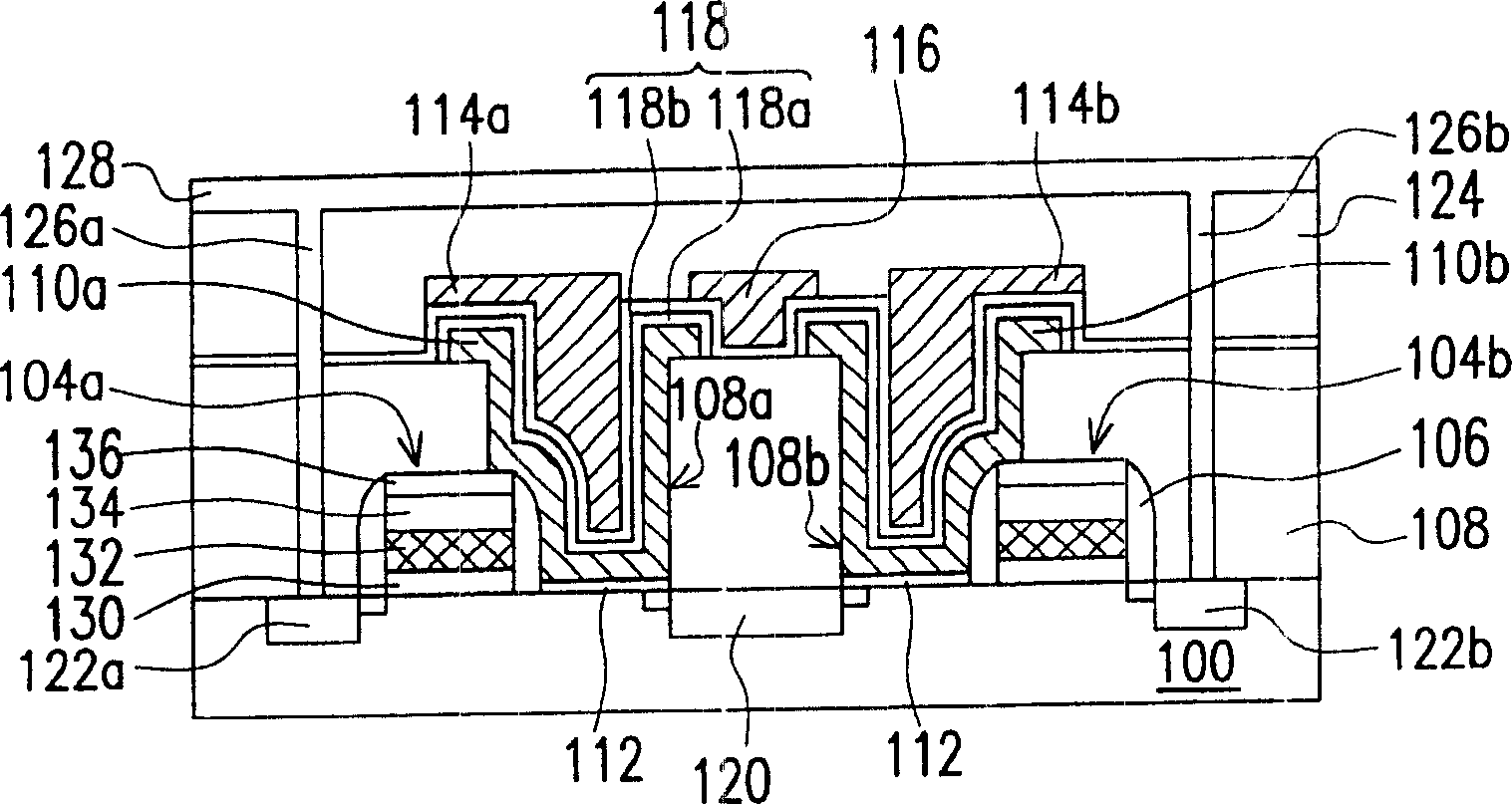

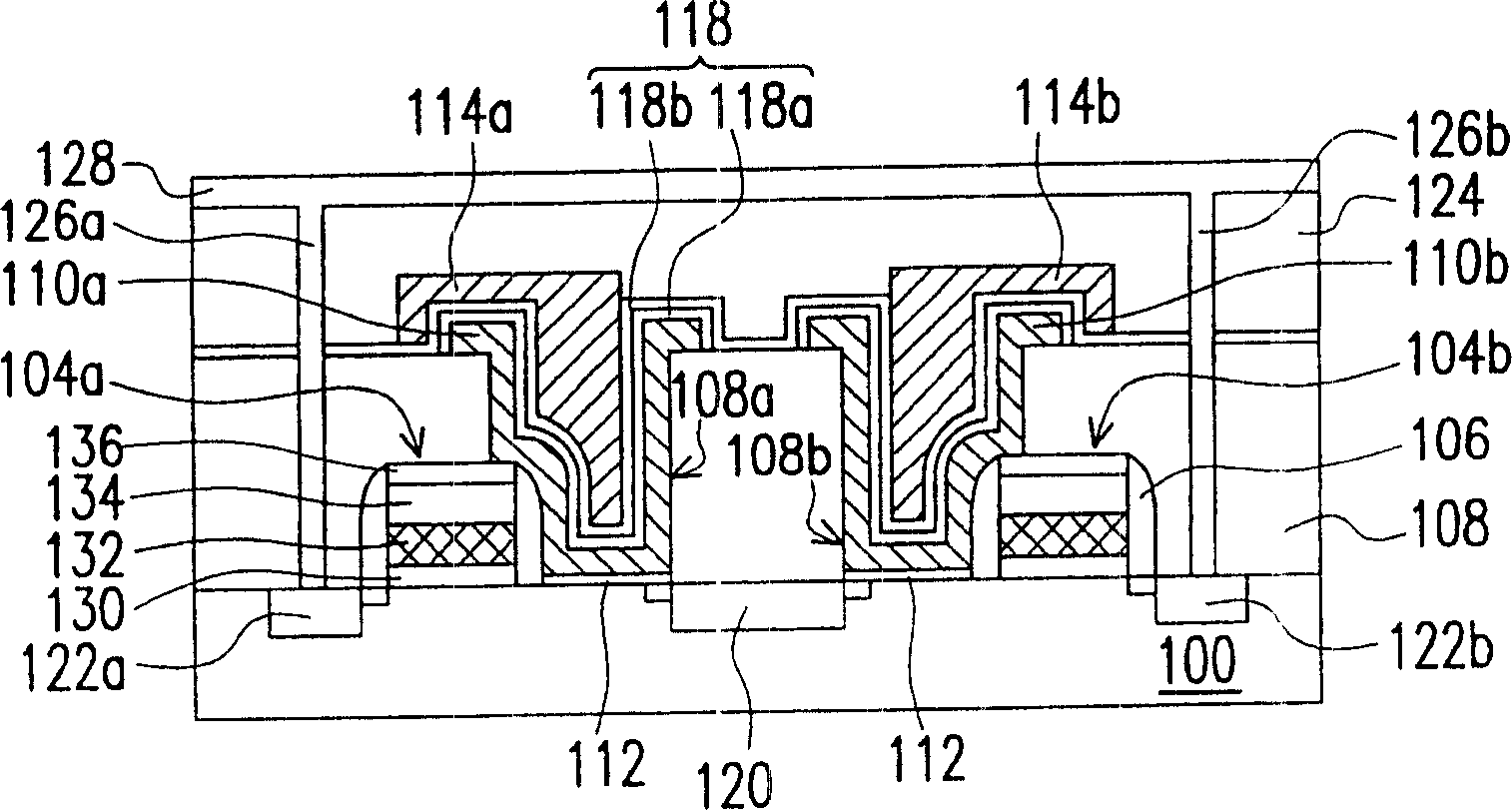

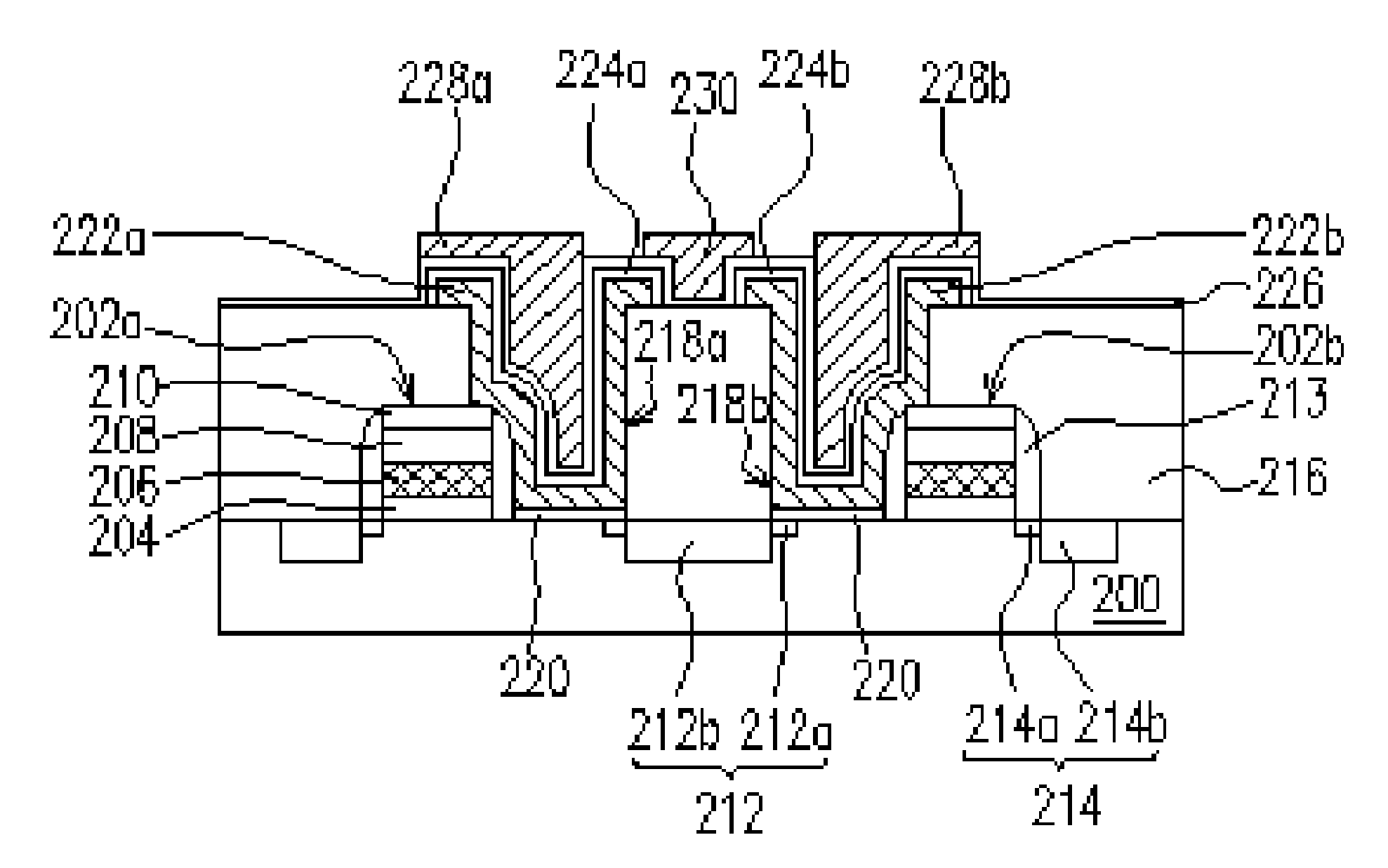

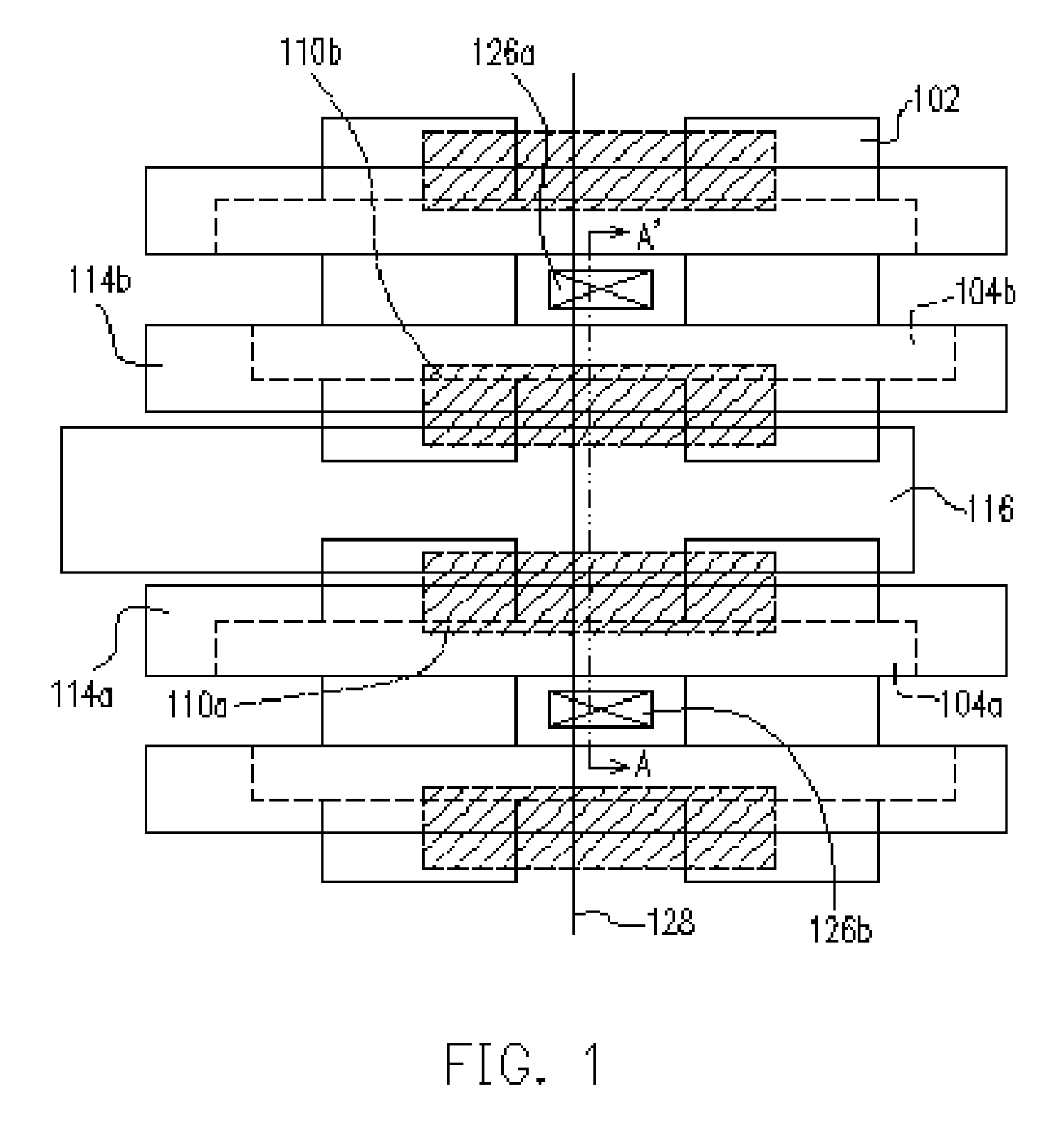

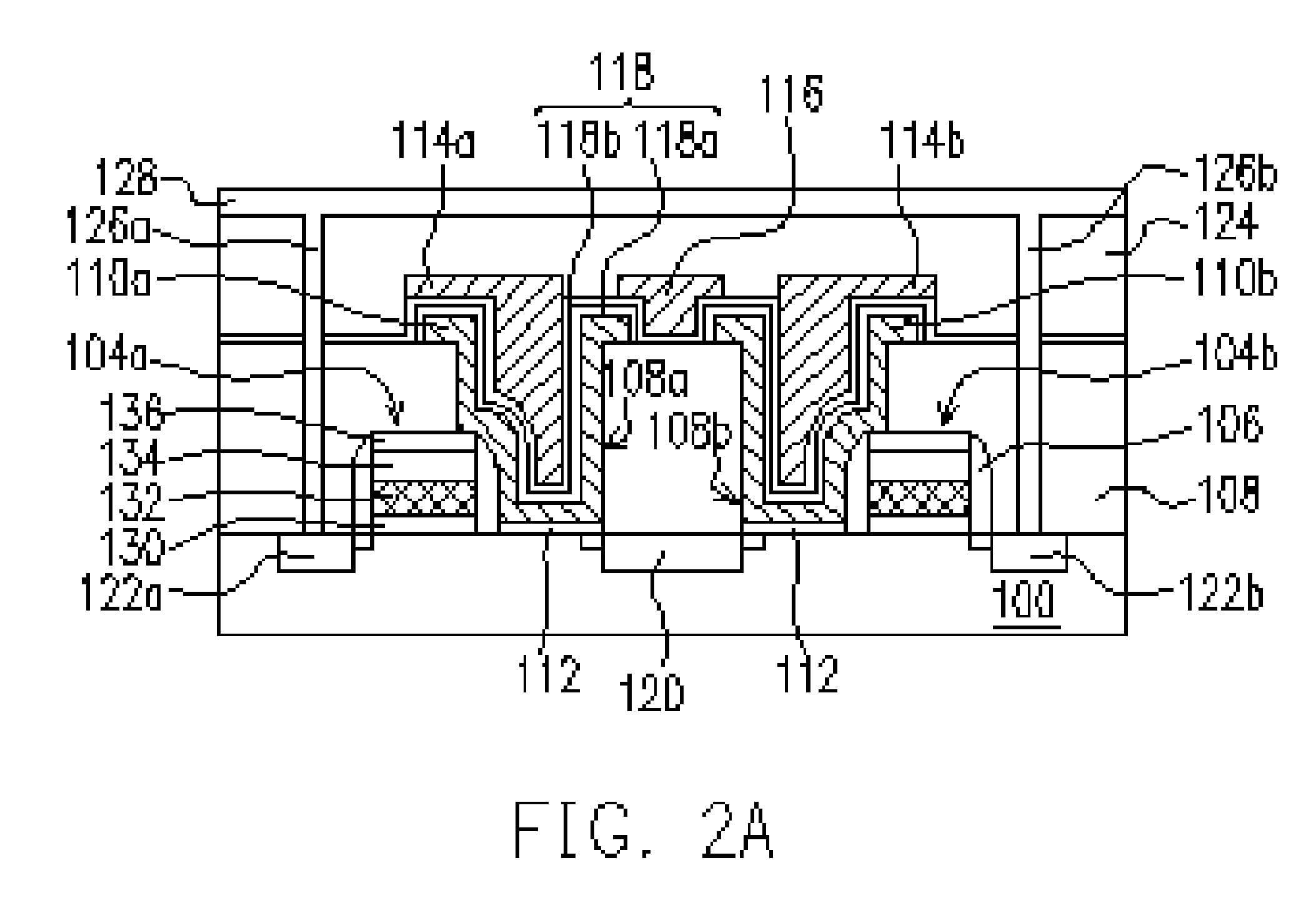

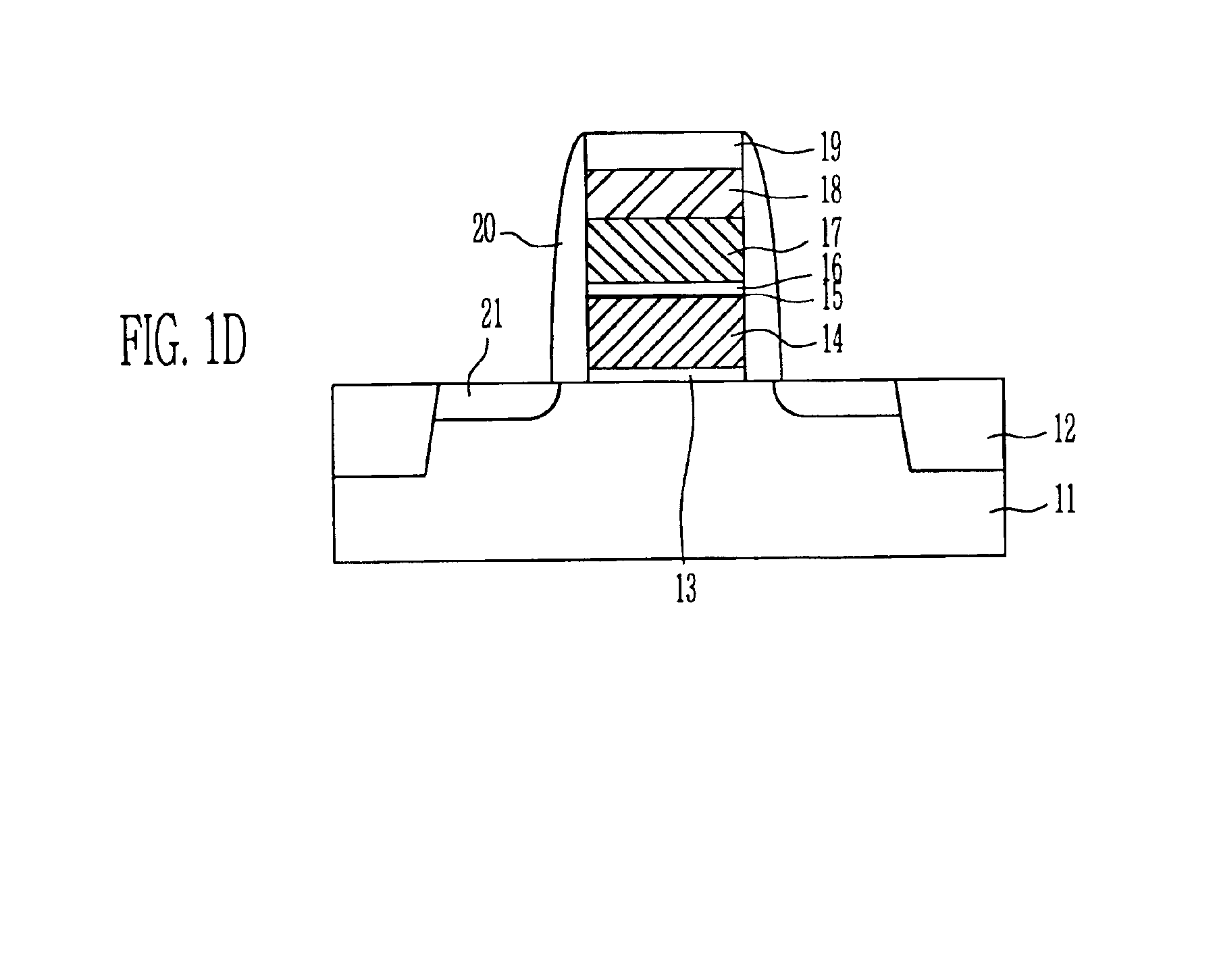

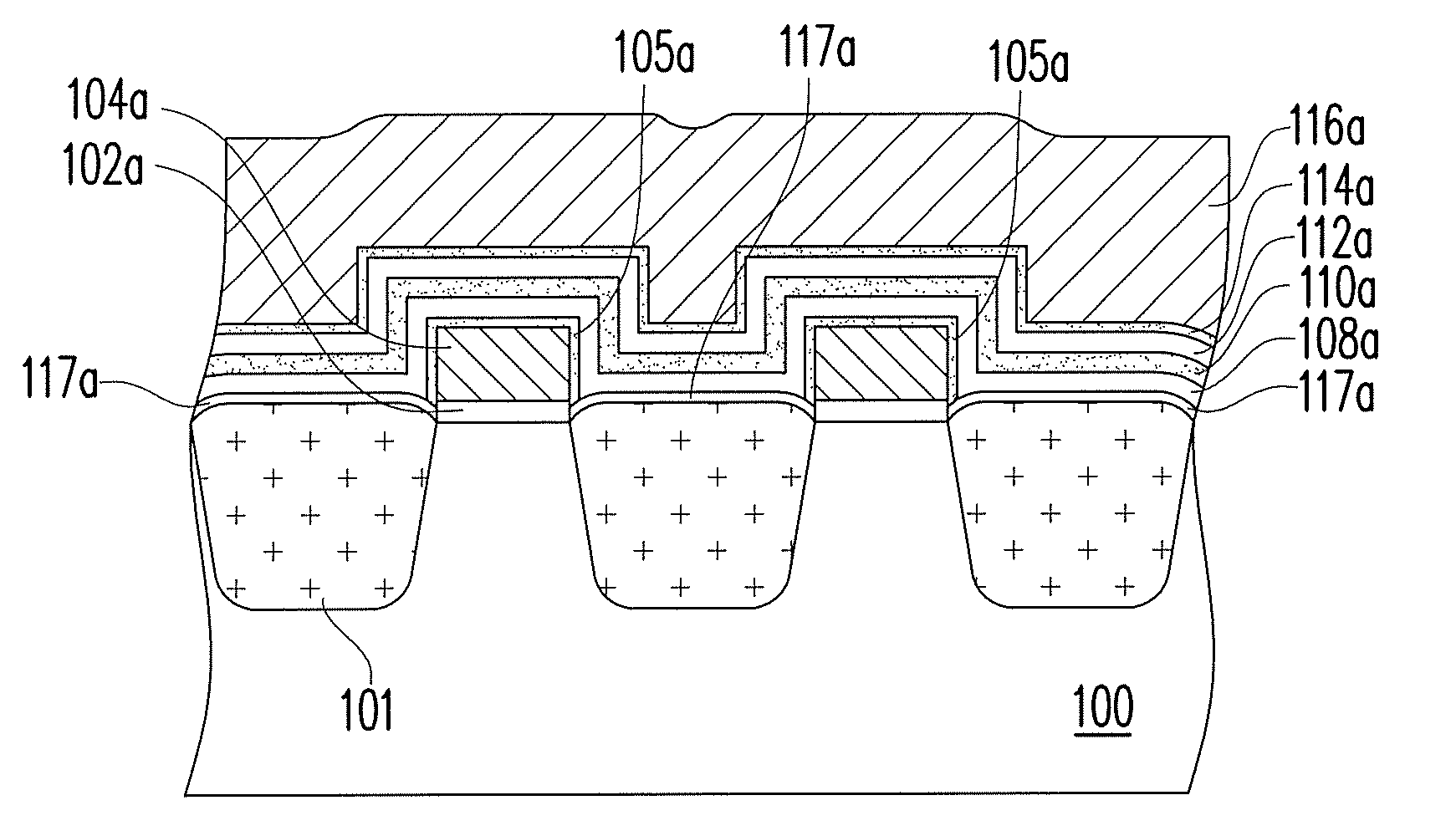

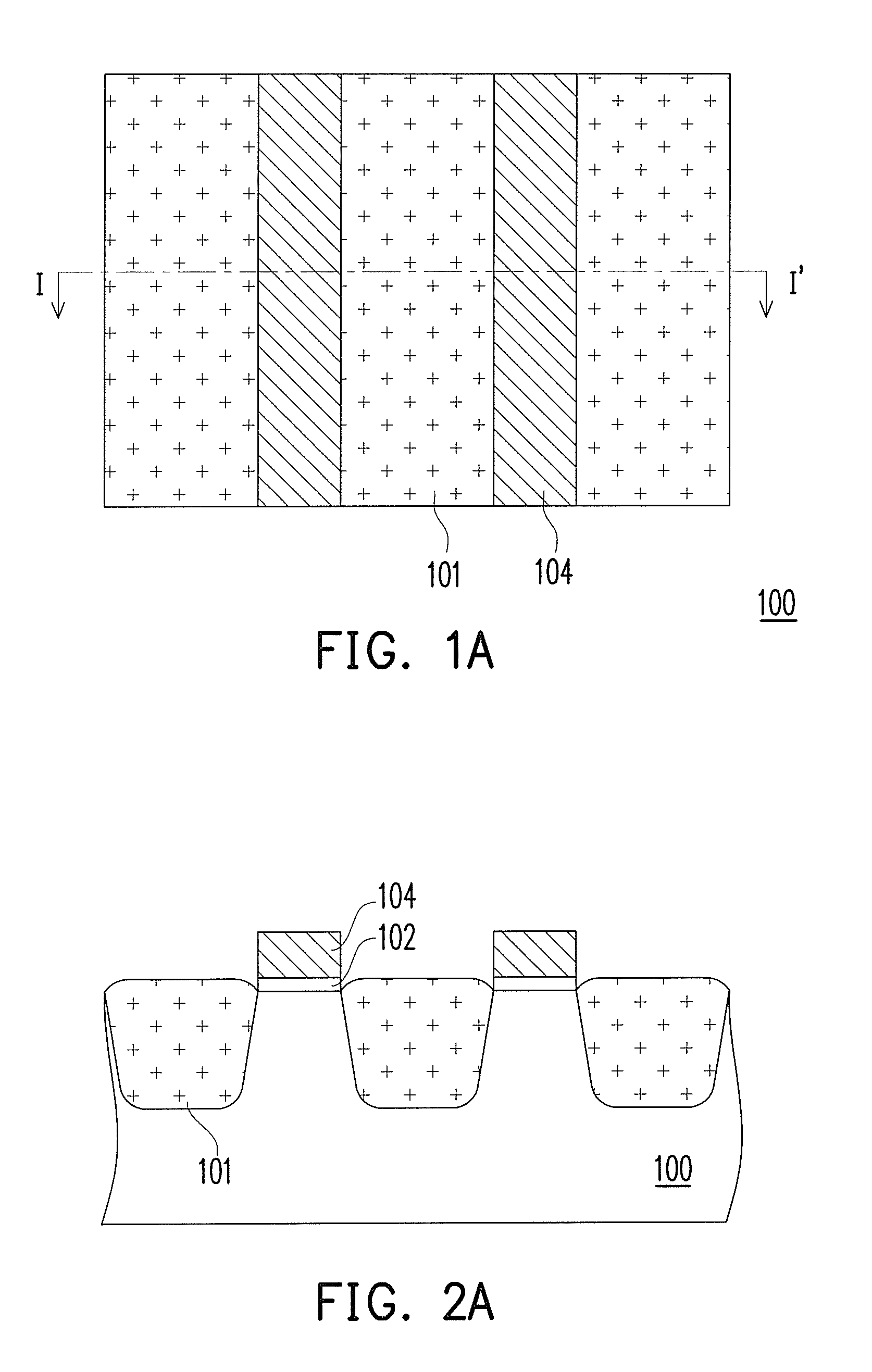

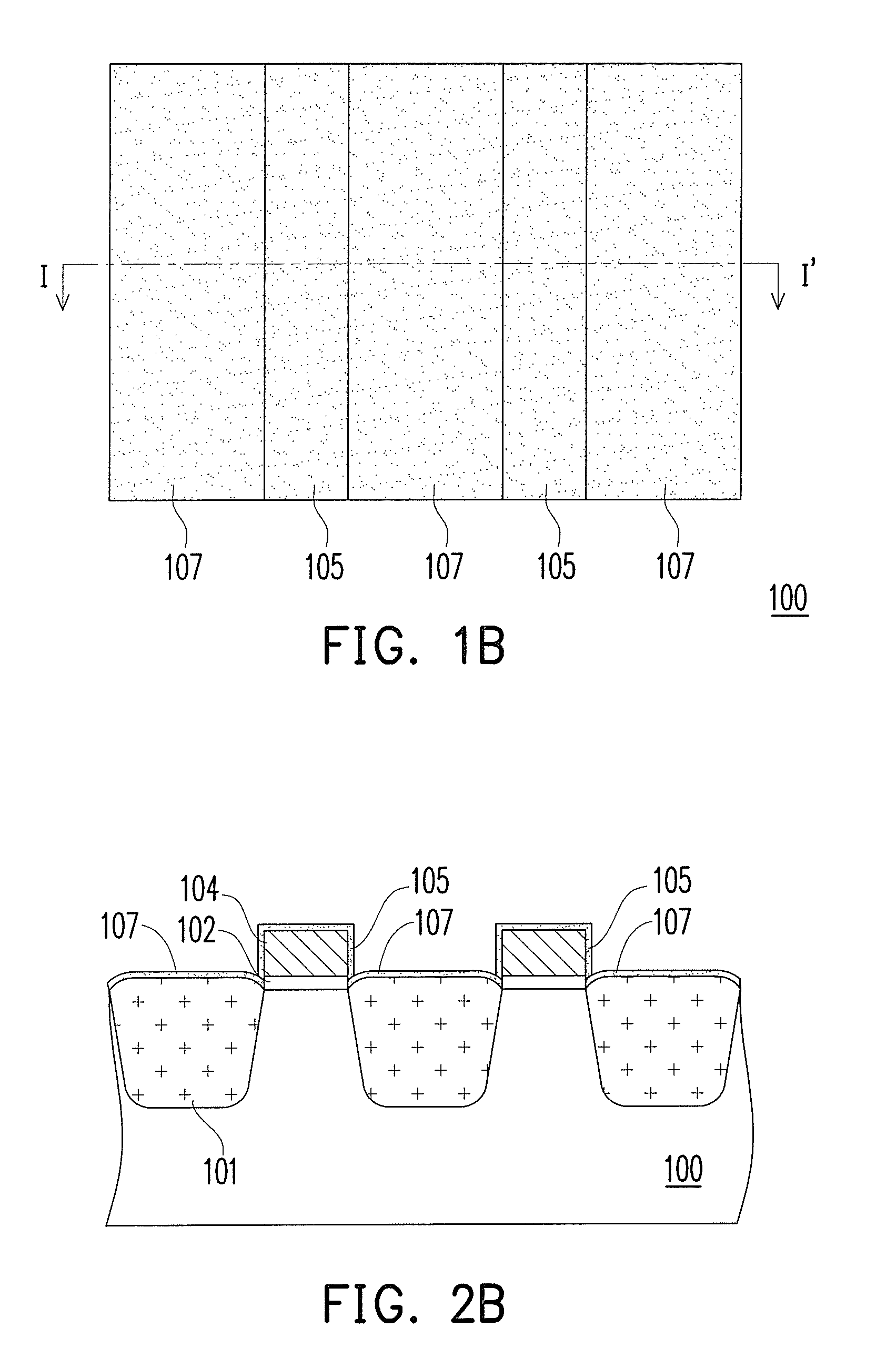

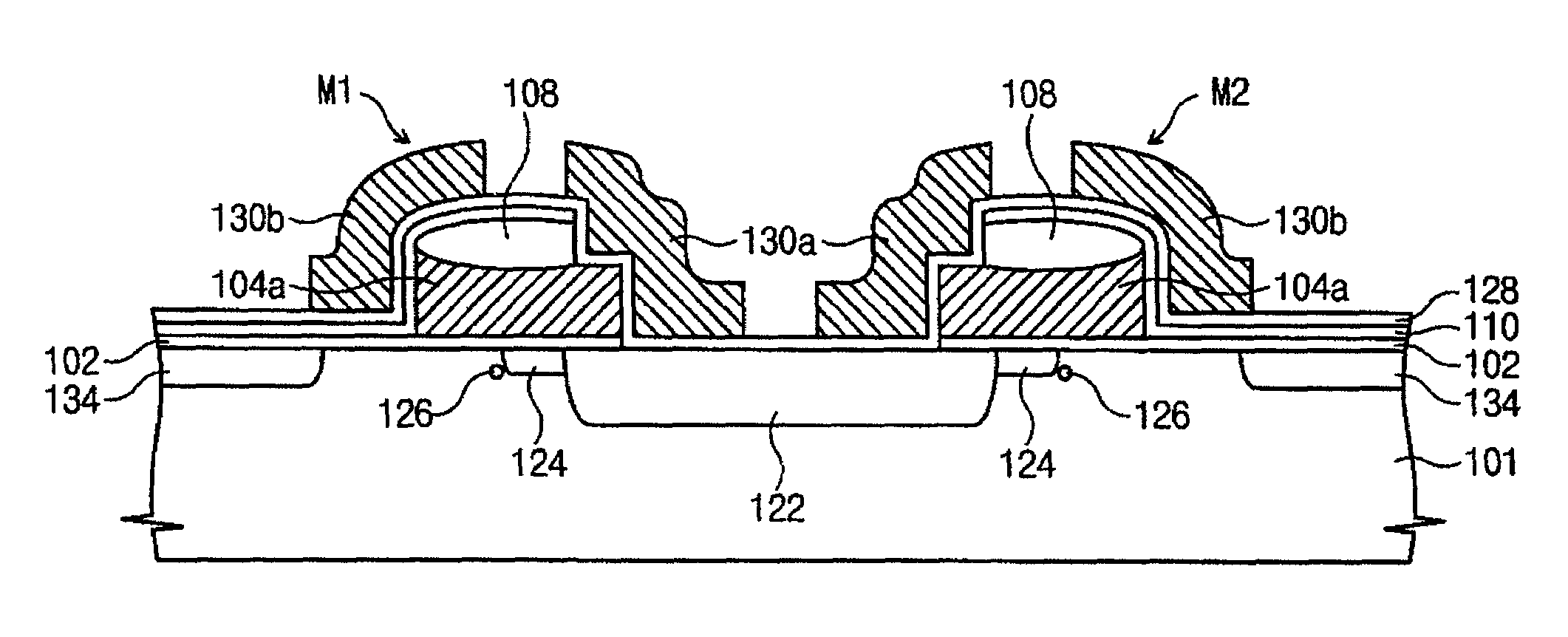

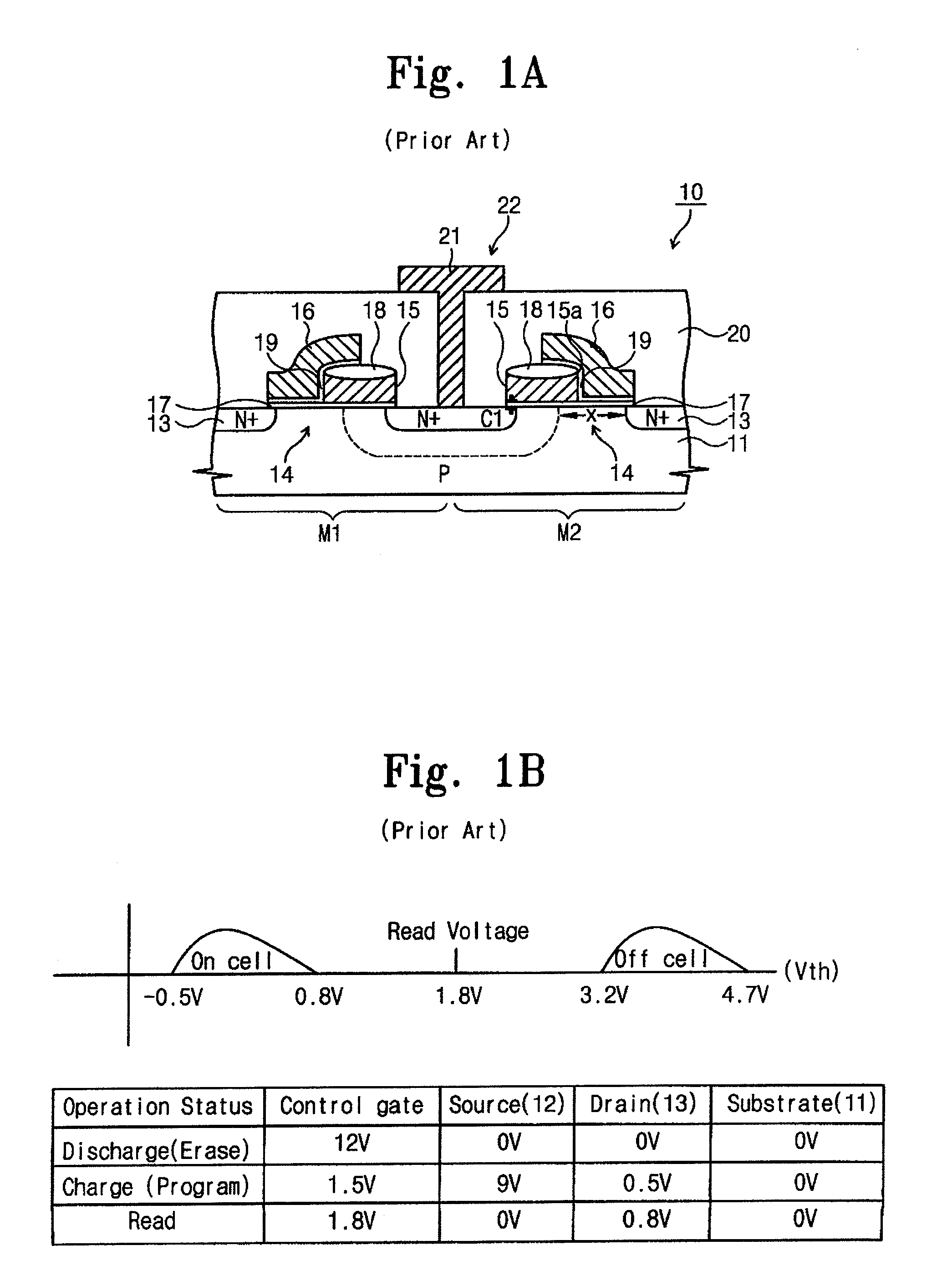

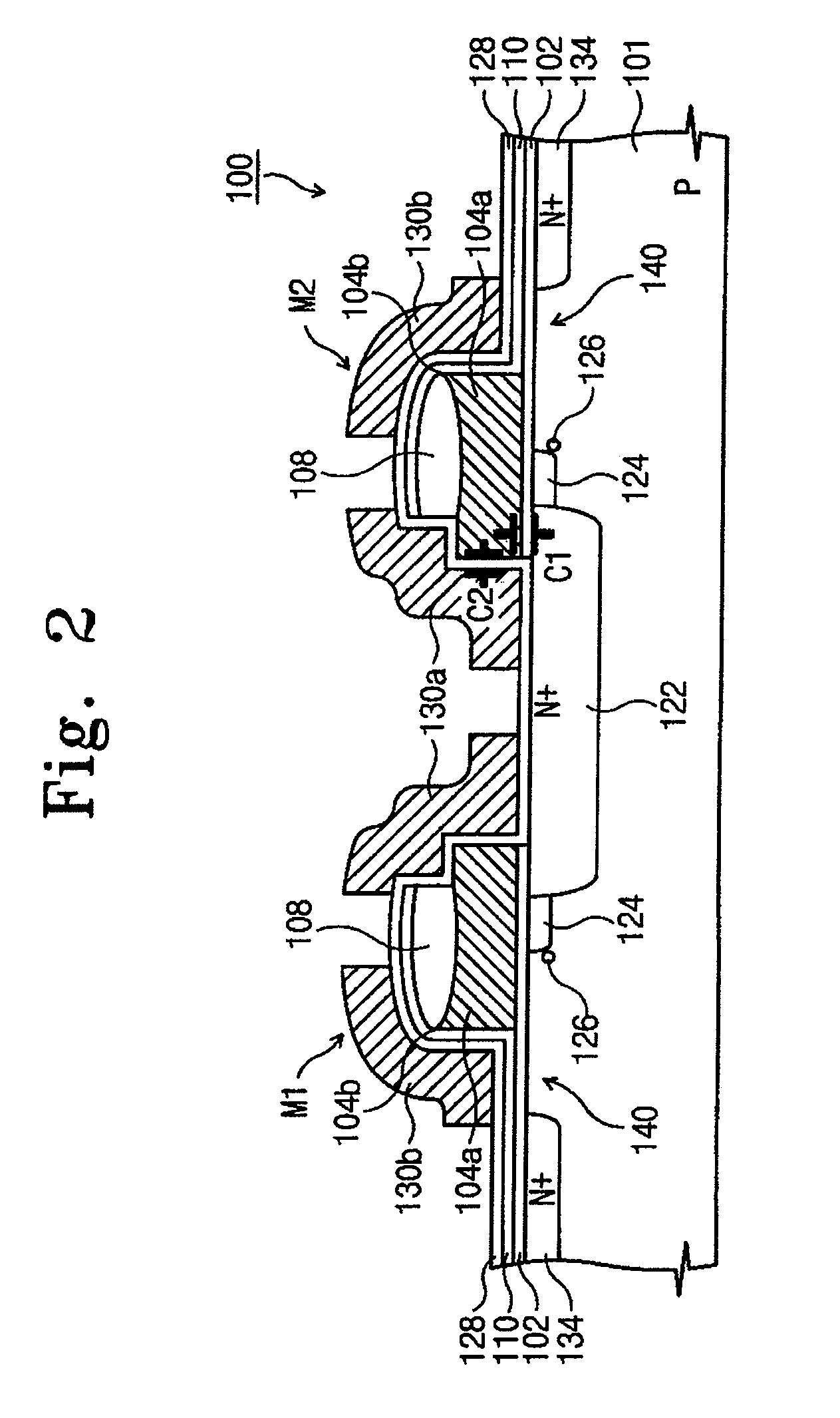

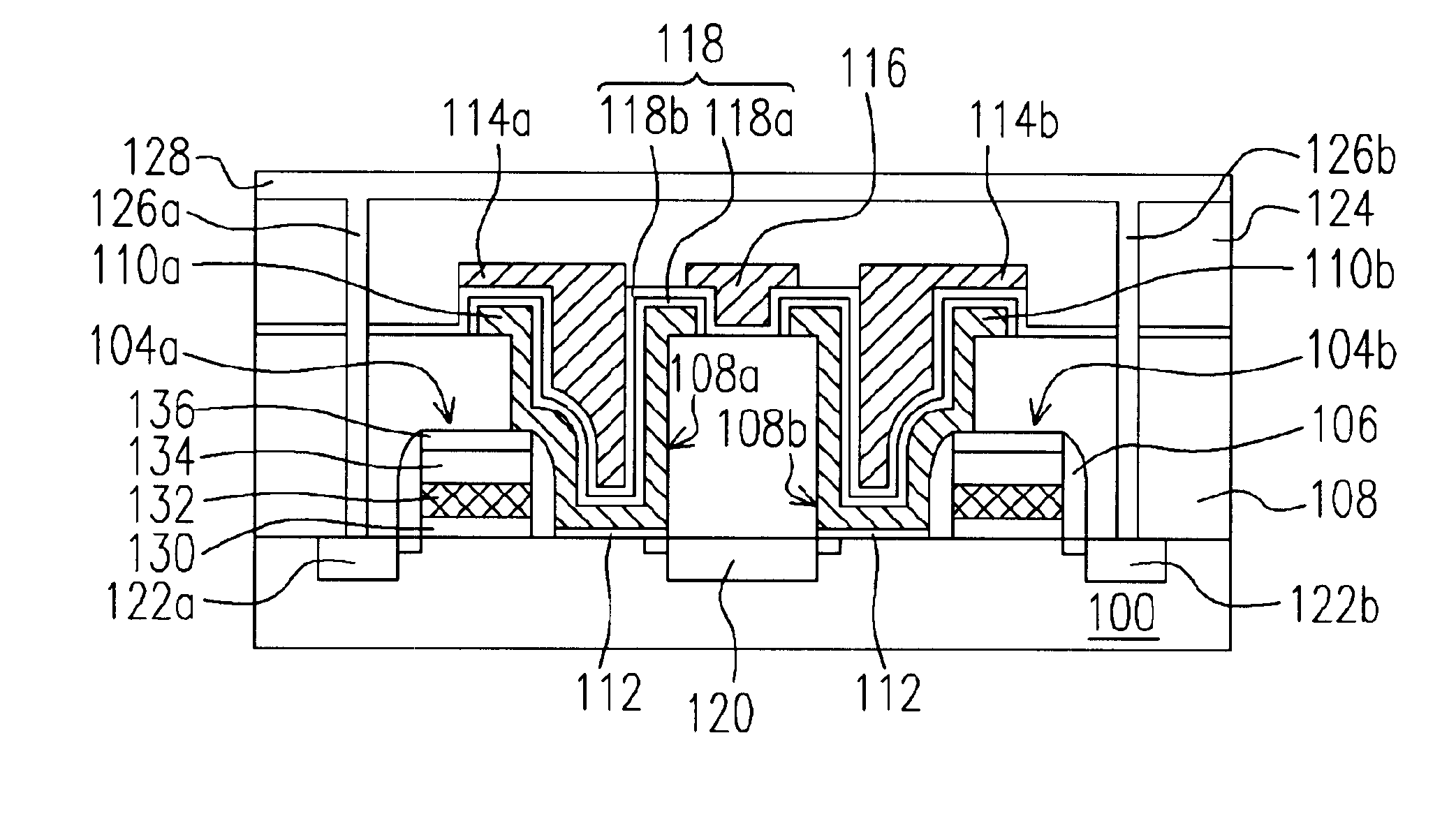

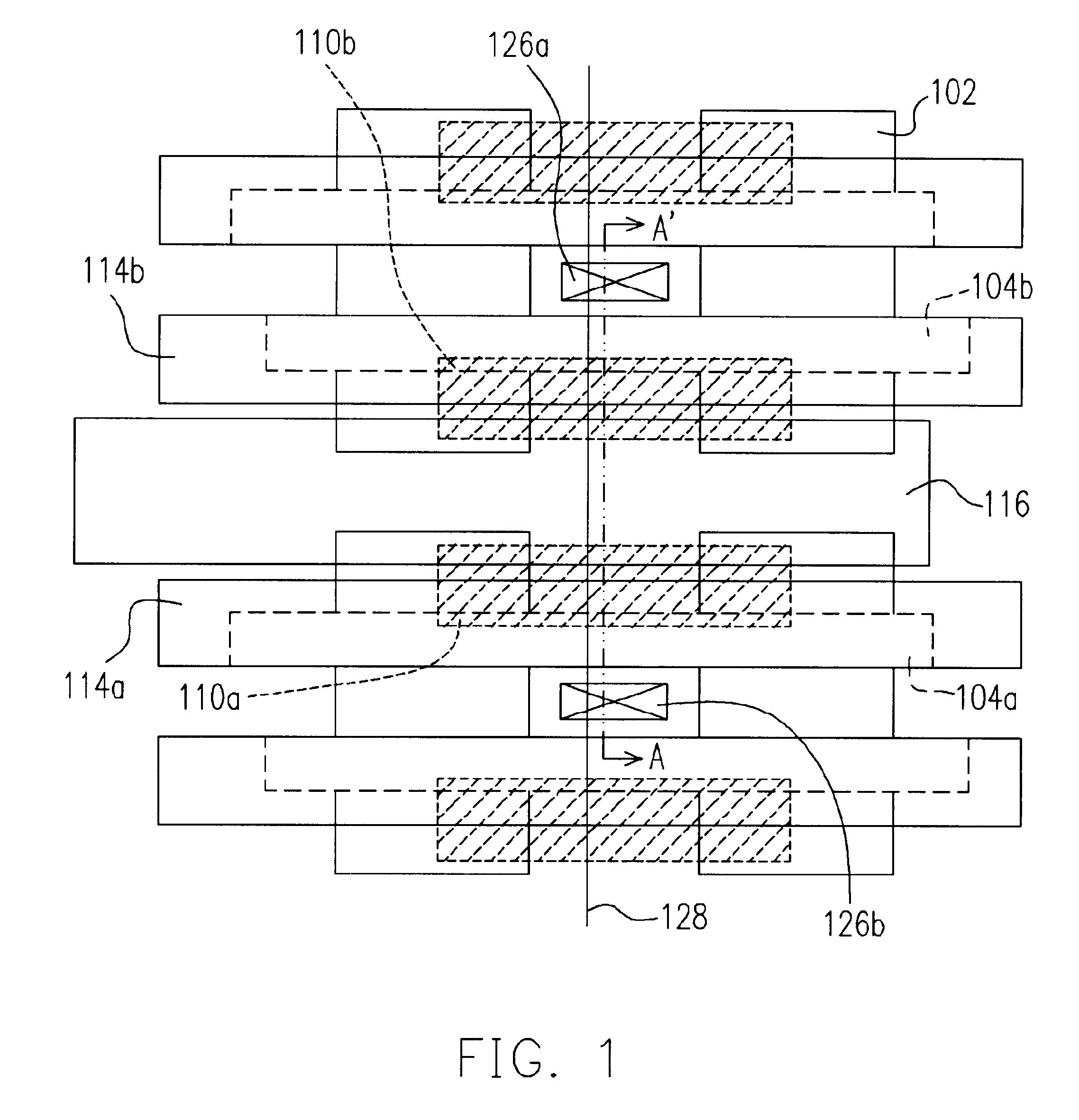

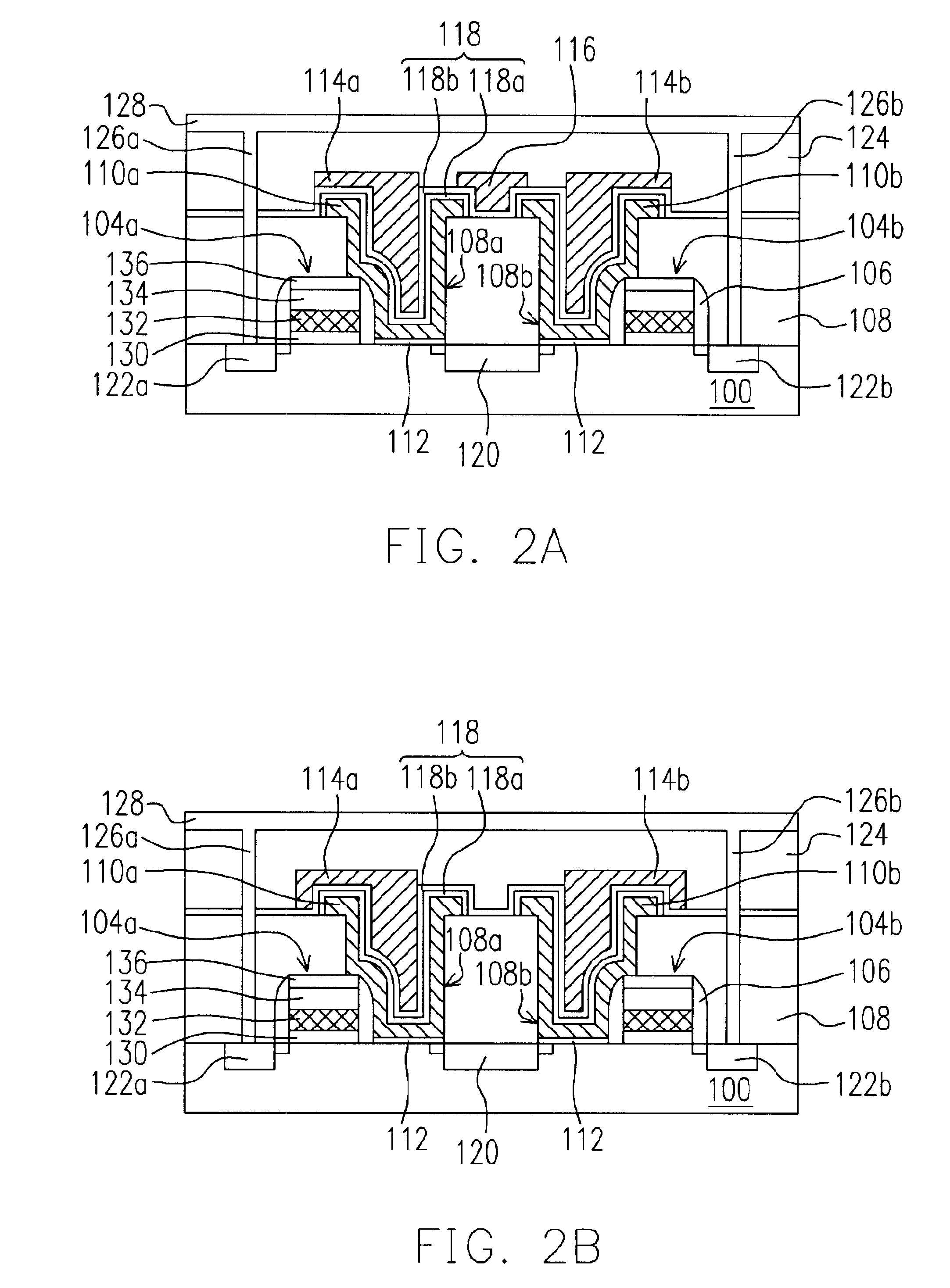

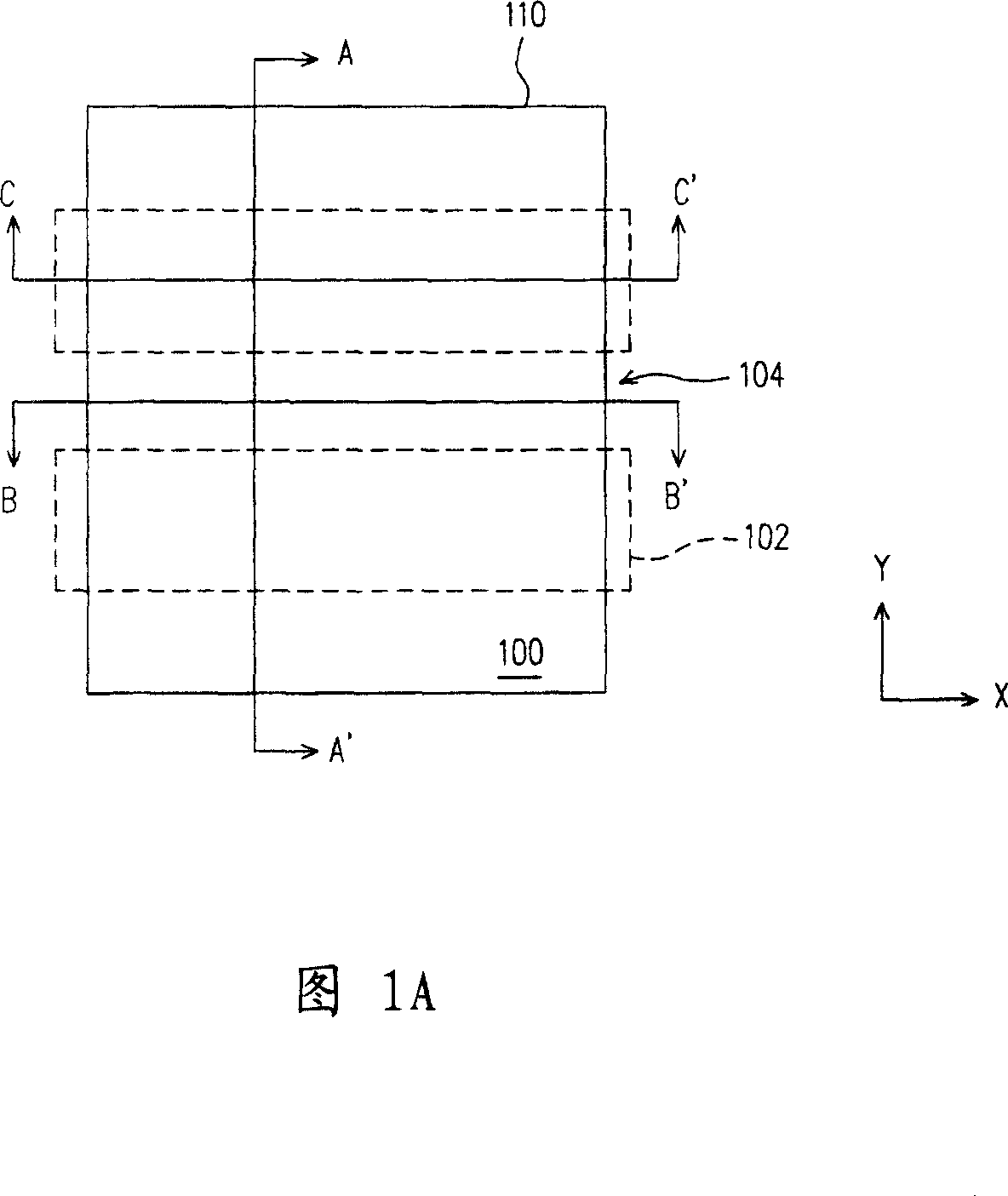

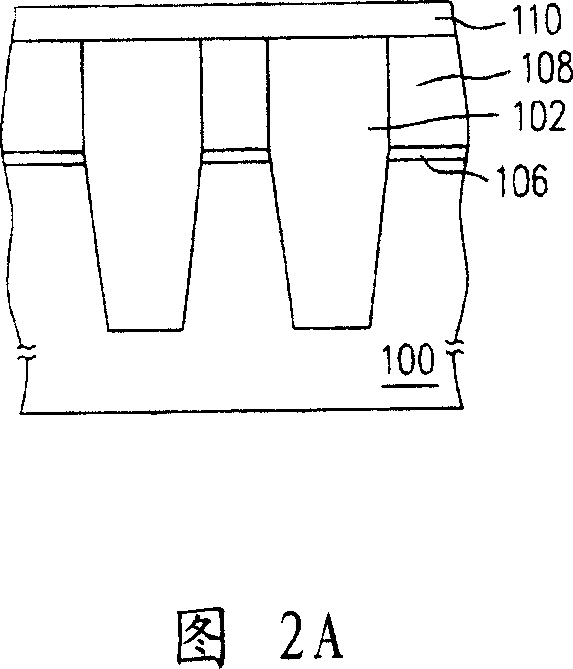

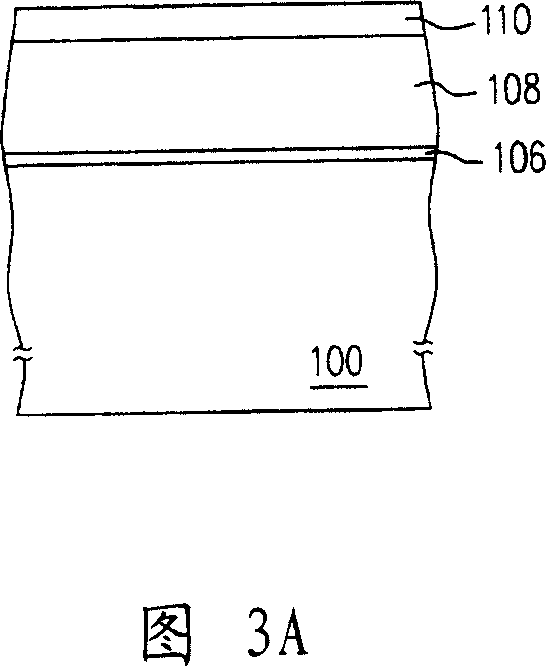

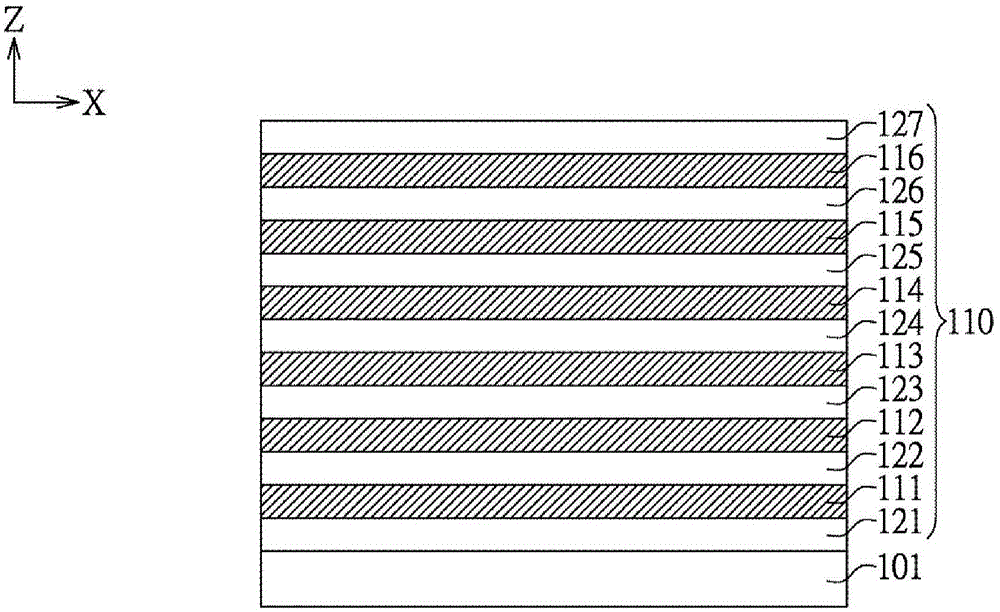

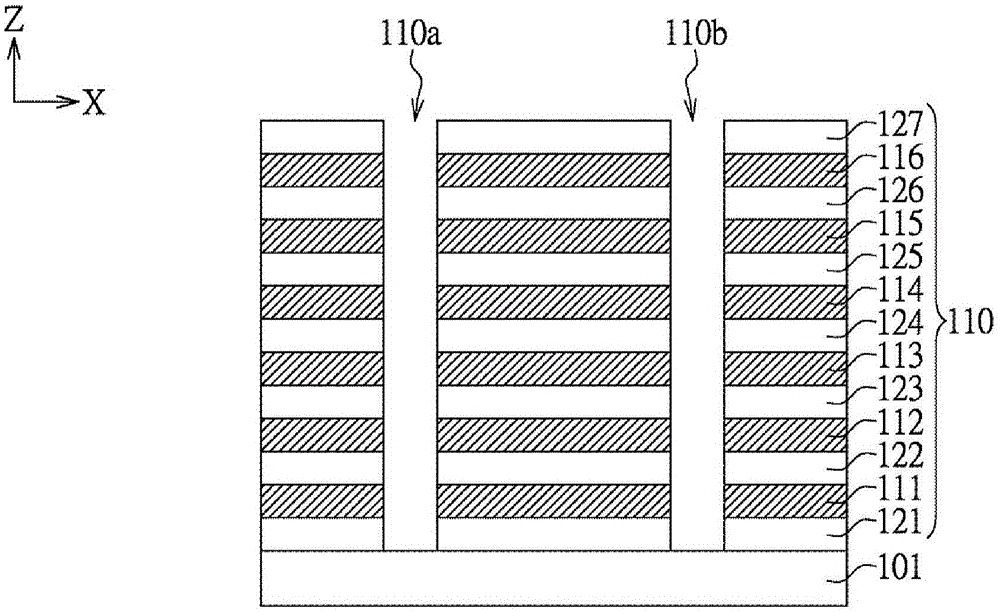

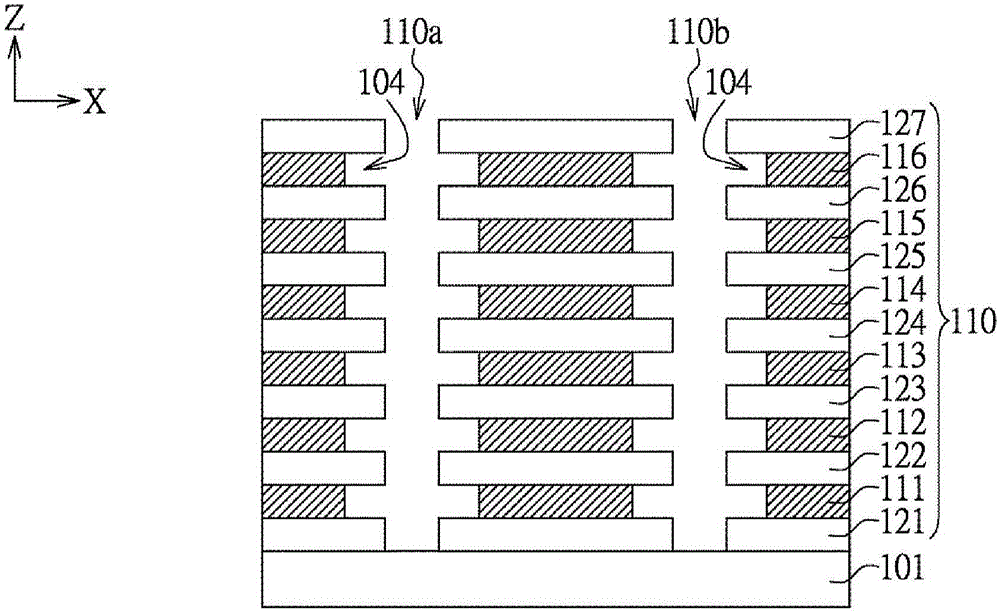

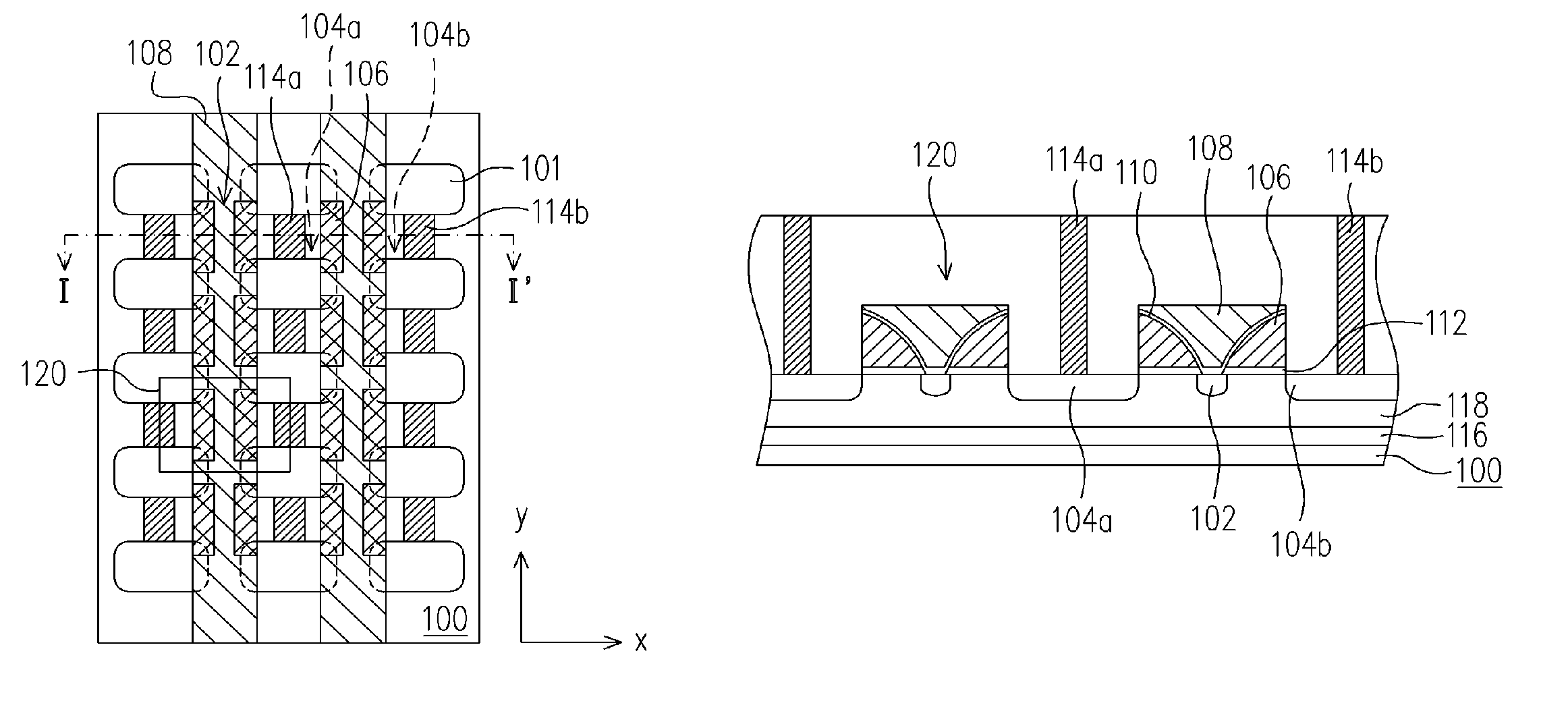

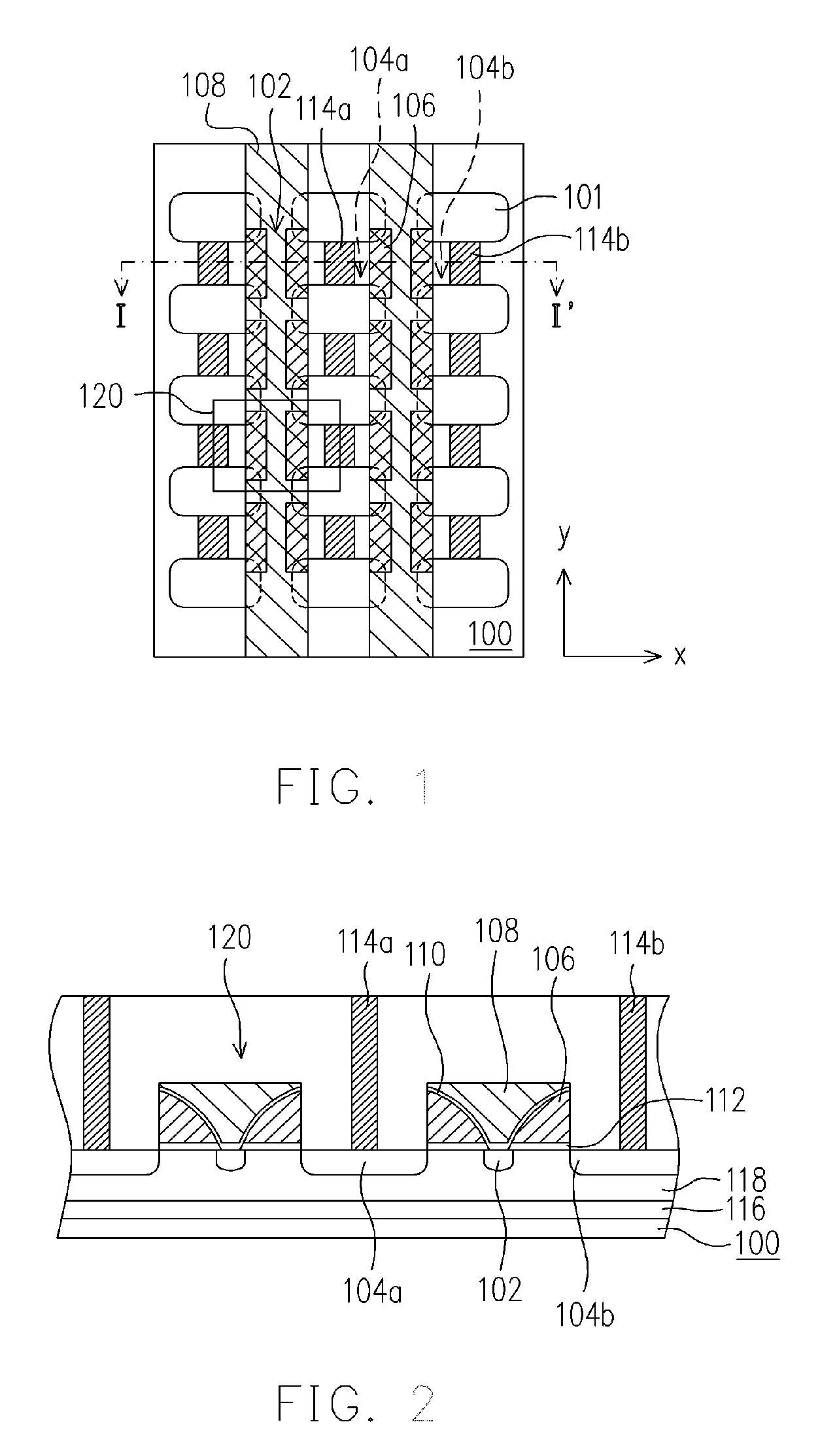

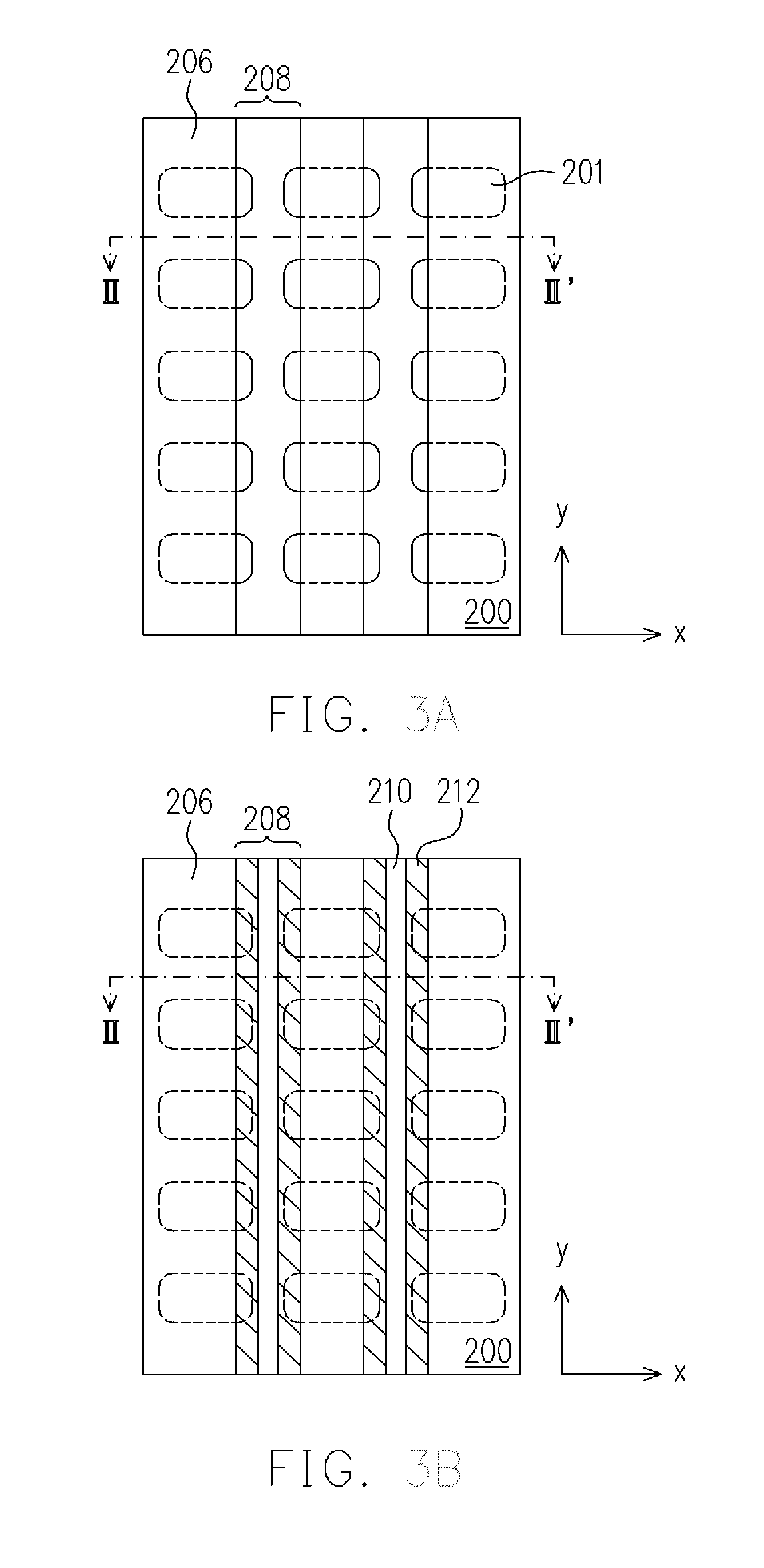

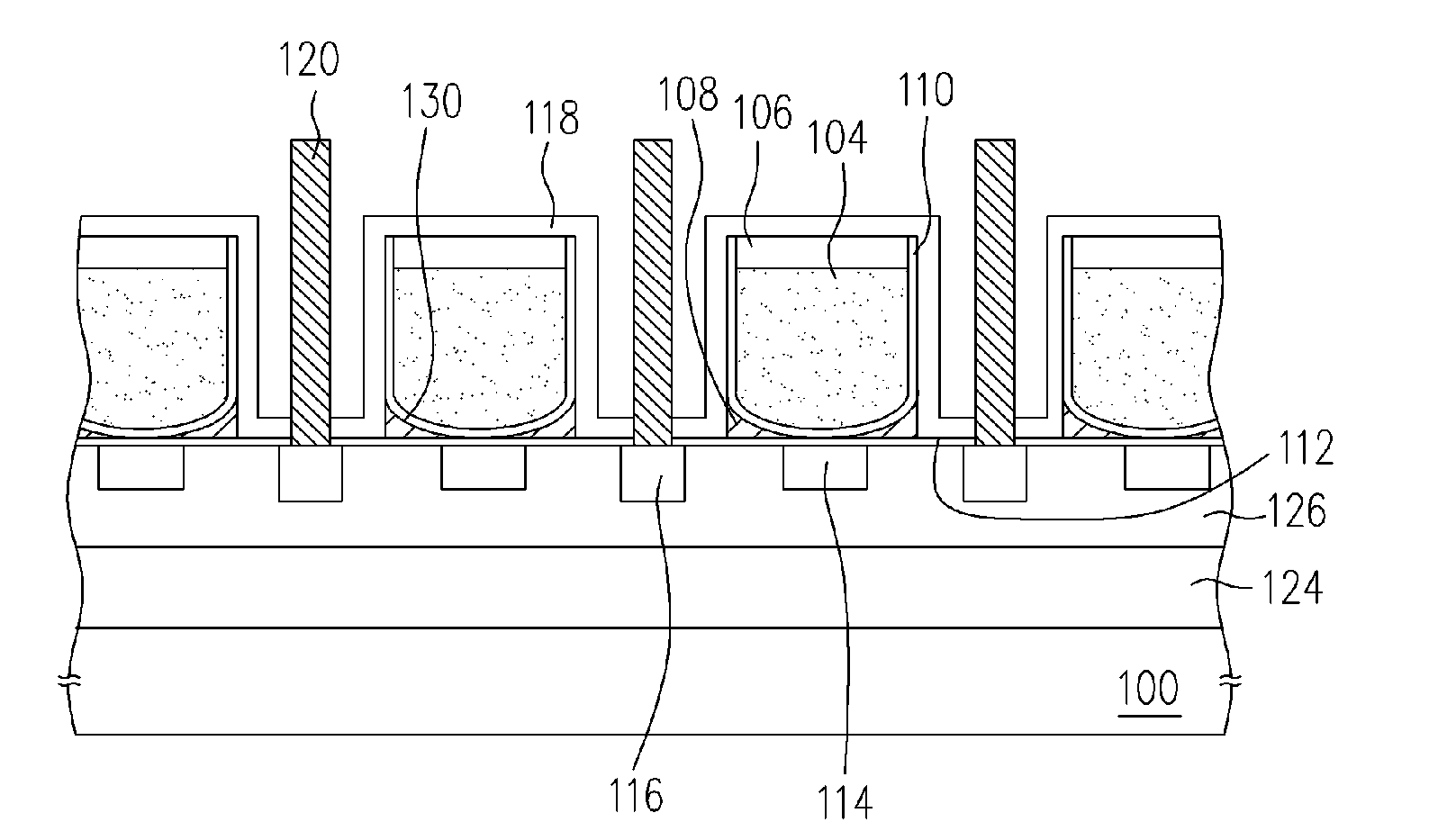

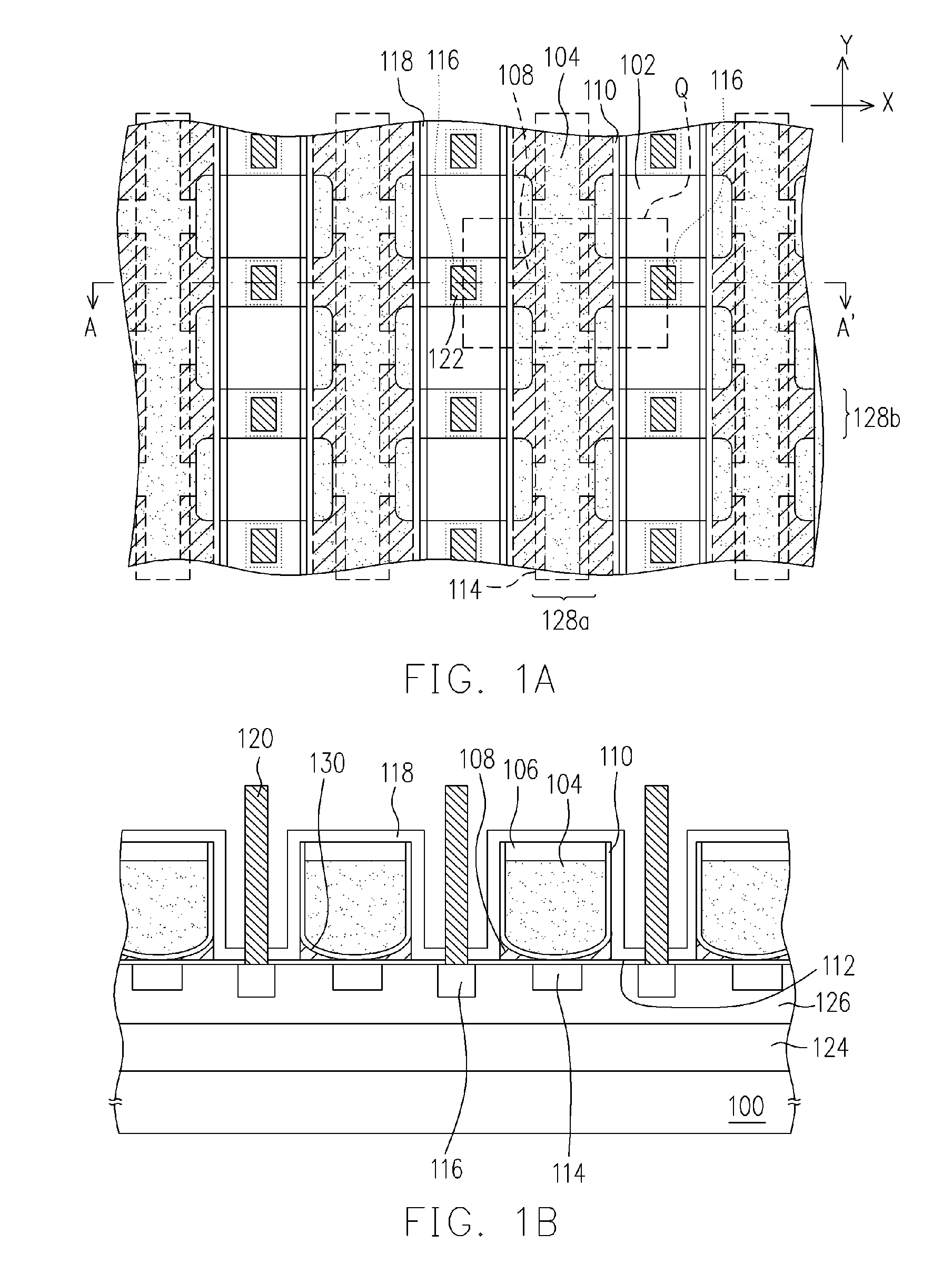

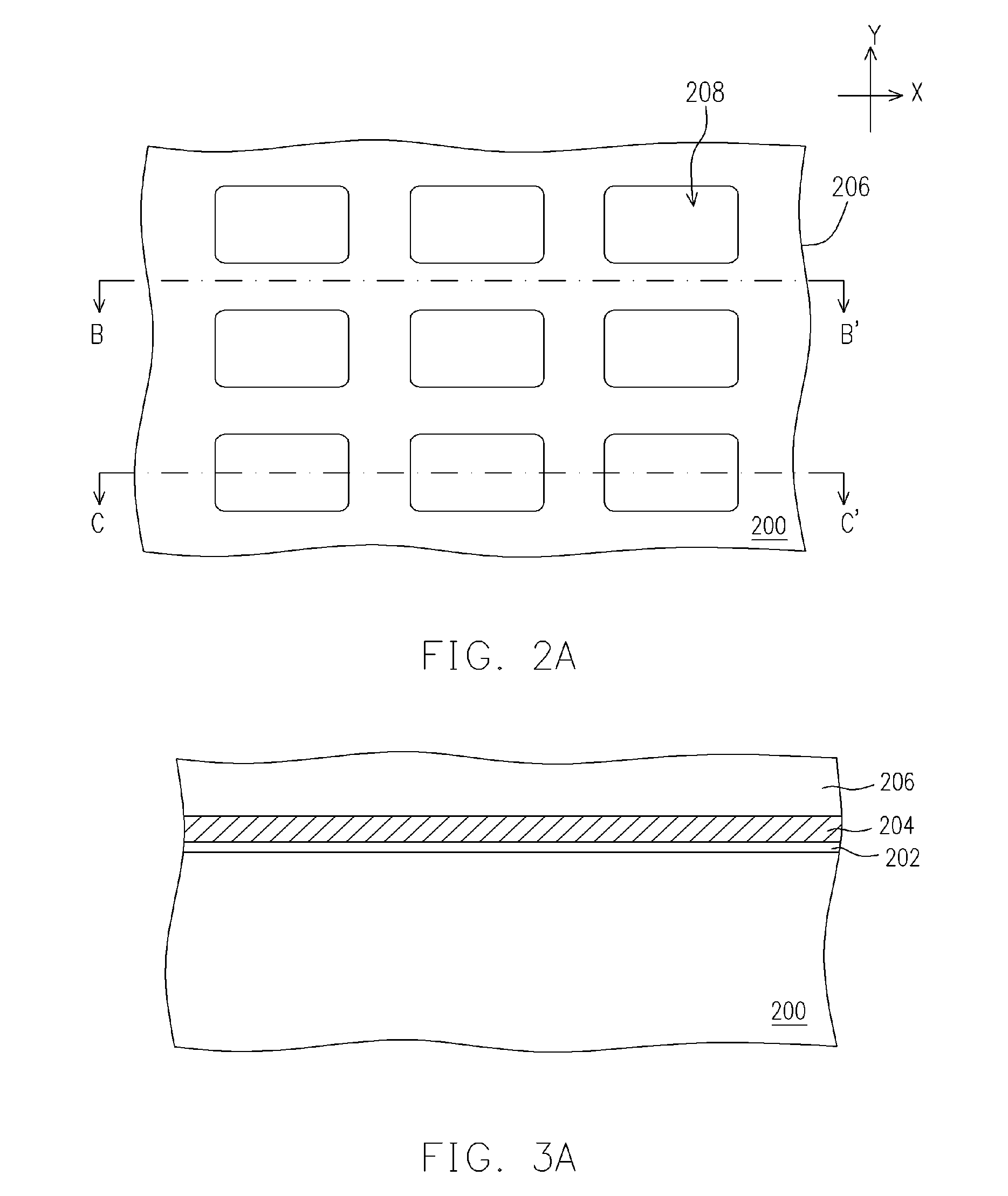

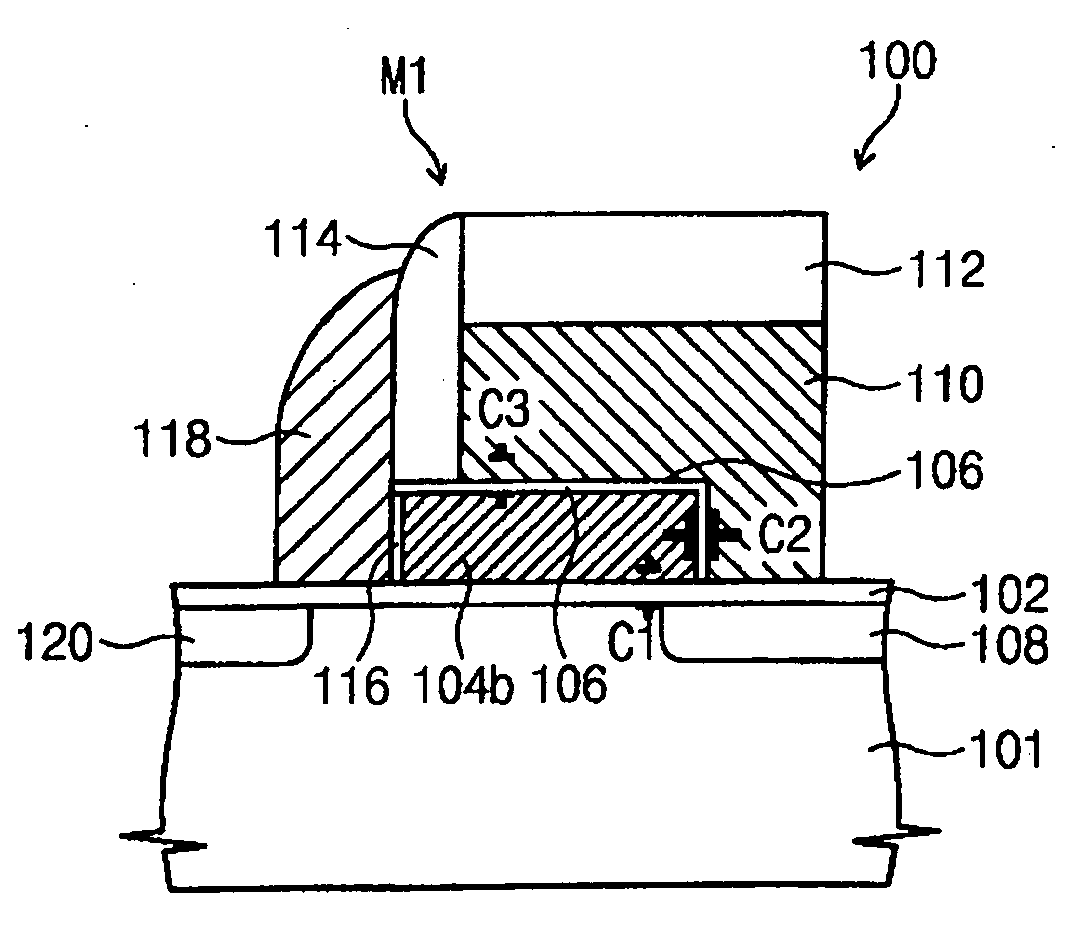

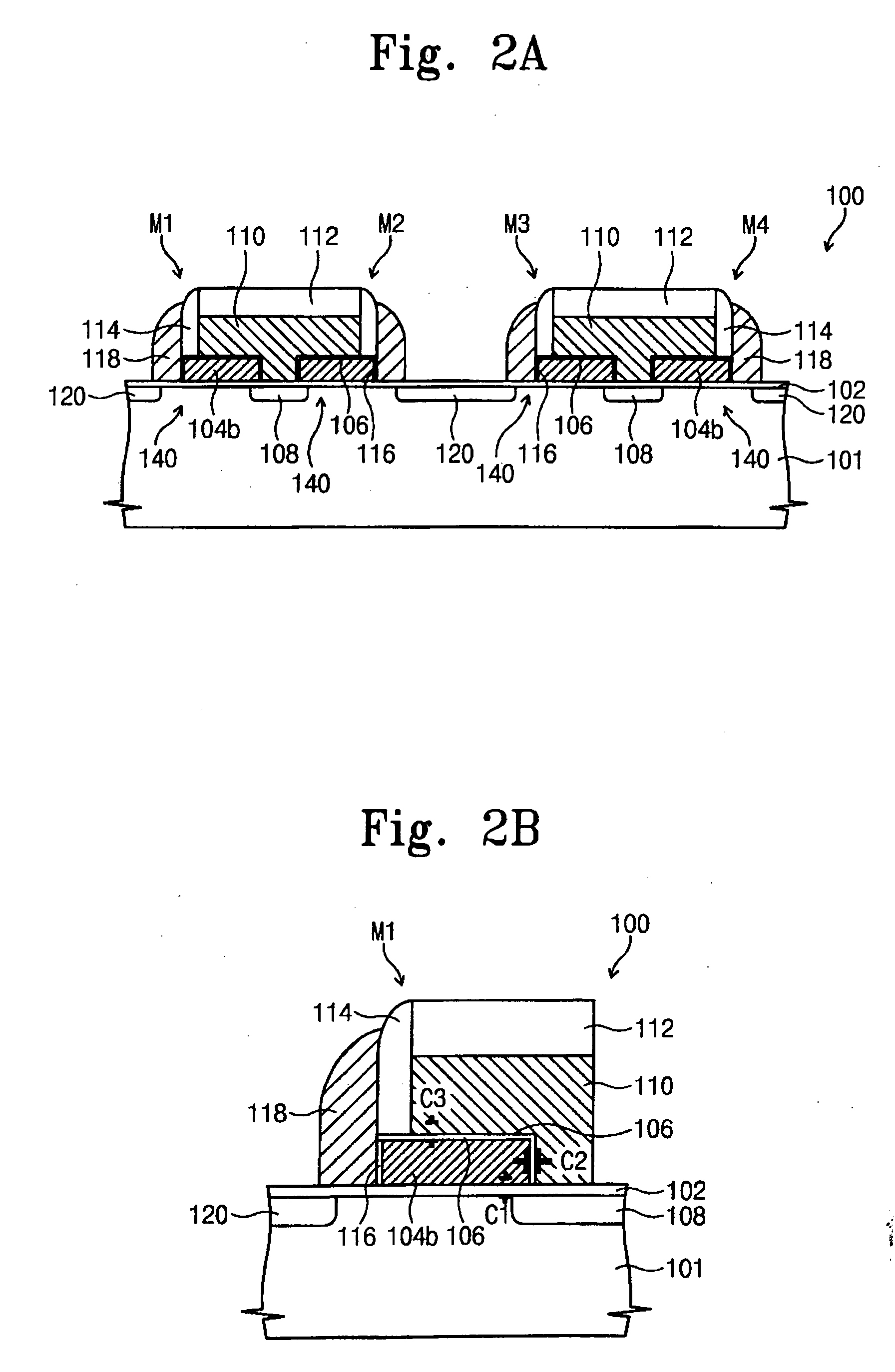

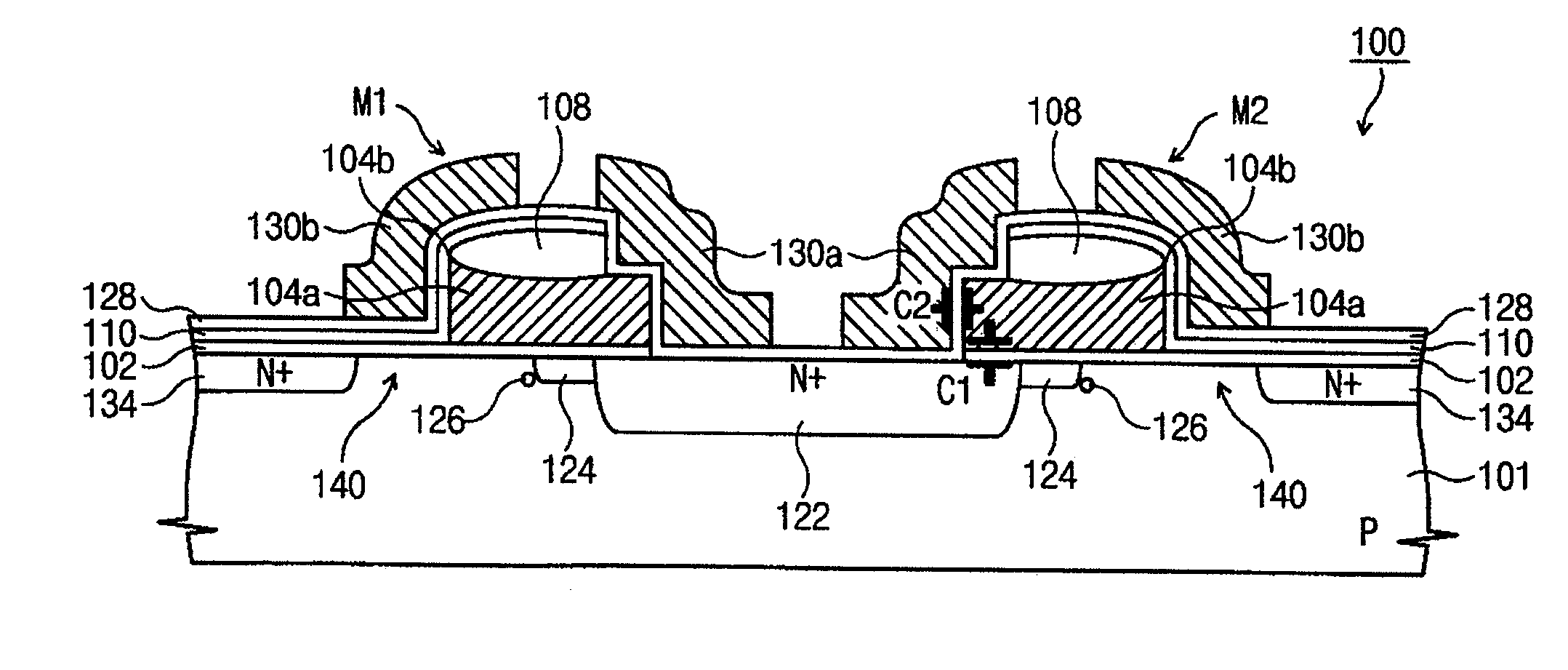

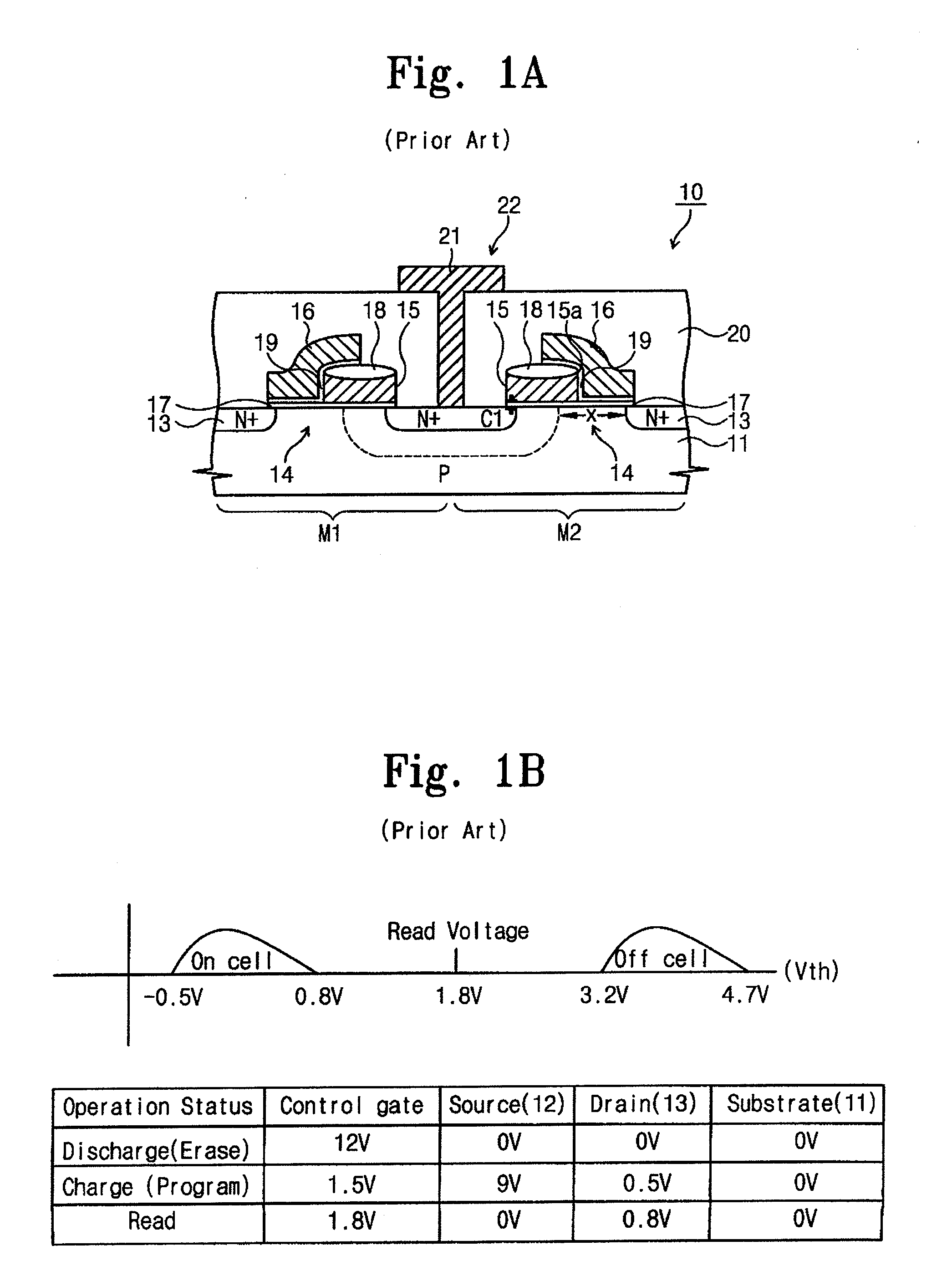

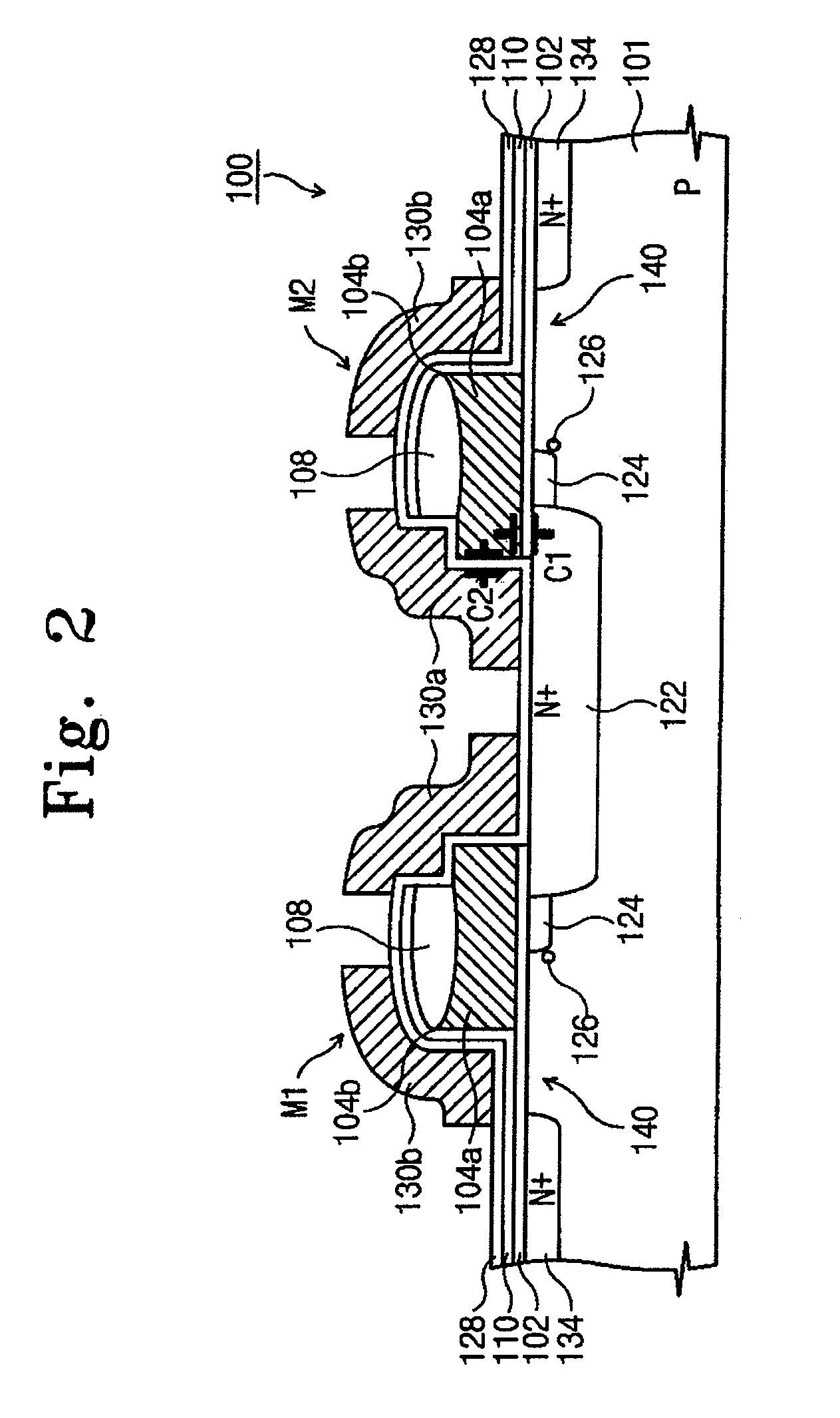

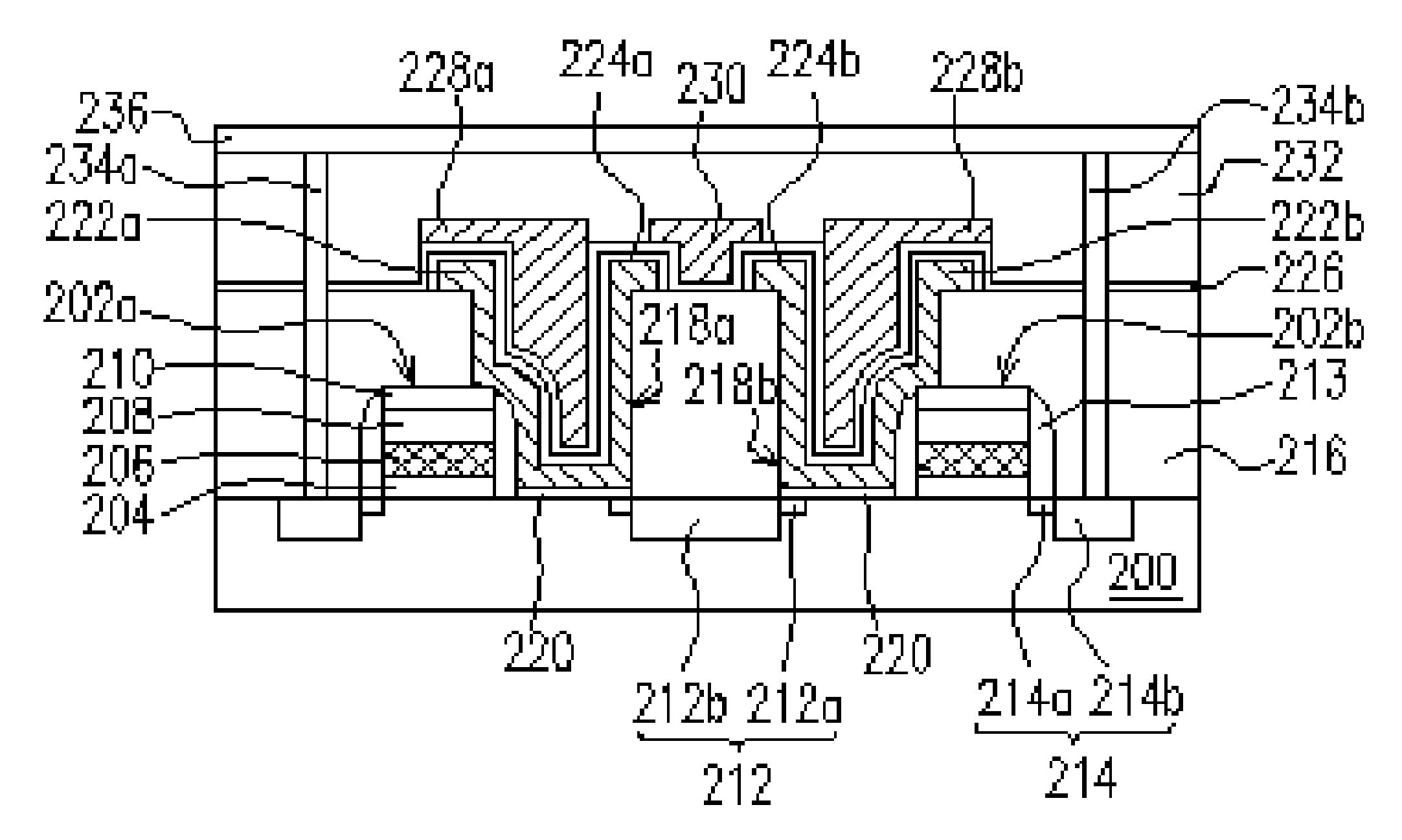

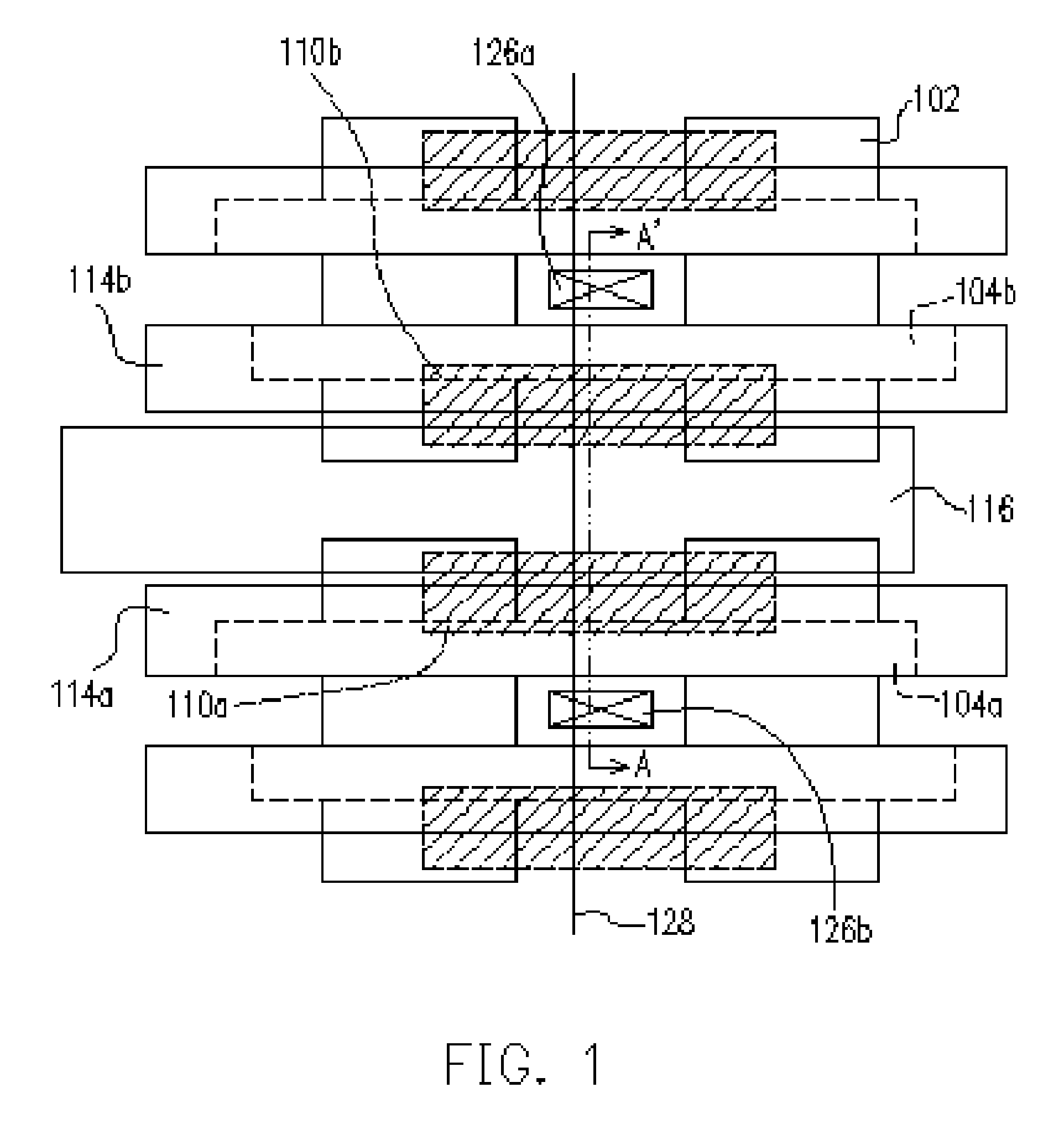

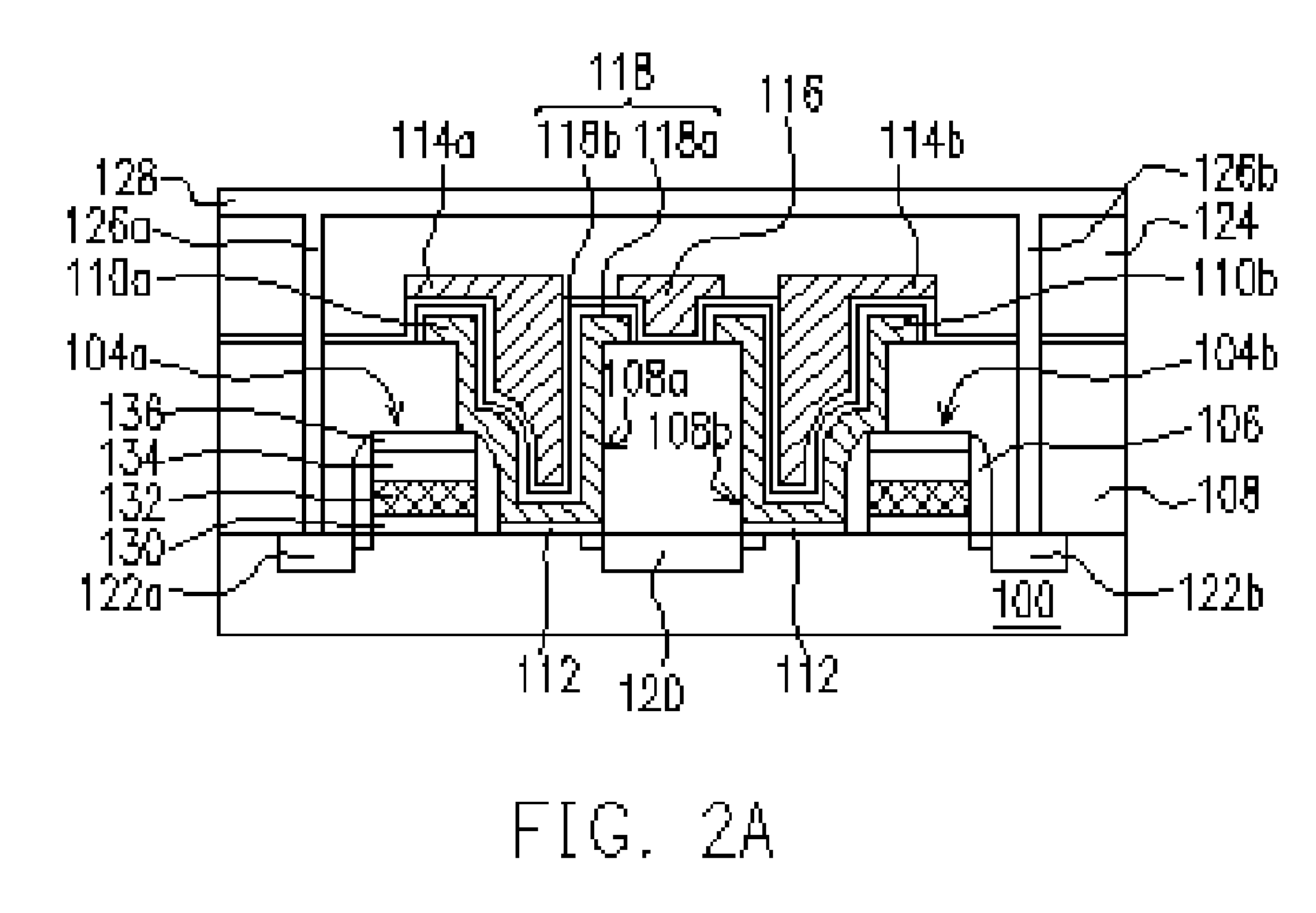

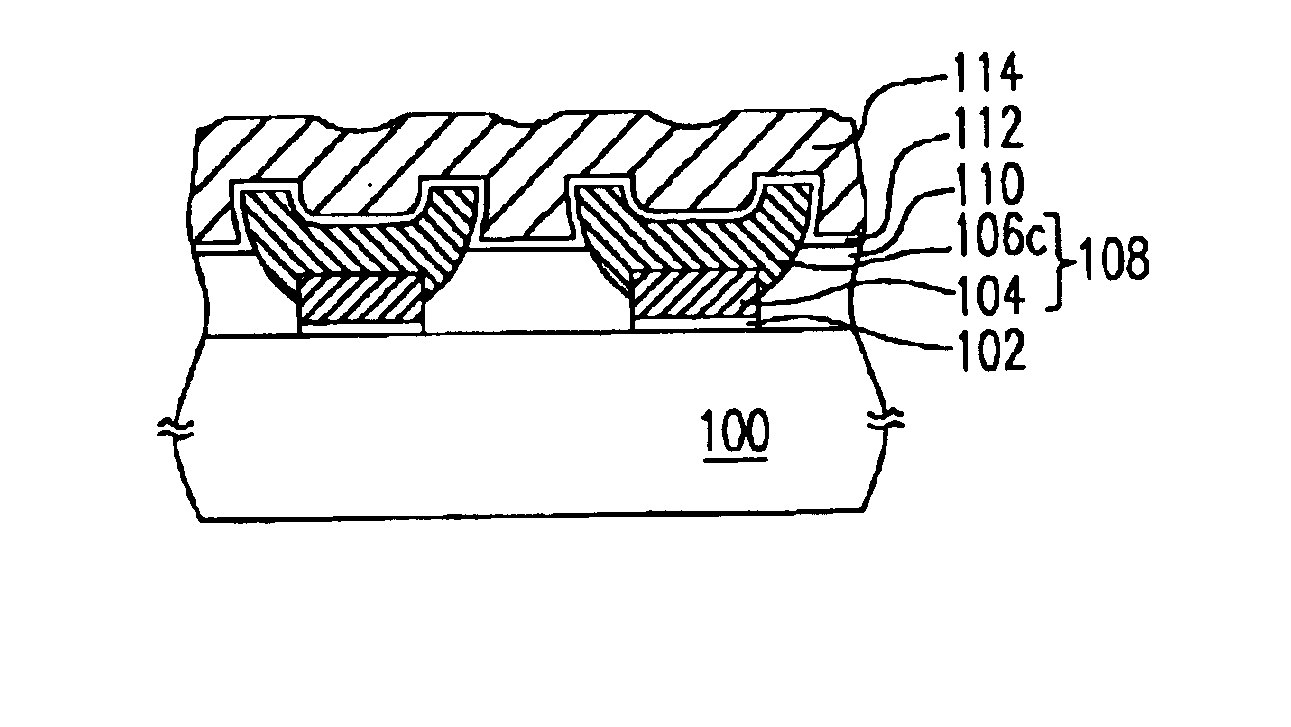

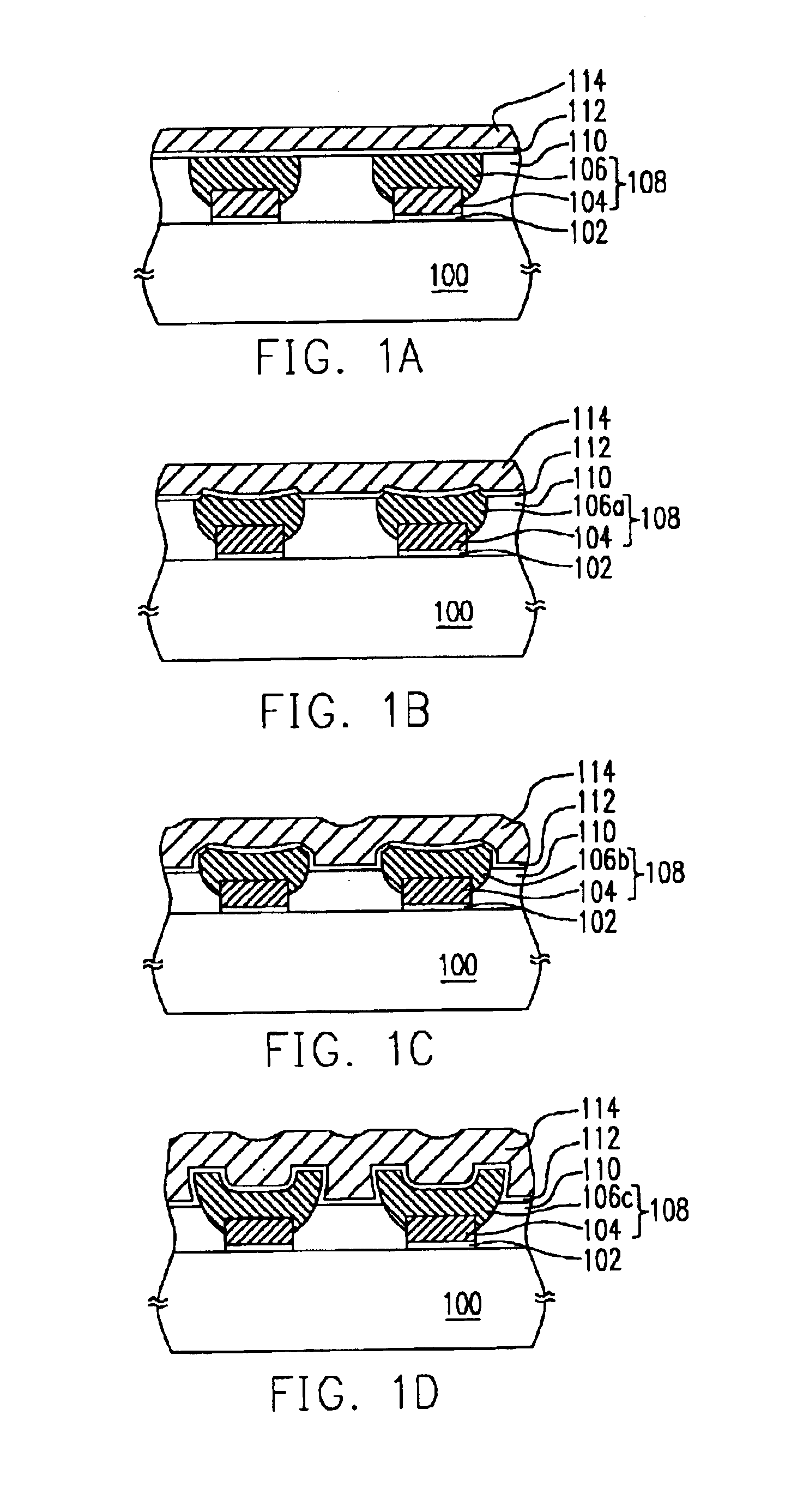

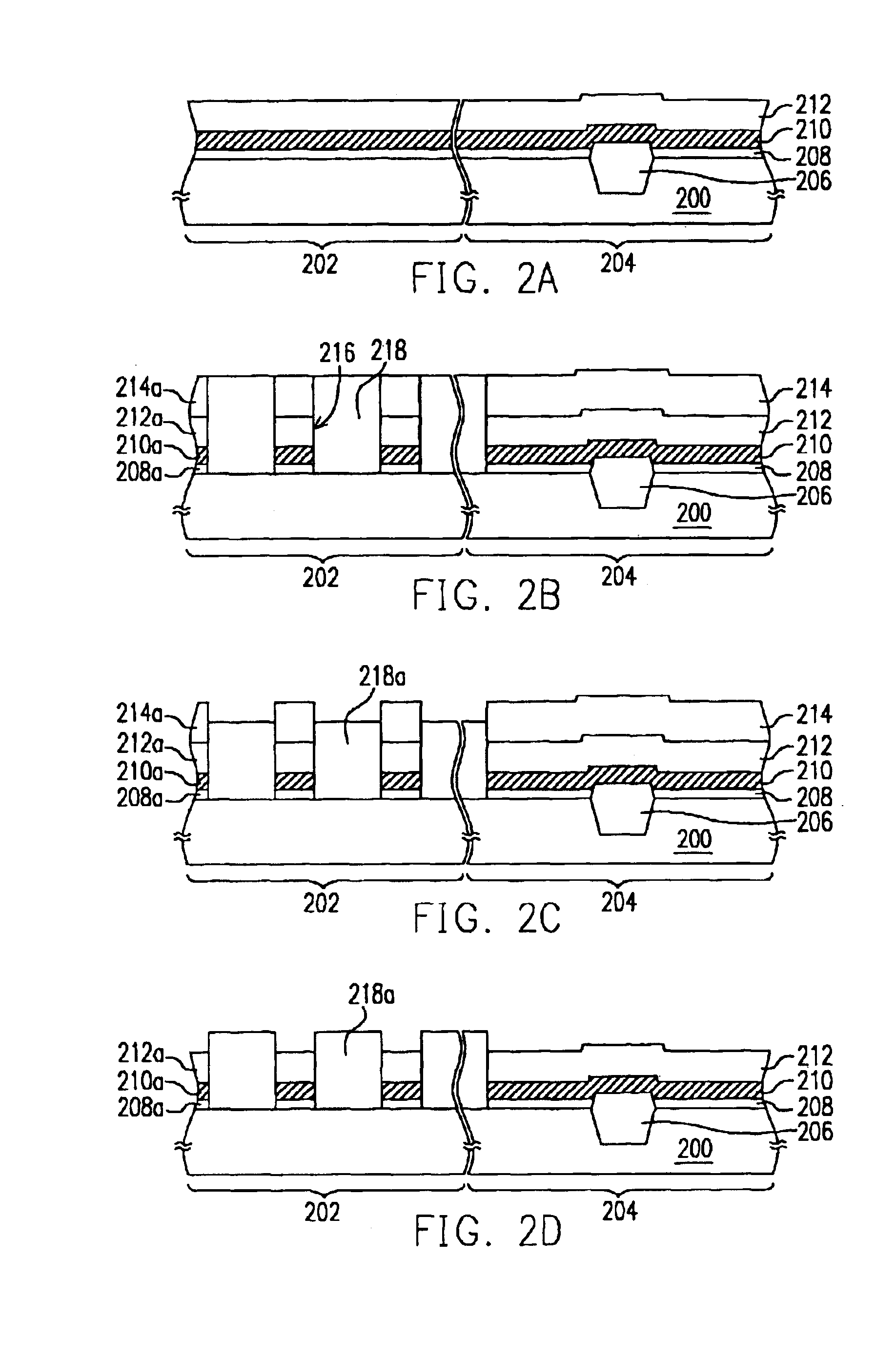

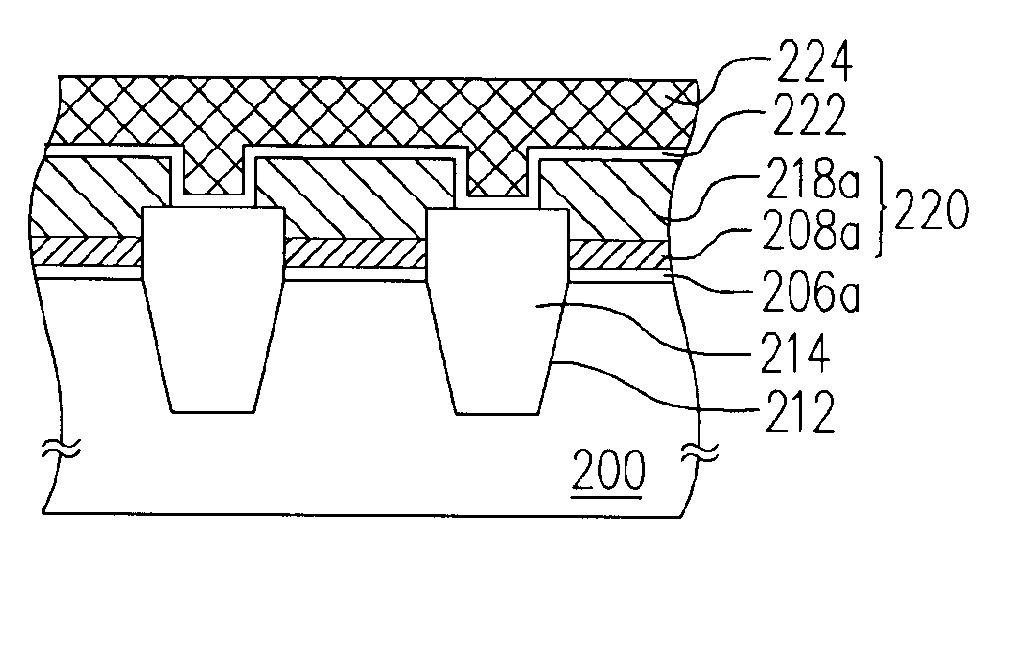

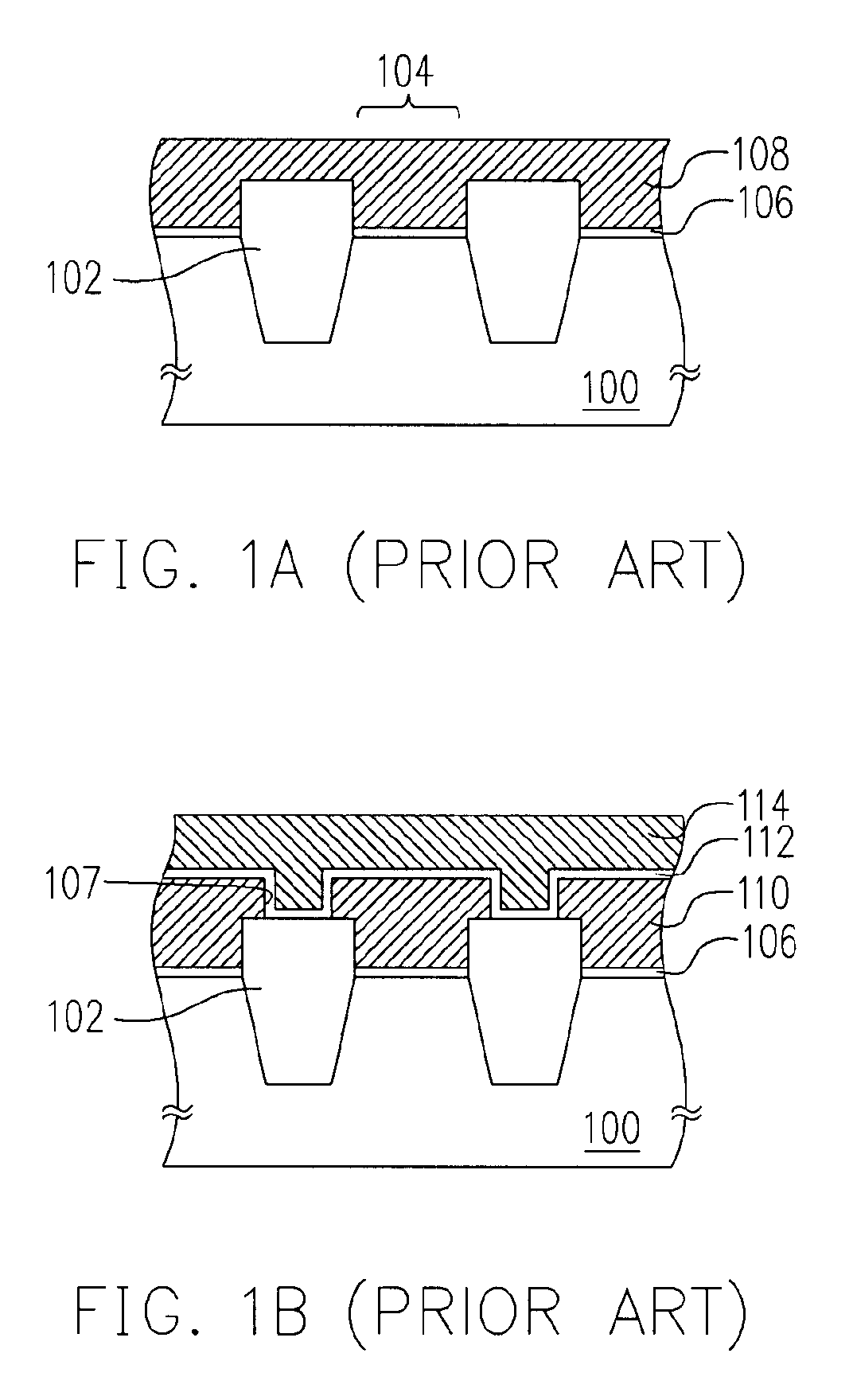

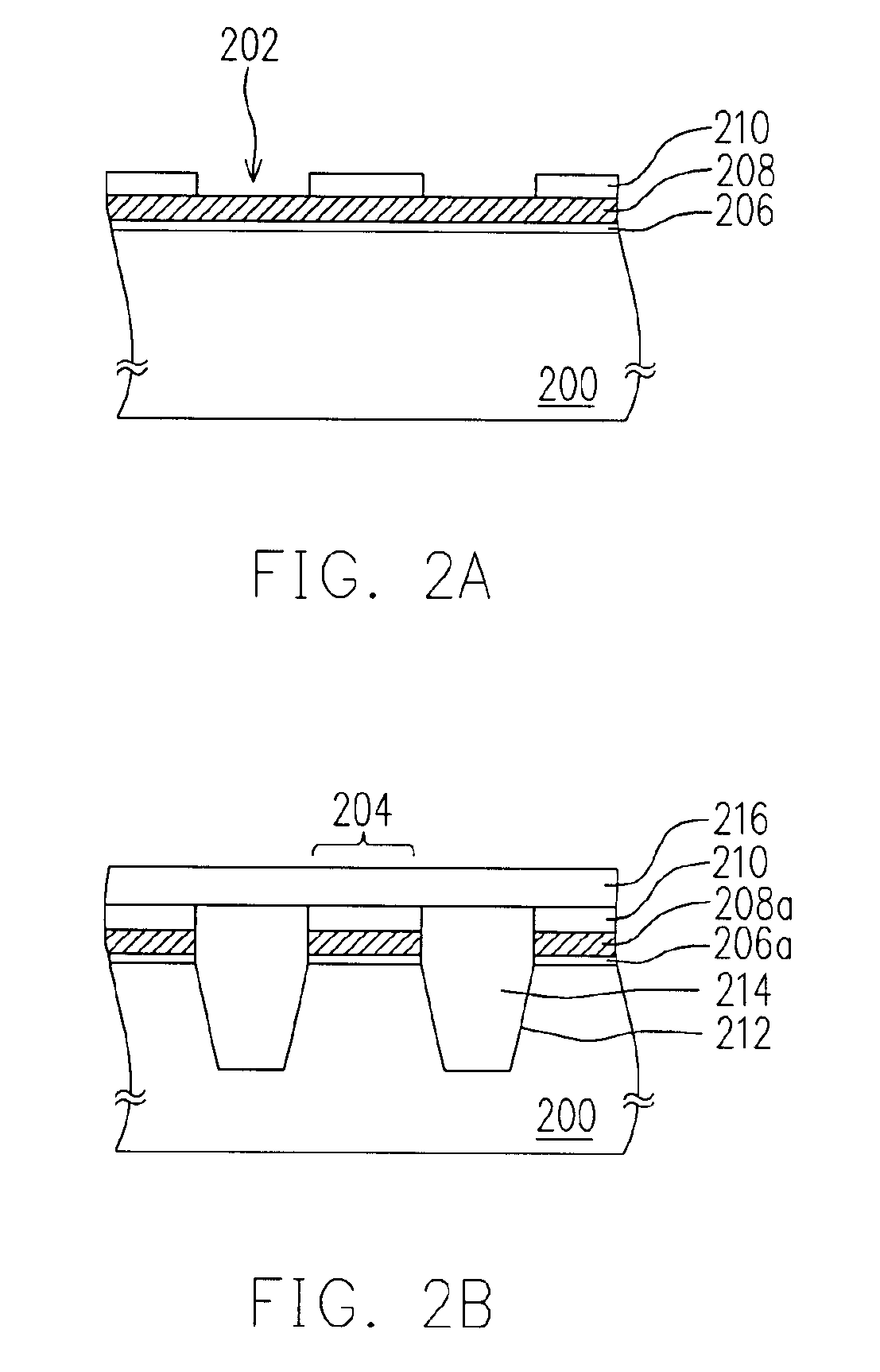

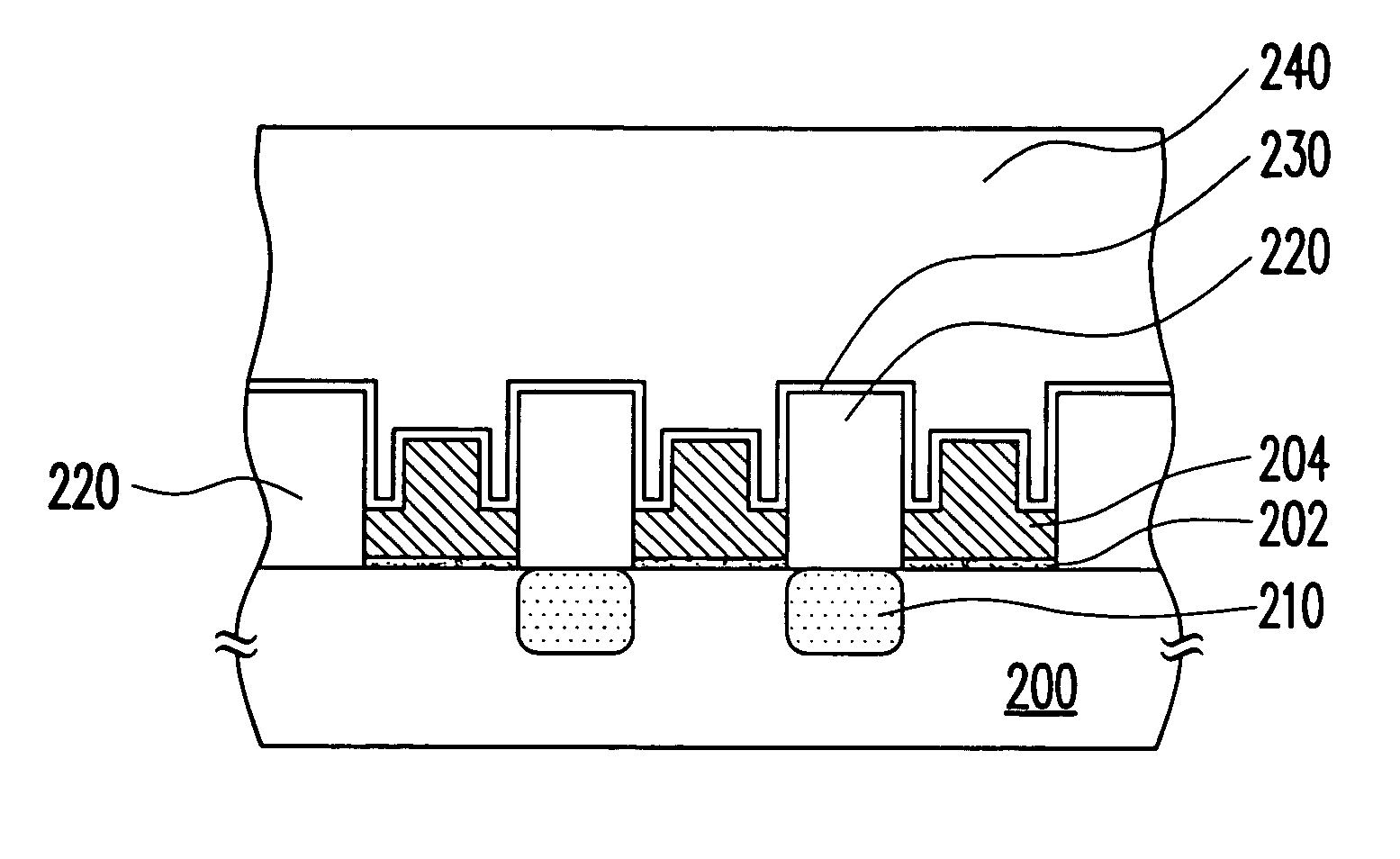

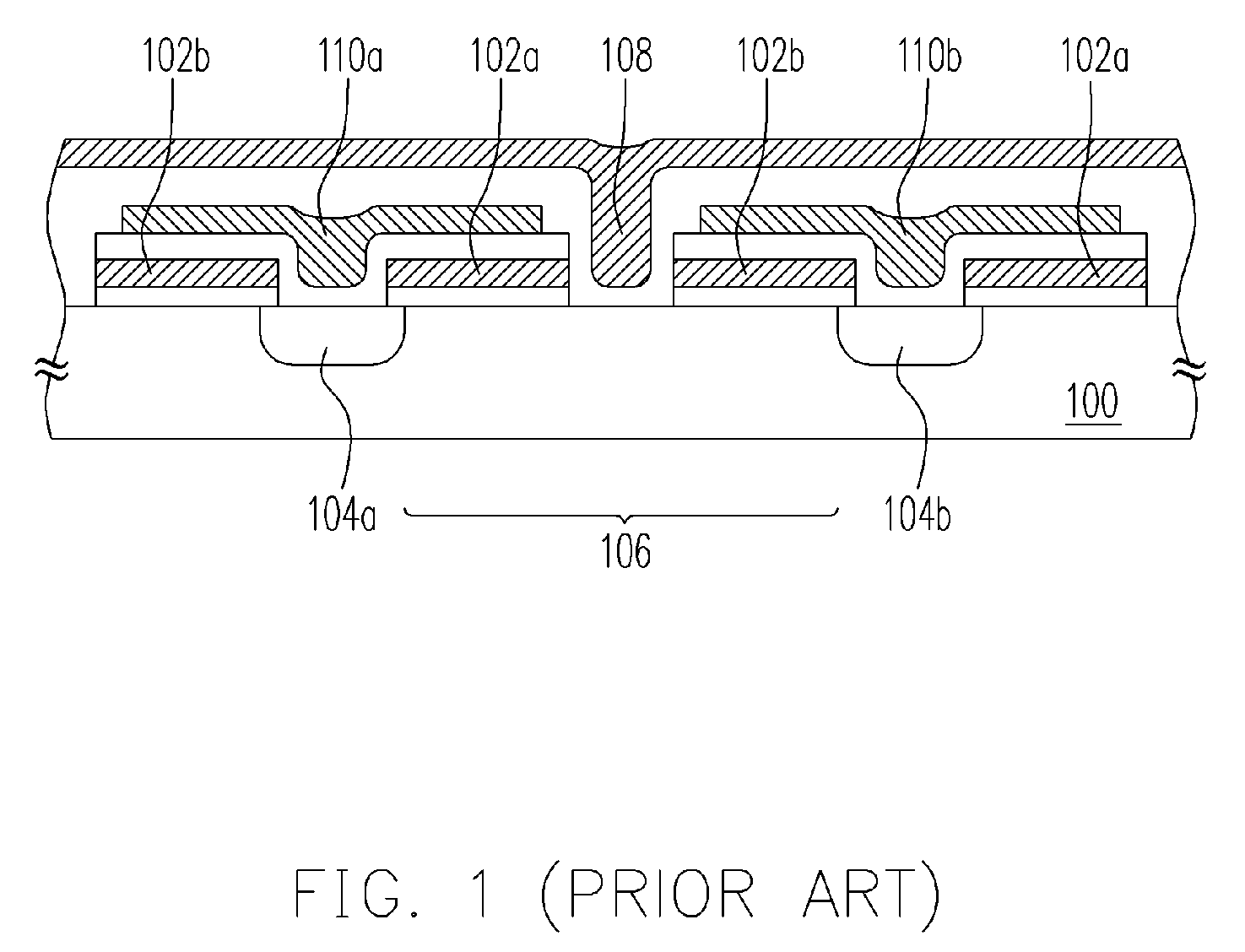

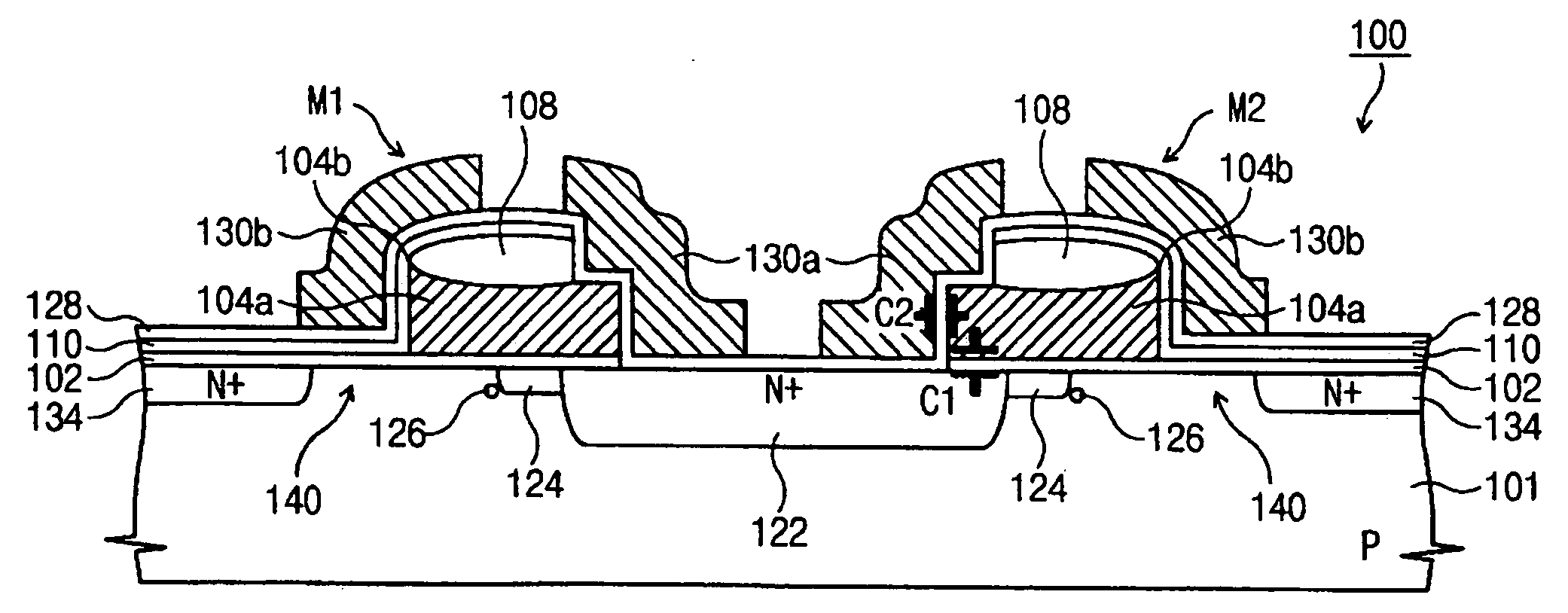

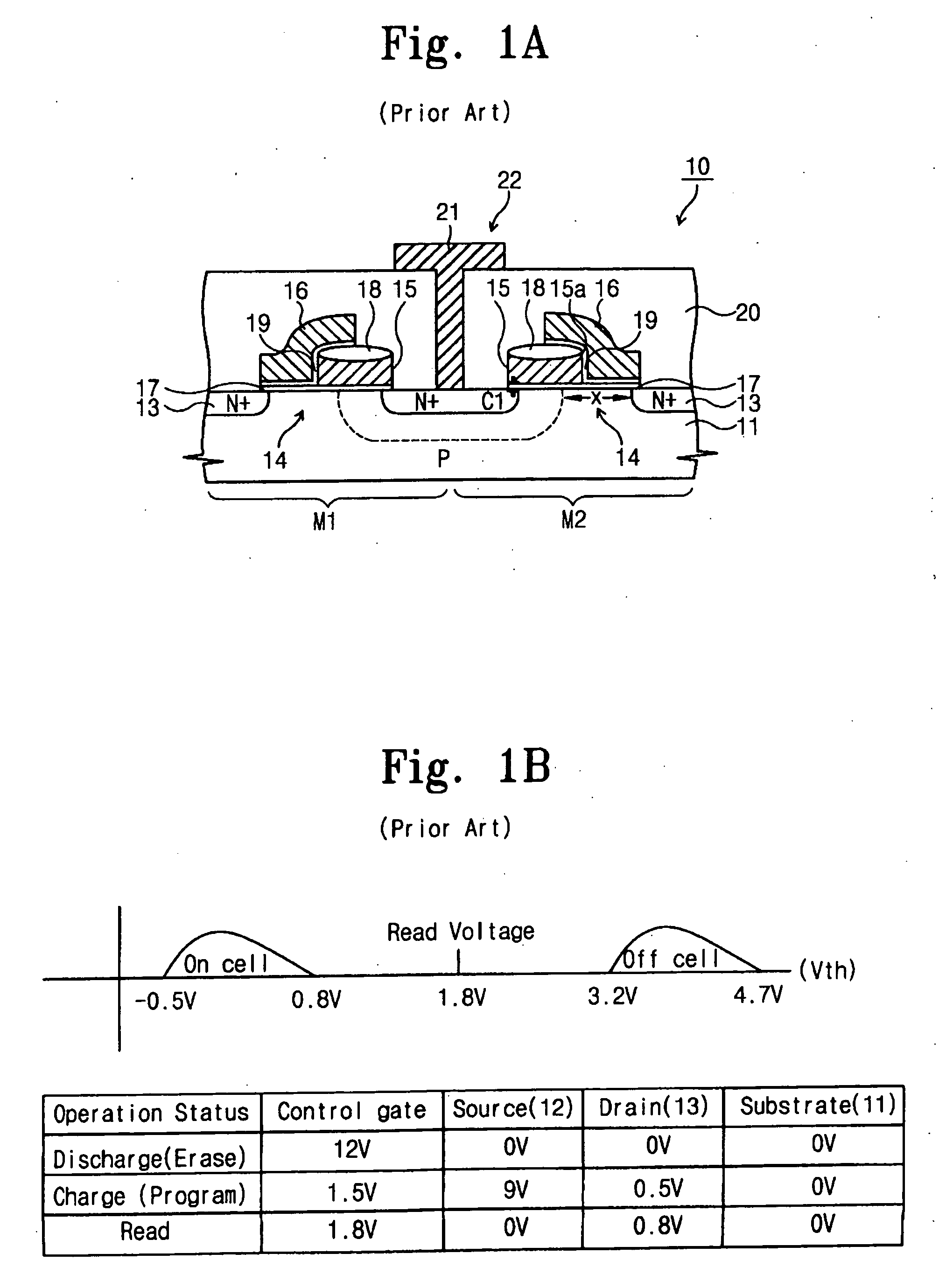

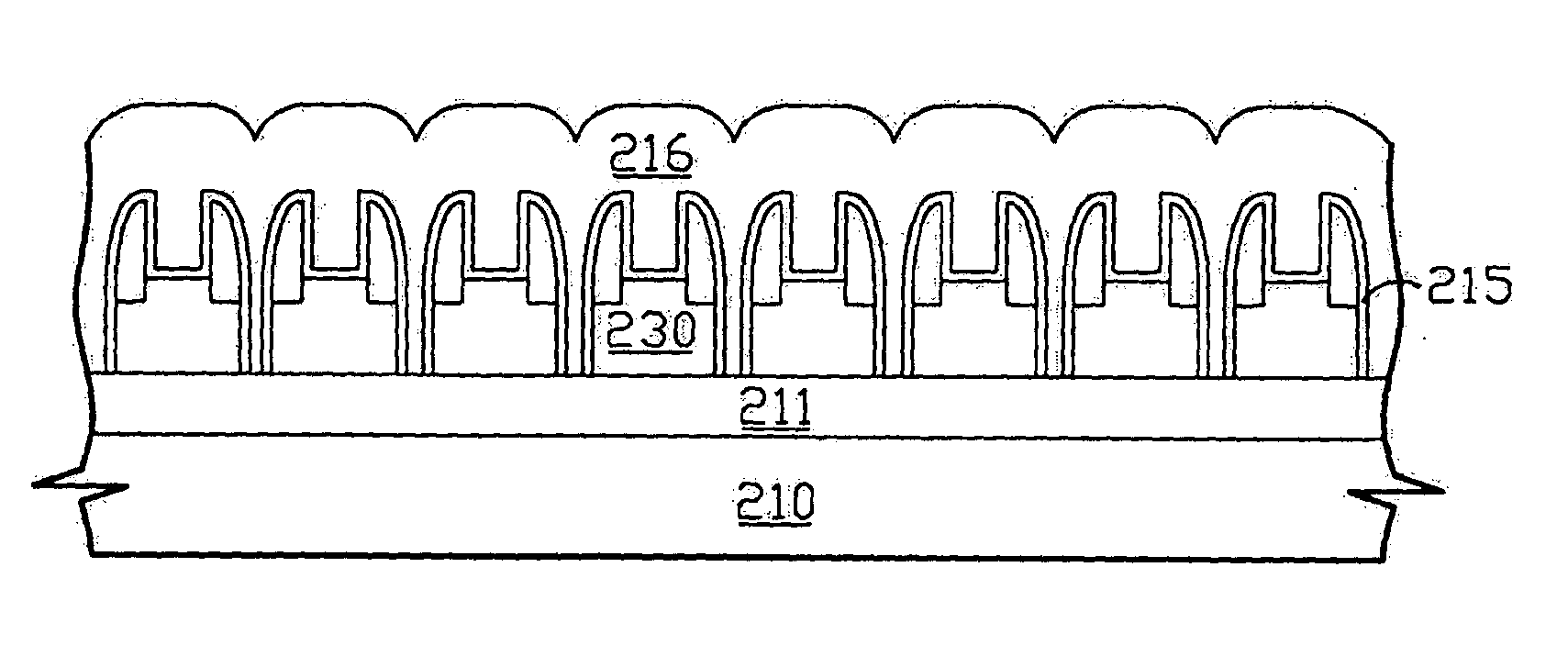

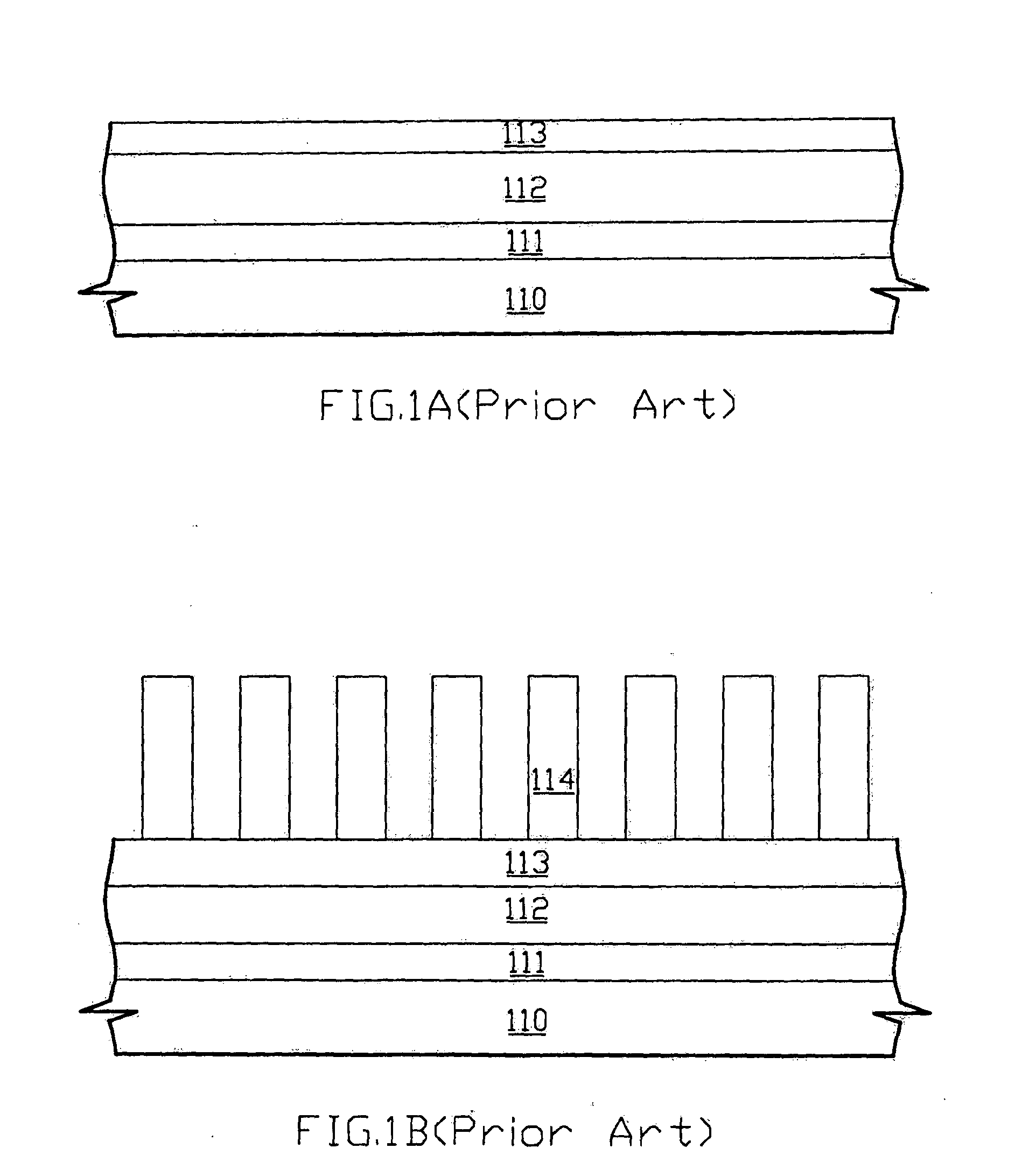

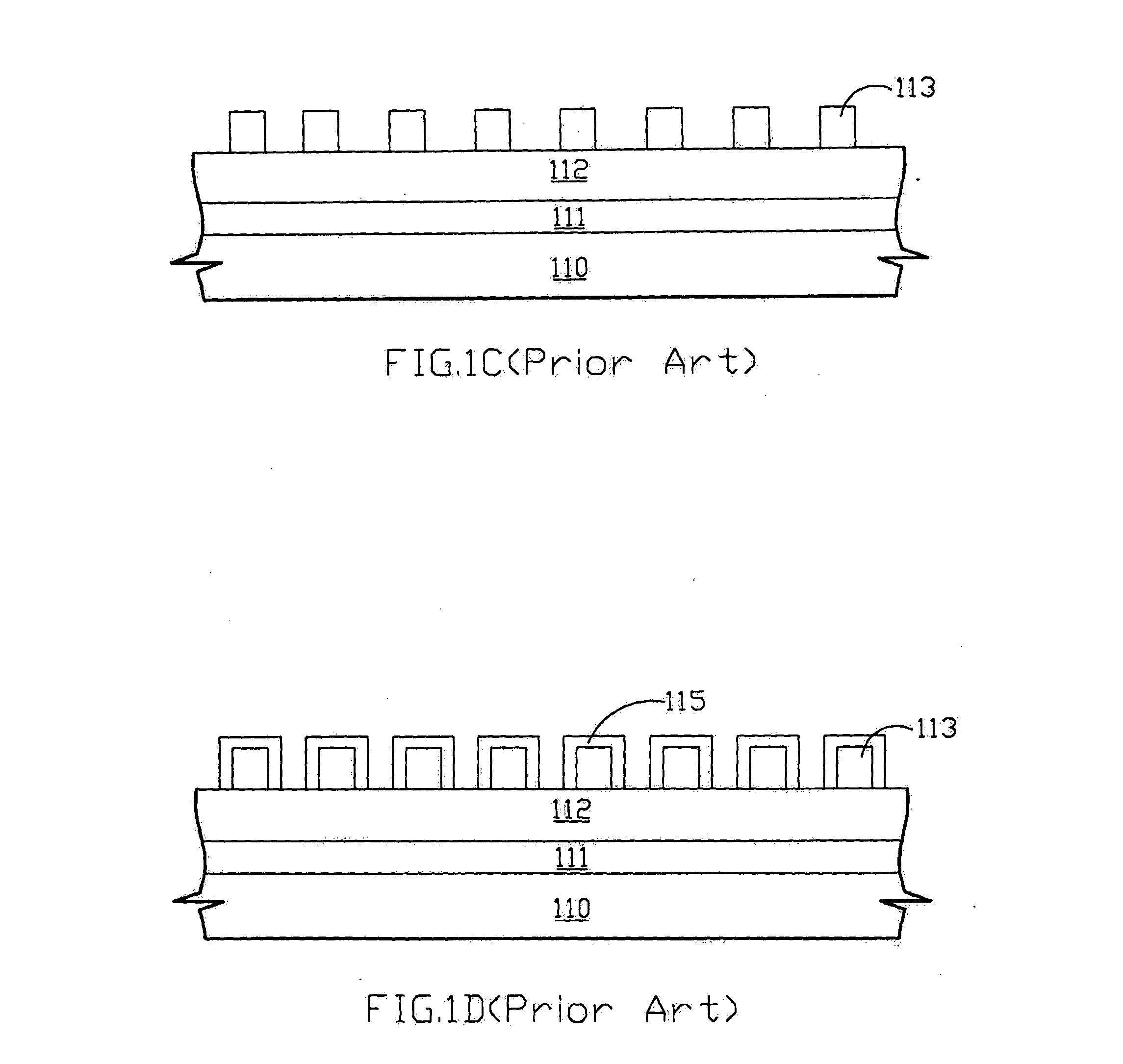

[split gate flash memory cell and manufacturing method thereof]

ActiveUS20050006691A1Raise ratioRaise the ratioTransistorSolid-state devicesElectrical and Electronics engineeringDielectric layer

A split gate flash memory cell includes a substrate having a device isolation structure; a selective gate structure disposed on the substrate; an interlayer dielectric layer having an opening disposed on the substrate, wherein the opening exposes a portion of the selective gate structure, the substrate and the device isolation structure; a floating gate disposed in the opening and extended to cover a surface of the interlayer dielectric layer; a tunneling di-electric layer disposed between the floating gate and the selective gate structure; a gate dielectric layer disposed between the floating gate and the control gate; a source region disposed in the substrate on one side of the control gate that is not adjacent to the selective gate structure, and a drain region disposed in the substrate on one side of the selective gate that is not adjacent to the control gate.

Owner:POWERCHIP SEMICON MFG CORP

Split gate non-volatile memory devices and methods of forming same

InactiveUS7315057B2Improve gate coupling ratioImprove efficiencyTransistorSolid-state devicesCoupling ratioEngineering

Non-volatile memory devices and methods for fabricating non-volatile memory devices are disclosed. More specifically, split gate memory devices are provided having frameworks that provide increased floating gate coupling ratios, thereby enabling enhanced programming and erasing efficiency and performance.

Owner:SAMSUNG ELECTRONICS CO LTD

Method of fabricating a flash memory

ActiveUS6984559B2Improve gate coupling ratioImprove device performanceTransistorSolid-state devicesGate dielectricOptoelectronics

A method of fabricating a flash memory is provided. A substrate having several device isolation structures for defining an active region is provided. A tunneling dielectric layer and a patterned mask layer are formed over the active region. A portion of each device isolation structure is removed to form a plurality of trenches. A dielectric layer is formed over the substrate and a sacrificial layer is filled the trenches. A portion of the dielectric layer is removed using the sacrificial layer as a self-aligned mask. The patterned mask layer is removed and a conductive layer that exposed the top section of the sacrificial layers is formed over the substrate. After removing the sacrificial layer, an inter-gate dielectric layer and a control gate are formed over the substrate. A source region and a drain region are formed in the substrate on each side of the control gate.

Owner:POWERCHIP SEMICON MFG CORP

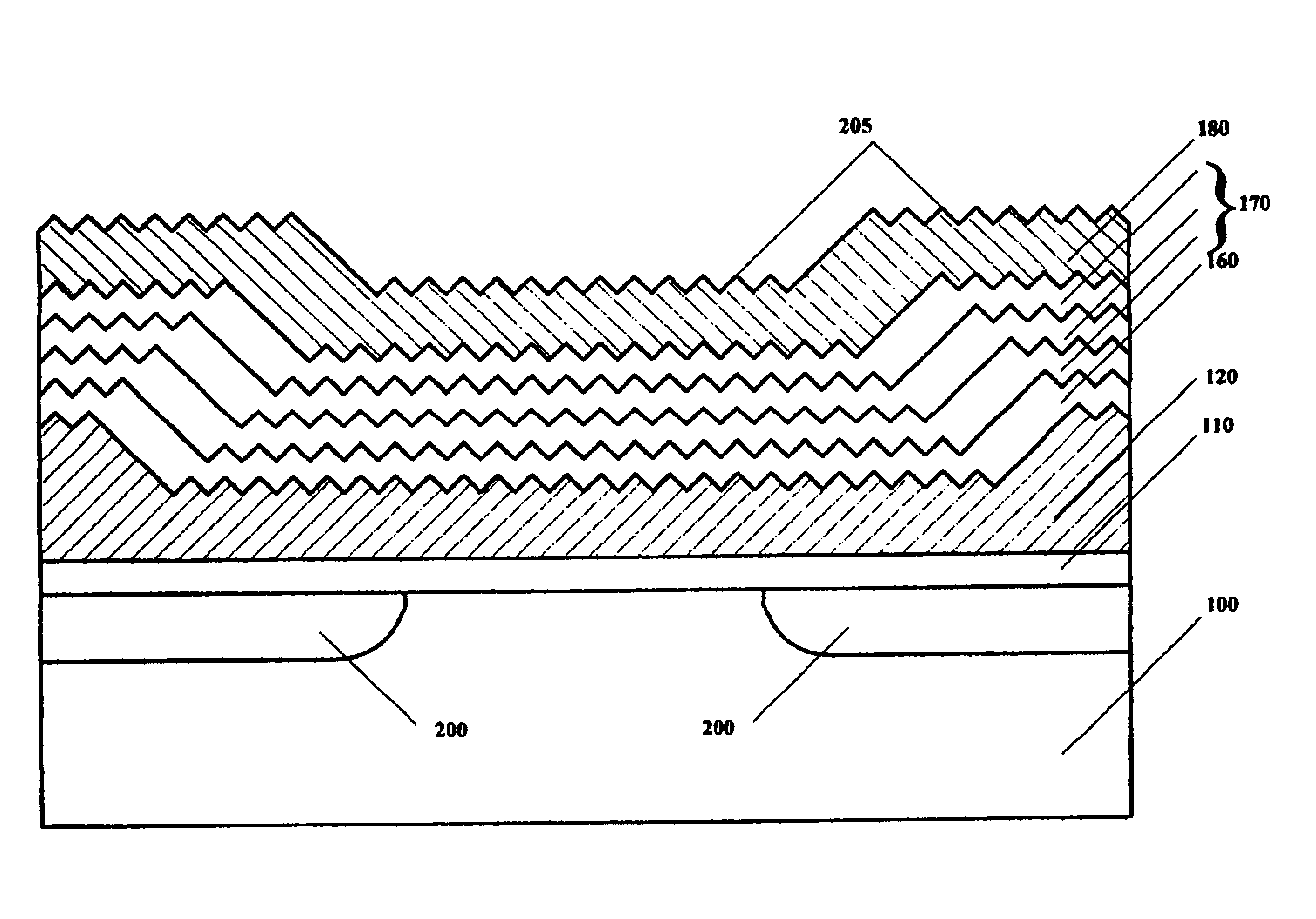

Memory cell

InactiveUS20060157774A1Improve integrationEfficient in operationTransistorSemiconductor/solid-state device manufacturingPhysicsDielectric layer

A memory cell is provided as including a substrate, a tunneling dielectric layer, a charge trapping layer, an inter-gate dielectric layer, a metal gate layer, and a source / drain region. The source / drain region is formed in the substrate besides the gate structure that includes the tunneling dielectric layer, charge trapping layer, inter-gate dielectric layer, and metal gate layer. The tunneling dielectric layer is formed on the substrate, the charge trapping layer is formed on the tunneling dielectric layer, the inter-gate dielectric layer is formed on the charge trapping layer, and the metal gate layer is formed on the inter-gate dielectric layer.

Owner:MACRONIX INT CO LTD

Flash memory unit, flash memory unit array and mfg. method thereof

InactiveCN1591873AImprove gate coupling ratioImprove operating speedSolid-state devicesSemiconductor/solid-state device manufacturingComputer architectureGate dielectric

The present invention discloses a flash memory storage unit, flash memory storage unit array and its making method. Said flash memory storage unit array consists of substrate, series-connected several storage unit structures and source region / drain region. Every storage unit structure is formed from stack gate structure consisting of selection gate dielectric layer, selection gate and top cover layer; gap wall placed on the side wall of selection gate; control gate which is placed on one side of the stack gate structure and is connected with stack gate structure; floating gate placed between control gate and substrate; intergate dielectric layer placed between the control gate and floating gate; tunneling dielectric layer placed between floating gate and substrate and control gate and source region / drain region respectively placed in the most external side of storage unit array and substrate of one side of stack gate structure.

Owner:POWERCHIP SEMICON CORP

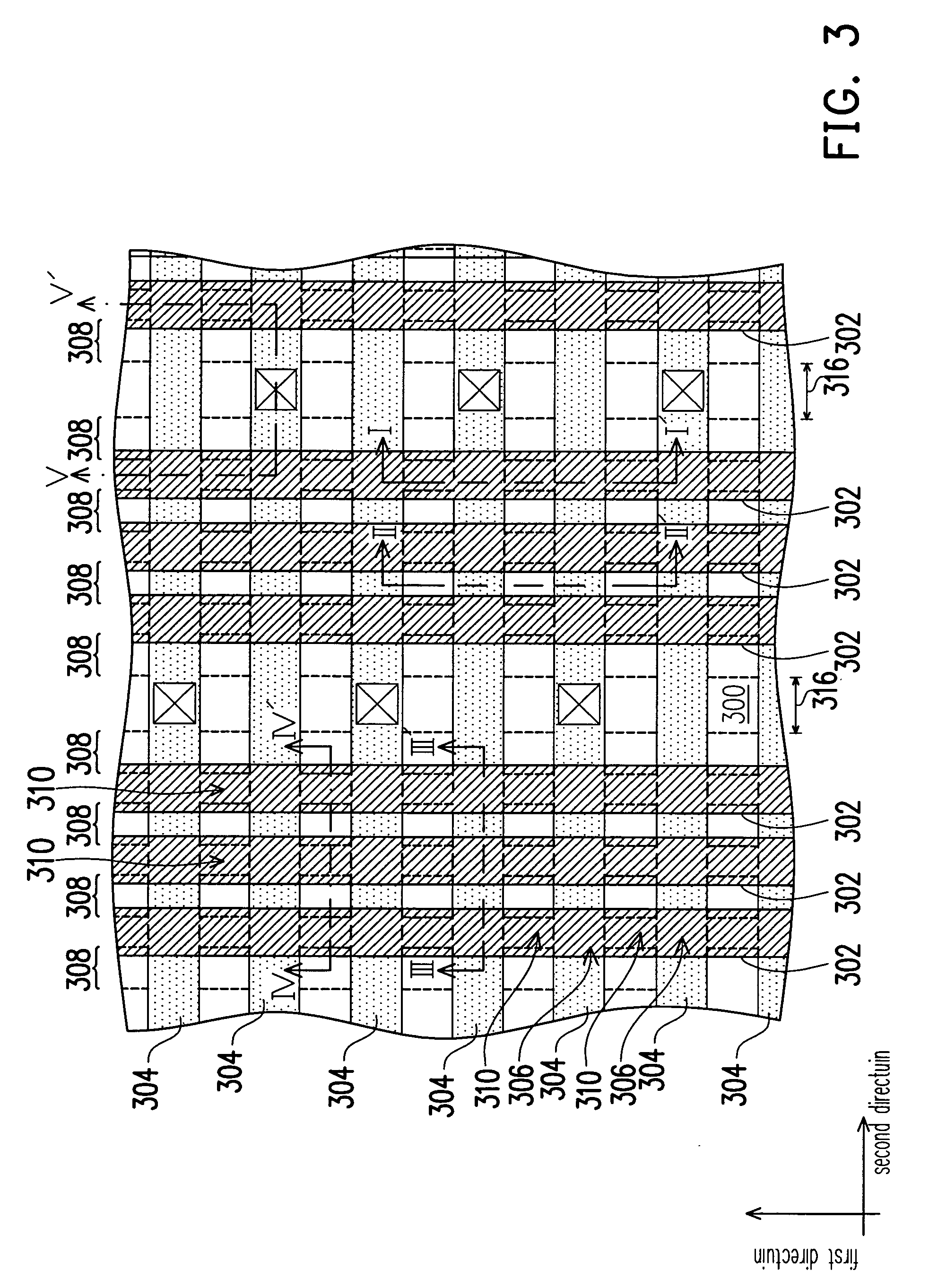

Flash memory and fabrication method thereof

InactiveUS20060284267A1Reduce contact areaImprove gate coupling ratioSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricIsolation layer

A flash memory comprises a substrate, control gates, doped regions, an isolation layer, isolation structures, floating gates, tunneling dielectric layers and inter-gate dielectric layers. The control gates are arranged over the substrate with a first direction, and the doped regions are arranged within the substrate with a second direction. The isolation layers are disposed between the control gates and the doping regions, and the isolation structures are disposed within the substrate where the doped regions and the control gates do not overlap. Furthermore, the floating gates are disposed between the control gates and the substrate that is not covered by the isolation layers. The tunneling dielectric layers are disposed between the substrate and the floating gates. The inter-gate dielectric layers are disposed between the control gates and the floating gates.

Owner:MACRONIX INT CO LTD

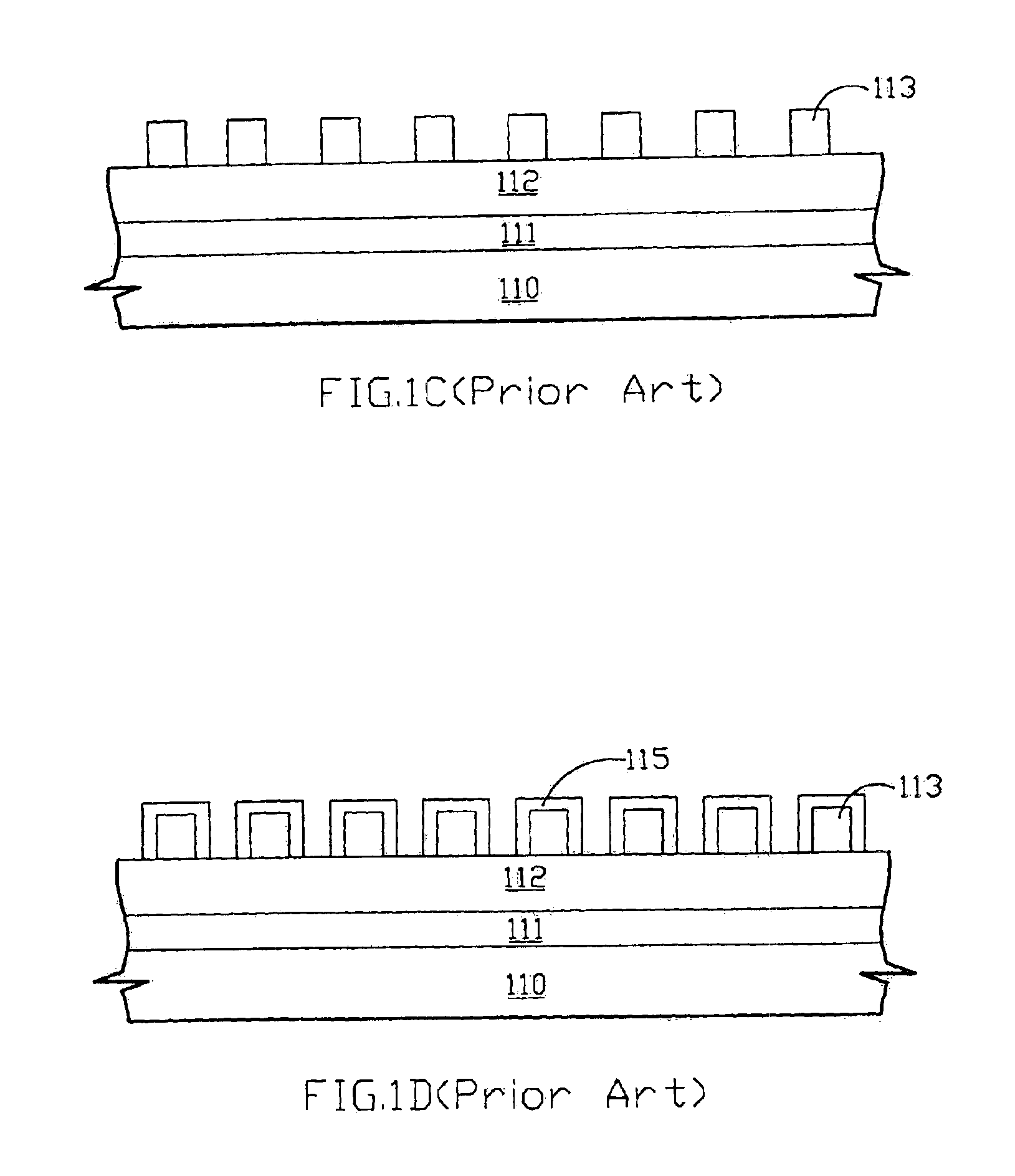

Flash gate stack notch to improve coupling ratio

InactiveUS20060081908A1Improve gate coupling ratioTransistorSemiconductor/solid-state device manufacturingCapacitanceCoupling ratio

A semiconductor flash memory device with increased gate coupling ratio and a method of preparing this flash memory device. The semiconductor flash memory device includes a notched floating polysilicon gate. The notches are at the interface between the floating polysilicon layer and the tunneling dielectric layer. The notches reduce the capacitance between the floating polysilicon and the channel region. The reduced capacitance results in the increased gate coupling ratio. The degree of capacitance reduction, which affects the gate coupling ratio increase, is controlled by the width of the notches. The floating polysilicon gate etch includes a first anisotropic etch and a second isotropic etch. The widths of the notches are controlled by the etch time of the isotropic etch.

Owner:APPLIED MATERIALS INC

Flash memory

ActiveUS20060175654A1Increasing gate couple ratio and integrationGate couple ratioTransistorSolid-state devicesGate dielectricEngineering

A method for fabricating a flash memory is described. A mask layer having openings to expose a portion of the substrate is formed on the substrate. A tunneling dielectric layer is formed at the bottom surface of the openings. Conductive spacers are formed on the sidewalls of the openings. The conductive spacers are patterned to form a plurality of floating gates. A plurality of buried doped regions is formed in the substrate under the bottom surface of the openings. An inter-gate dielectric layer is formed over the substrate. A plurality of control gates is formed over the substrate to fill the openings. The mask layer is removed to form a plurality of memory units. A plurality of source regions and drain regions are formed in the substrate beside the memory units.

Owner:POWERCHIP SEMICON MFG CORP

Separated grid flash memory unit and its mfg. method

InactiveCN1591872AImprove reliabilityExtend your lifeSolid-state devicesSemiconductor/solid-state device manufacturingDielectric layerElectrical and Electronics engineering

The present invention relates to a separate gate flash memory storage unit. It is includes substrate with element-isolating structure; selection gate structure placed on the substrate; interlaminar dielectric layer placed on the substrate and having opening, said opening expose partial selection gate structure, substrate and element-isolating structure; floating gate which is placed in the opening and whose part is extended to interlaminar dielectric layer surface; tunneling dielectric layer placed between floating gate and substrate; control gate which is placed in said opening, used for filling said opening and extented to the upper portion of selection gate structure; intergate dielectric layer placed between floating gate and control gate; source region placed in the substrate of one side of control gate which is not adjacent to selection gate structure and drain region placed in the substrate of one side of selection gate which is not adjacent to control gate.

Owner:POWERCHIP SEMICON CORP

Split gate flash memory cell and manufacturing method thereof

ActiveUS7358134B2Raise the ratioReliability of the tunneling dielectric layer is thereby increasedSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricDielectric layer

A split gate flash memory cell includes a substrate having a device isolation structure; a selective gate structure disposed on the substrate; an interlayer dielectric layer having an opening disposed on the substrate, wherein the opening exposes a portion of the selective gate structure, the substrate and the device isolation structure; a floating gate disposed in the opening and extended to cover a surface of the interlayer dielectric layer; a tunneling dielectric layer disposed between the floating gate and the selective gate structure; a gate dielectric layer disposed between the floating gate and the control gate; a source region disposed in the substrate on one side of the control gate that is not adjacent to the selective gate structure, and a drain region disposed in the substrate on one side of the selective gate that is not adjacent to the control gate.

Owner:POWERCHIP SEMICON MFG CORP

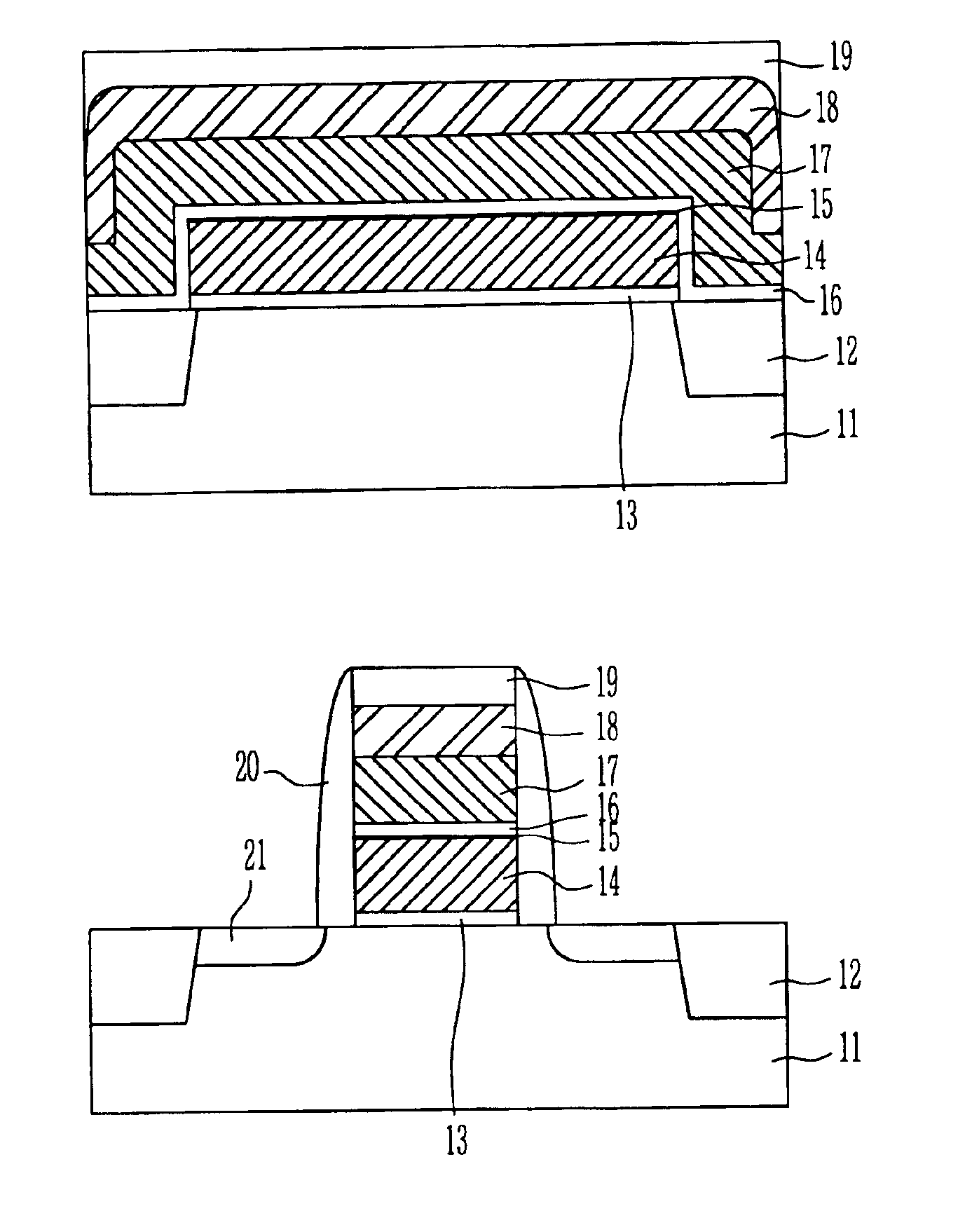

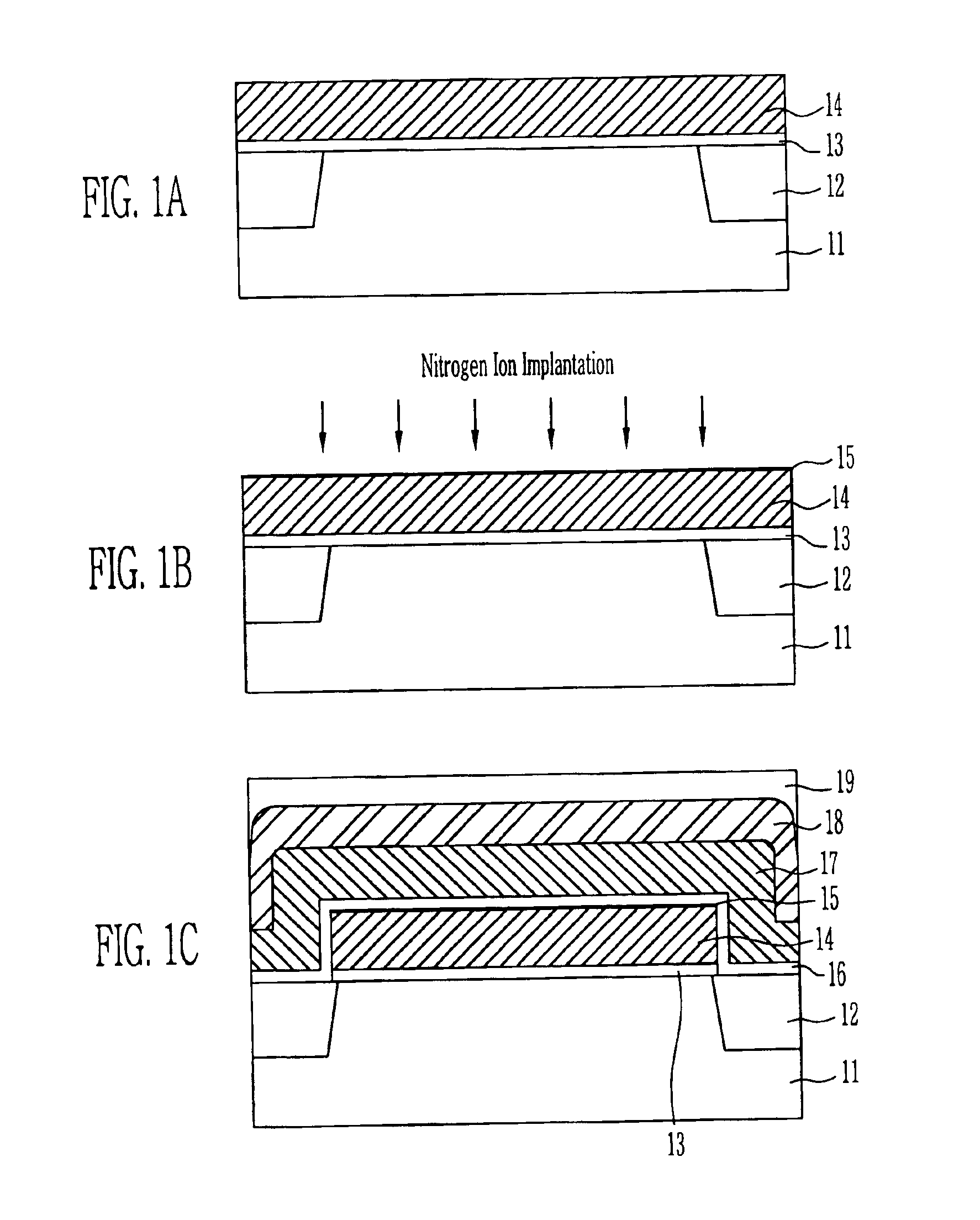

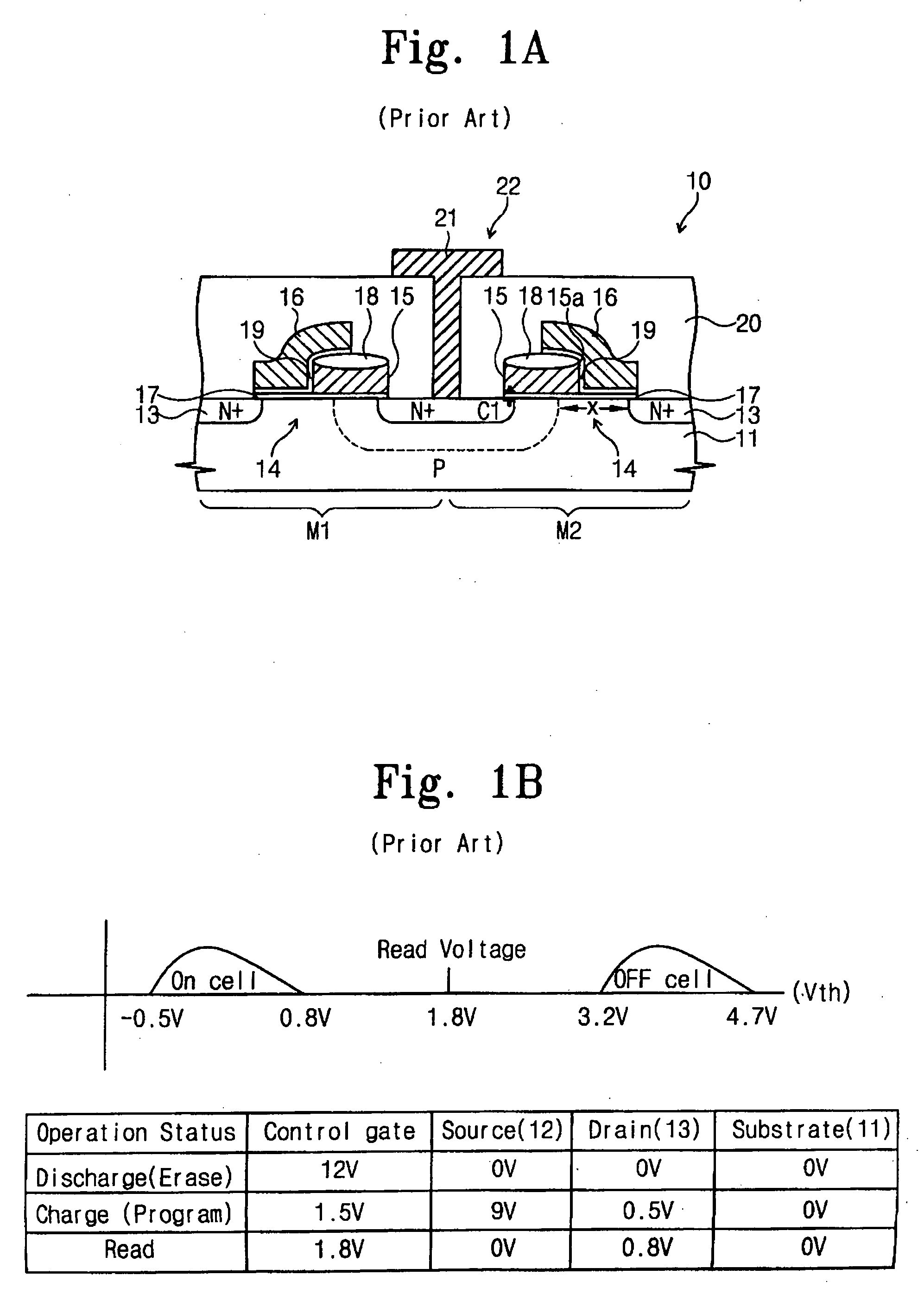

Method of manufacturing a flash memory cell

InactiveUS6900096B2Preventing increase in thickness of dielectricIncreasing the thicknessTransistorSolid-state devicesIonNitrogen

The present invention relates to a method of manufacturing a flash memory cell capable of preventing an oxidation of a dielectric film between a floating gate and a control gate, in a manner that a polysilicon film for floating gate is deposited, nitrogen ions are injected to make amorphous and contaminate the surface of the polysilicon film.

Owner:SK HYNIX INC

Method of fabricating device

InactiveUS20100093142A1Improve gate coupling ratioAvoid problemsSolid-state devicesSemiconductor/solid-state device manufacturingOxideNitride

Owner:POWERCHIP SEMICON CORP

Split gate non-volatile memory devices and methods of forming the same

InactiveUS7602008B2Improve gate coupling ratioImprove efficiencyTransistorSolid-state devicesCoupling ratioEngineering

Non-volatile memory devices and methods for fabricating non-volatile memory devices are disclosed. More specifically, split gate memory devices are provided having frameworks that provide increased floating gate coupling ratios, thereby enabling enhanced programming and erasing efficiency and performance.

Owner:SAMSUNG ELECTRONICS CO LTD

Split gate flash memory cell

InactiveUS6897521B2Raise the ratioReliability of the tunneling dielectric layer is thereby increasedTransistorSolid-state devicesGate dielectricDielectric layer

A split gate flash memory cell includes a substrate having a device isolation structure; a selective gate structure disposed on the substrate; an interlayer dielectric layer having an opening disposed on the substrate, wherein the opening exposes a portion of the selective gate structure, the substrate and the device isolation structure; a floating gate disposed in the opening and extended to cover a surface of the interlayer dielectric layer; a tunneling dielectric layer disposed between the floating gate and the selective gate structure; a gate dielectric layer disposed between the floating gate and the control gate; a source region disposed in the substrate on one side of the control gate that is not adjacent to the selective gate structure, and a drain region disposed in the substrate on one side of the selective gate that is not adjacent to the control gate.

Owner:POWERCHIP SEMICON MFG CORP

Method for producing nonvolatile memory

InactiveCN101064284AReduce photomask countReduce manufacturing costSemiconductor/solid-state device manufacturingDielectric layerNon-volatile memory

A preparing method of nonvolatile memory is disclosed. Firstly, providing a basis with several separation configurations which extrude the surface of basis, the first mask layer is formed on basis between separation configurations. The second mask layer is formed on the basis. Then, the second mask layer and the first mask layer are patterned to form several openings; these openings expose part of the basis and surface of the separation configurations. Then forming the tubular floating grid which through the dielectric layer and possesses hollows, said tubular floating grid is at the position that adjacent separation configurations and the first mask layer encircle. Then the grip gap dielectric layer is formed on the basis. Then control gate electrode is formed on the basis to fill the opening.

Owner:POWERCHIP SEMICON CORP

Memory and manufacturing method thereof

ActiveCN106409837AImprove reliabilityHigh densitySolid-state devicesSemiconductor devicesIsolation layerElectrical and Electronics engineering

The present invention discloses a memory and a manufacturing method thereof. A memory element comprises a first insulating layer, a second insulating layer, an isolation layer, a floating gate electrode, a control gate electrode, a channel layer and a tunneling oxide layer. The second insulating layer is adjacent to and parallel with the first insulating layer and defines an interlayer space with the first insulating layer, the isolation layer is located in the interlayer space, and the included angle of the isolation layer and the first insulating layer is a non-flat angle. The interlayer space is isolated into a first concave chamber and a second concave chamber, the floating gate electrode is located in the first concave chamber, and the control gate electrode is located in the second concave chamber. The channel layer is located at the outer side of the opening of the first concave chamber, the included angle of the channel layer and the first insulating layer is a non-flat angle, and the tunneling oxide layer is located between the channel layer and the floating gate electrode.

Owner:MACRONIX INT CO LTD

Flash memory

ActiveUS7196371B2Increasing gate couple ratio and integrationGate couple ratioTransistorSolid-state devicesGate dielectricEngineering

A method for fabricating a flash memory is described. A mask layer having openings to expose a portion of the substrate is formed on the substrate. A tunneling dielectric layer is formed at the bottom surface of the openings. Conductive spacers are formed on the sidewalls of the openings. The conductive spacers are patterned to form a plurality of floating gates. A plurality of buried doped regions is formed in the substrate under the bottom surface of the openings. An inter-gate dielectric layer is formed over the substrate. A plurality of control gates is formed over the substrate to fill the openings. The mask layer is removed to form a plurality of memory units. A plurality of source regions and drain regions are formed in the substrate beside the memory units.

Owner:POWERCHIP SEMICON MFG CORP

Flash memory and manufacturing method thereof

ActiveUS20060275985A1The process steps are simpleLow production costSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricOptoelectronics

A method for manufacturing flash memory is provided. A tunneling dielectric layer, a conductive layer and a patterned mask layer that exposes a portion of the conductive layer are formed on a substrate. An oxide layer is formed on the exposed conductive layer so that the conductive layer is partitioned through the oxide layer into blocks. The oxide layer is removed and an inter-gate dielectric layer is formed in the opening. A control gate that completely fills the opening is formed. A cap layer is formed over the control gate. The mask layer is then removed. Using the cap layer as a mask, a portion of the conductive layer is removed to form two floating gates under the control gate. An insulating layer is formed on the substrate. Source / drain regions are formed in the substrate on the respective sides of the control gate.

Owner:POWERCHIP SEMICON MFG CORP

![[split gate flash memory cell and manufacturing method thereof] [split gate flash memory cell and manufacturing method thereof]](https://images-eureka.patsnap.com/patent_img/1c49a4bd-1be8-4073-b021-faf3f1642f59/US20050006691A1-20050113-D00000.png)

![[split gate flash memory cell and manufacturing method thereof] [split gate flash memory cell and manufacturing method thereof]](https://images-eureka.patsnap.com/patent_img/1c49a4bd-1be8-4073-b021-faf3f1642f59/US20050006691A1-20050113-D00001.png)

![[split gate flash memory cell and manufacturing method thereof] [split gate flash memory cell and manufacturing method thereof]](https://images-eureka.patsnap.com/patent_img/1c49a4bd-1be8-4073-b021-faf3f1642f59/US20050006691A1-20050113-D00002.png)