Minimum time controller with controllable serial capacitor compensation and its control method

A technology of series capacitor compensation and time controller, applied in reactive power compensation, reactive power adjustment/elimination/compensation, etc., can solve problems affecting dynamic response time, reduction, and many constraints

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

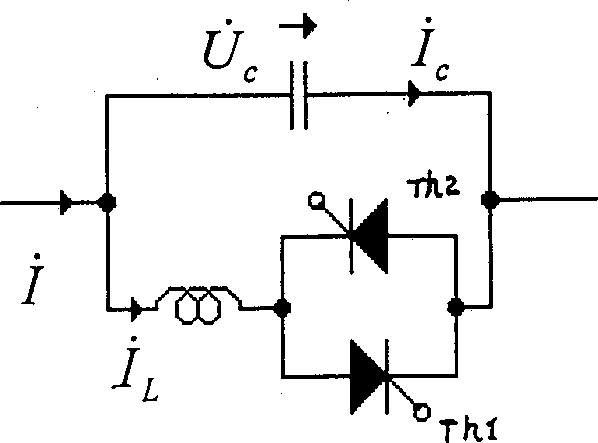

Method used

Image

Examples

Embodiment Construction

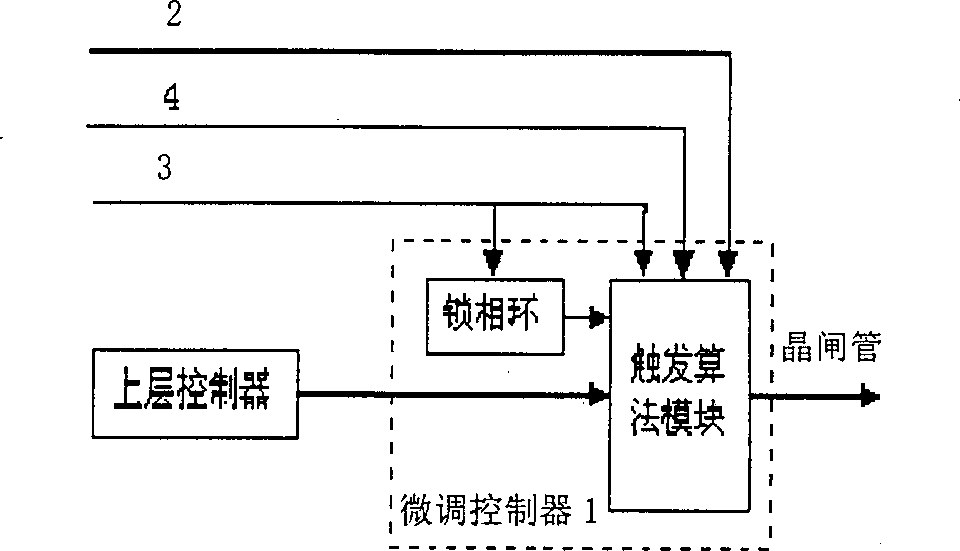

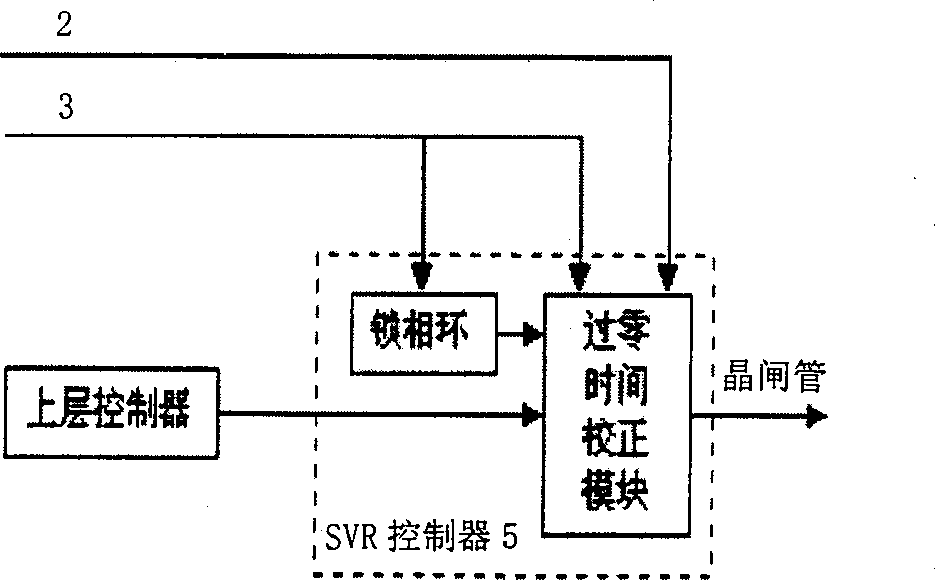

[0029] please see Figure 4 with Figure 5 , the connection relationship of each box is as above. Digital signal processor DSP adopts chip TMS320C32, A / D data acquisition card adopts chip AD7874X2, EEPROM adopts chip SST29010, SRAM adopts chip ISSI128K*8, dual-port RAM adopts chip IDT133*2, logic controller adopts chip Altera max7196, bus buffer The device adopts the chip 16245*2, and the serial port adopts RS232, and the connection method between the pins is the conventional method stipulated in the use of the chip. The key is: In addition to using the data acquisition card A / D to collect from the scene and then transmit the line current 3 expressed in digital quantities as a synchronization signal through the bus interface 3XBUS, the data acquisition card A / D does not need to collect other system power , it only needs to calculate the parameters of the controllable series compensation itself, so the algorithm is simple and fast, and the dynamic response time is shortened. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More