Multiplier and shift device using signed digit representation

A multiplier and digital technology, applied in the field of multipliers and shifters, can solve the problems of occupying a large silicon chip area, large structural volume, and increased cost.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0109] Embodiments of the present invention will be described in detail below with reference to the accompanying drawings.

[0110] While reducing the amount of hardware, thereby reducing the area required for the multiplier, one aspect of the invention is to minimize the hardware involved in the shifting means.

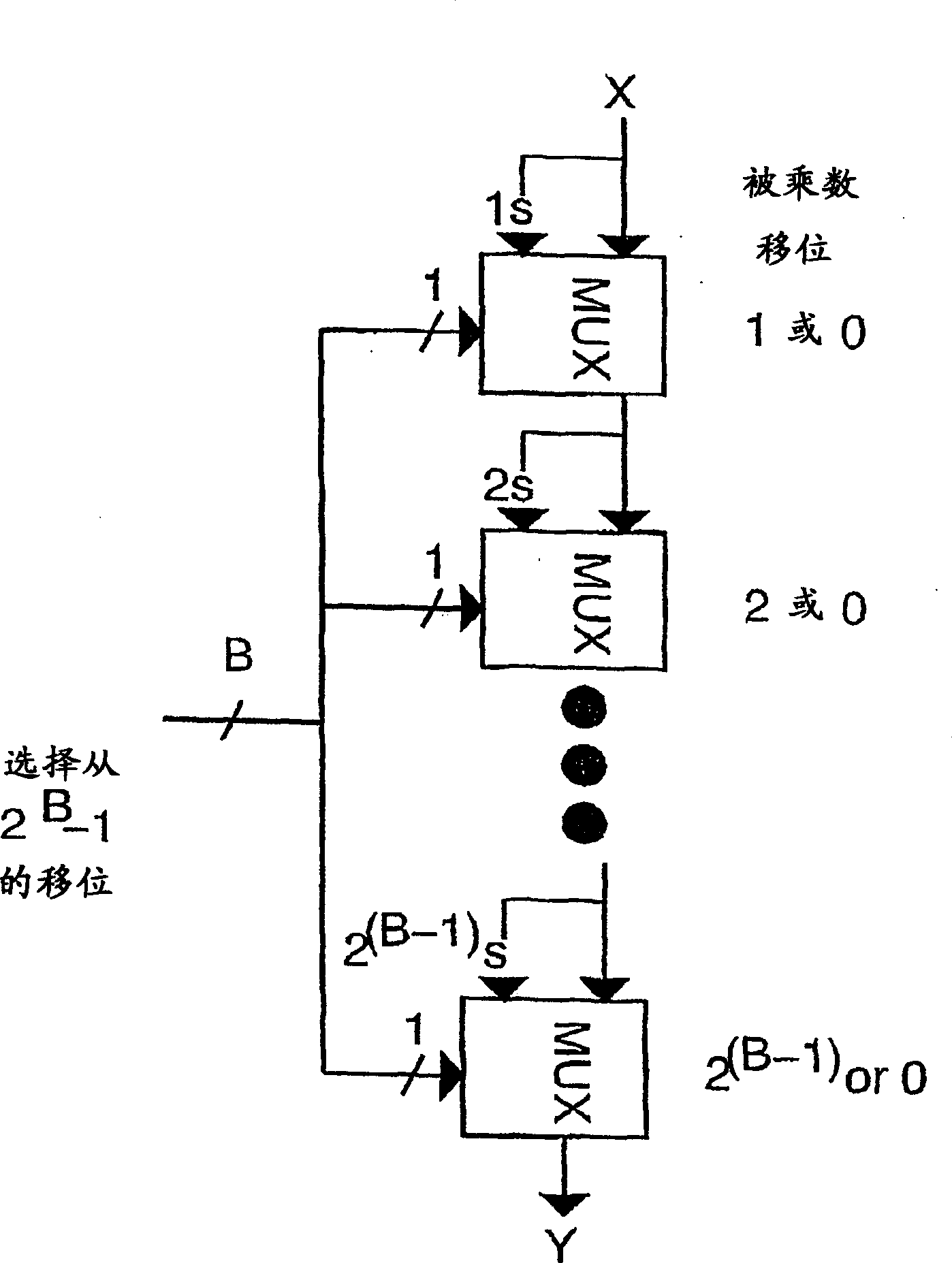

[0111] According to the present invention, image 3 Such a shift-minimizing arrangement in terms of hardware is shown in .

[0112] In general, shifts are produced consecutively, and each stage is adapted to achieve two different shift values, 0 or 2 (k-1) , k is the index (number) of the level, and k is 0~B. B represents the maximum number of stages required, and is linked to the number of bits of the input signal (for example, if applied to a multiplier, it is a multiplier), so that the input signal (multiplier) has 2 B bit. The shifts of each stage are binary weighted relative to each other. With such a structure, only B multiplexers (generally using log 2 (...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More