Method for mfg of semiconduceor device

A technology of semiconductors and oxide semiconductors, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as reducing contact resistance, reducing dose, and reducing mobility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

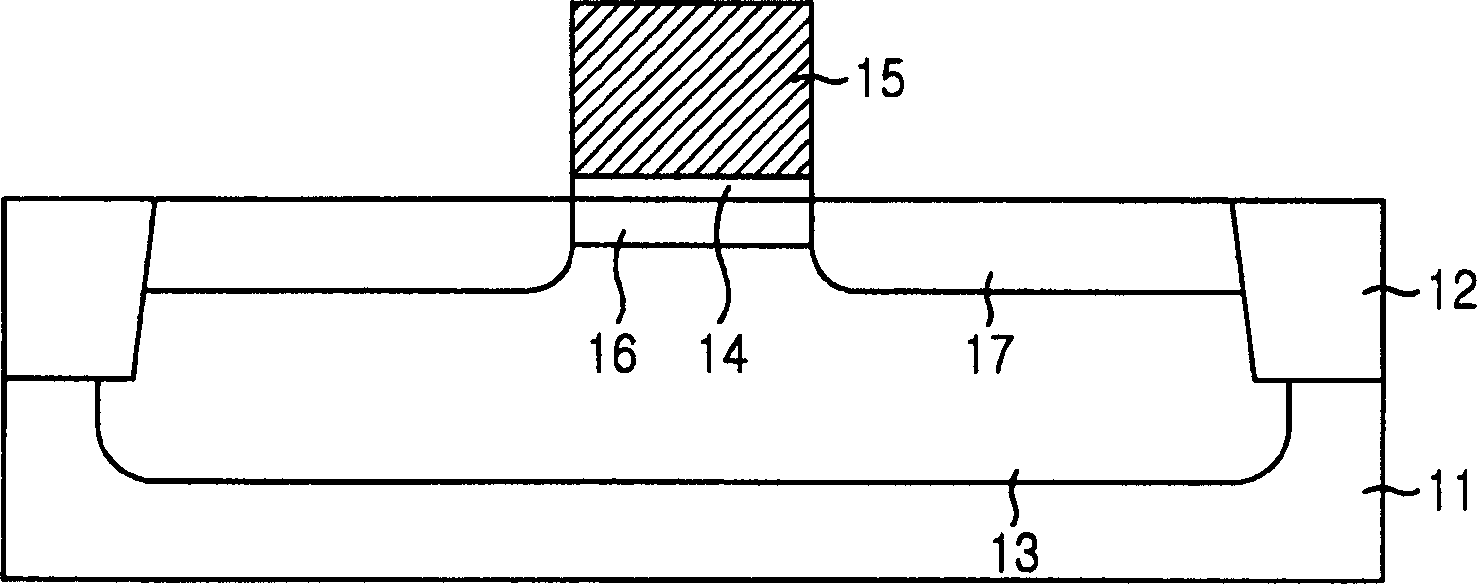

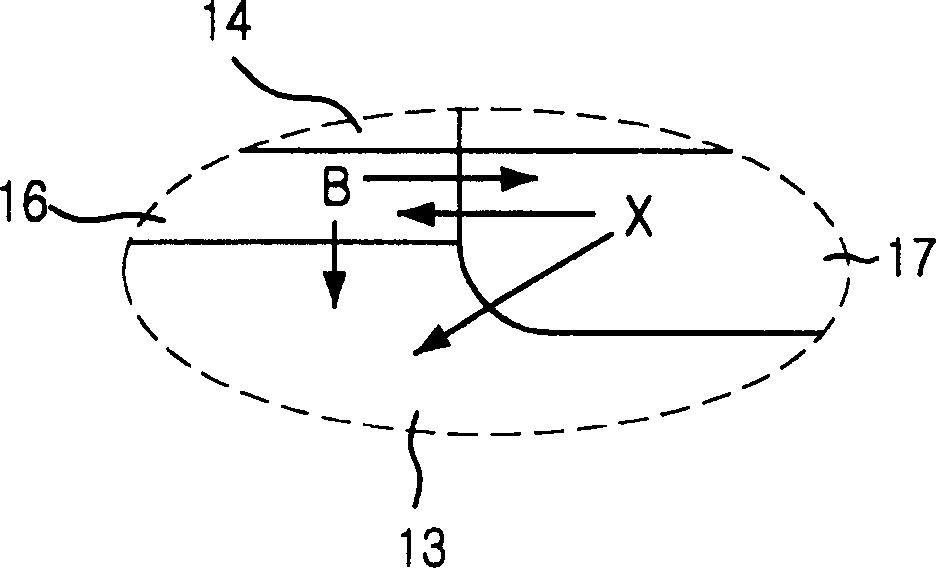

[0024] Hereinafter, preferred embodiments of the present invention will be described in detail with reference to the accompanying drawings.

[0025] In the preferred embodiments described below, the method for improving short channel characteristics is achieved by avoiding boron isolation from the semiconductor substrate as the channel and bulk region, but also by achieving uniformity of dopant in the channel region degree to implement. This is achieved by inhibiting components, such as intrusive defects, from entering the semiconductor substrate as channel and body regions, i.e. by increasing Electroactivation of boron in the dopant reduces the amount of deactivation.

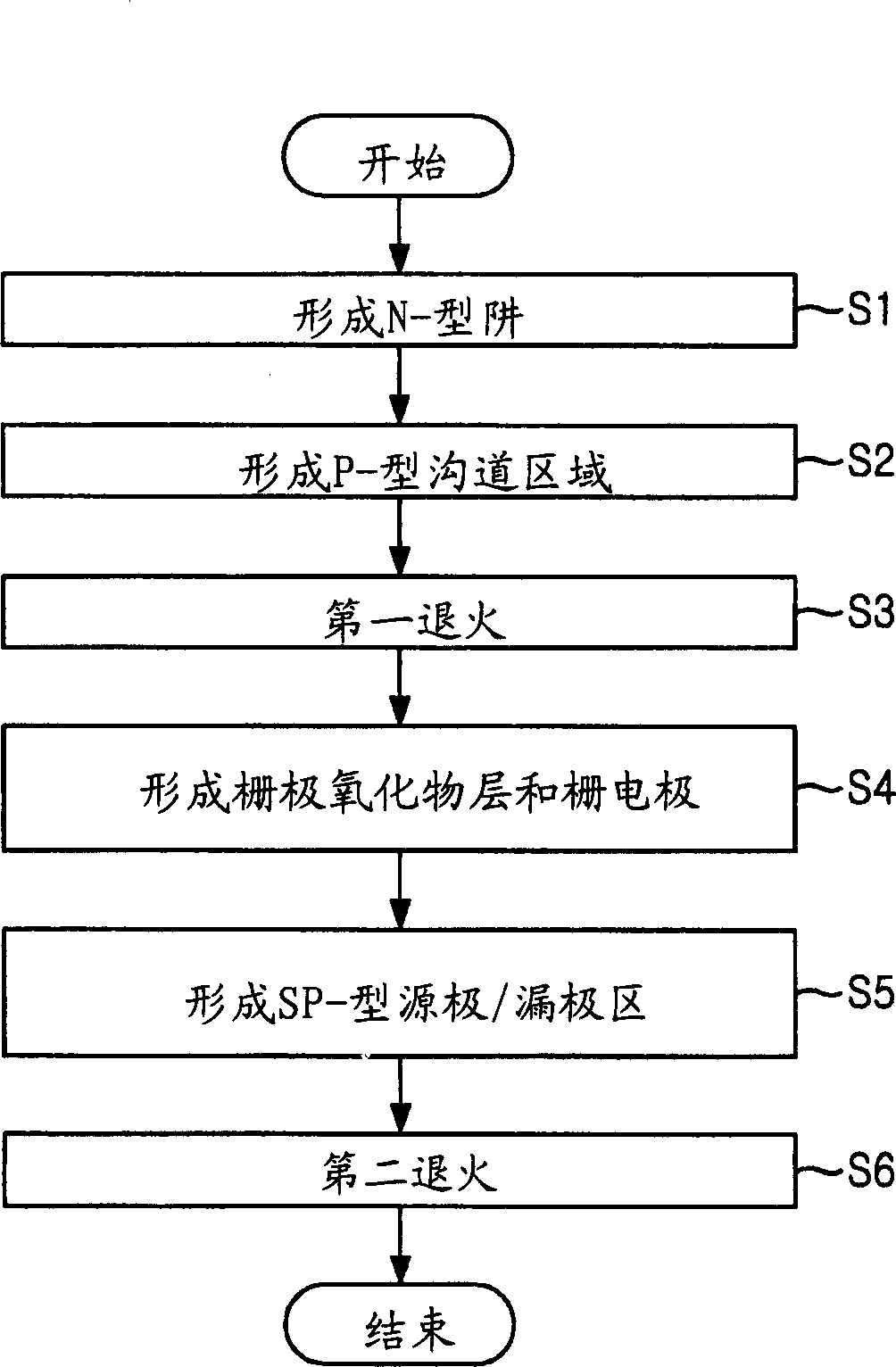

[0026] figure 2 A flow chart showing a PMOS device according to a preferred embodiment of the present invention.

[0027] Such as figure 2 As shown, the method for manufacturing a PMOS device includes a process (S1) for forming an n-type well; a process (S2) for forming a p-type channel region; a process...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More