Address mapping method and system for FFT processor with completely parallel data

An address mapping and processor technology, applied in the field of FFT processors, can solve the problem of low data parallelism

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

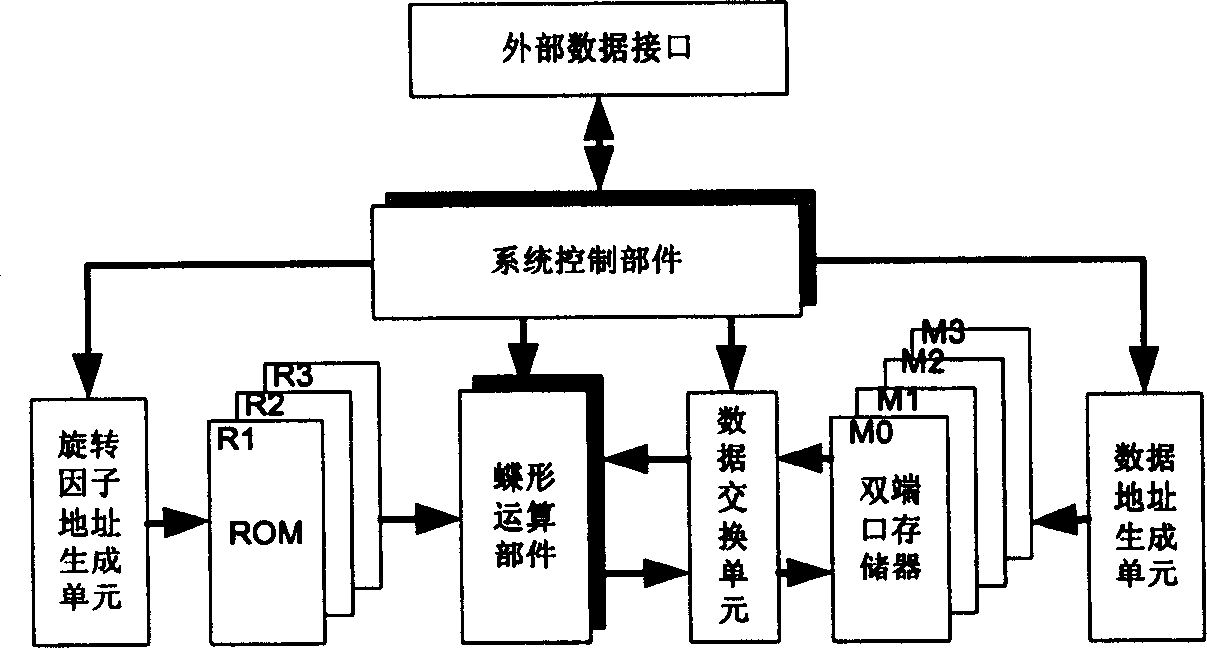

[0017] FFT processor block diagram of the present invention sees figure 1 , it is mainly composed of the following parts: the butterfly operation unit can complete one radix 4 or two radix 2 operations per cycle; the operation data is stored in the dual-port memory according to certain rules, and the dual-port memory is divided into 4 storage Body (M0, M1, M2, M3), which can complete the parallel reading and writing of 4 input data and 4 output data each time; according to the requirements of the address mapping algorithm, a data exchange component is needed between the operation unit and the memory; the rotation Factors are stored in ROM, they are divided into three memory banks, and provide three rotation factors required by a radix-4 butterfly operation; the system control part is responsible for the control and synchronization of the internal data of the processor; the external data interface is responsible for communicating with the external communication of data.

[001...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More