Method and device for correcting internal call or return stack in microprocessor

A microprocessor and stack technology, applied in machine execution devices, electrical digital data processing, instruments, etc., can solve problems such as microprocessors that cannot effectively use branch instruction misprediction, and achieve the effect of reducing the occurrence of air bubbles

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

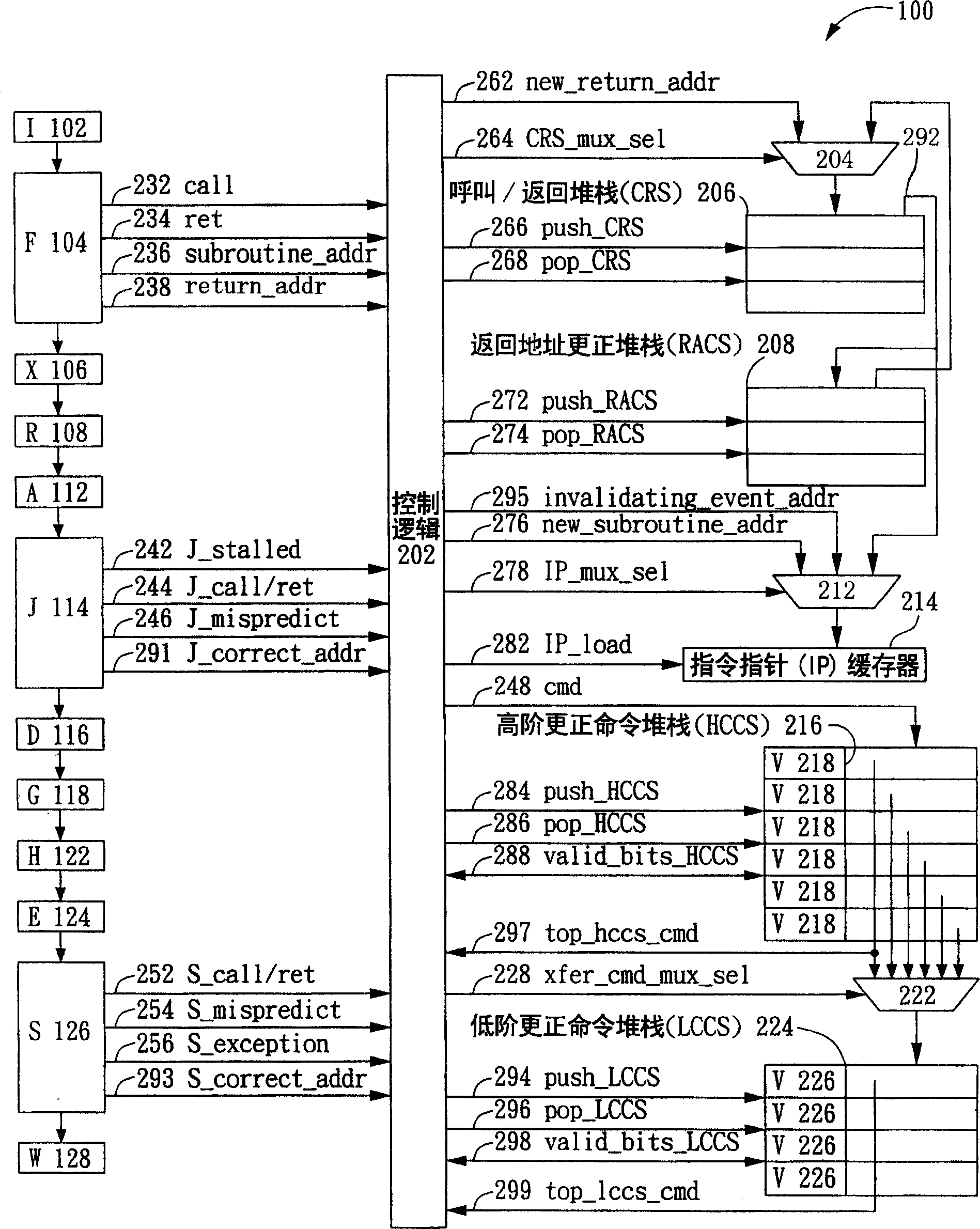

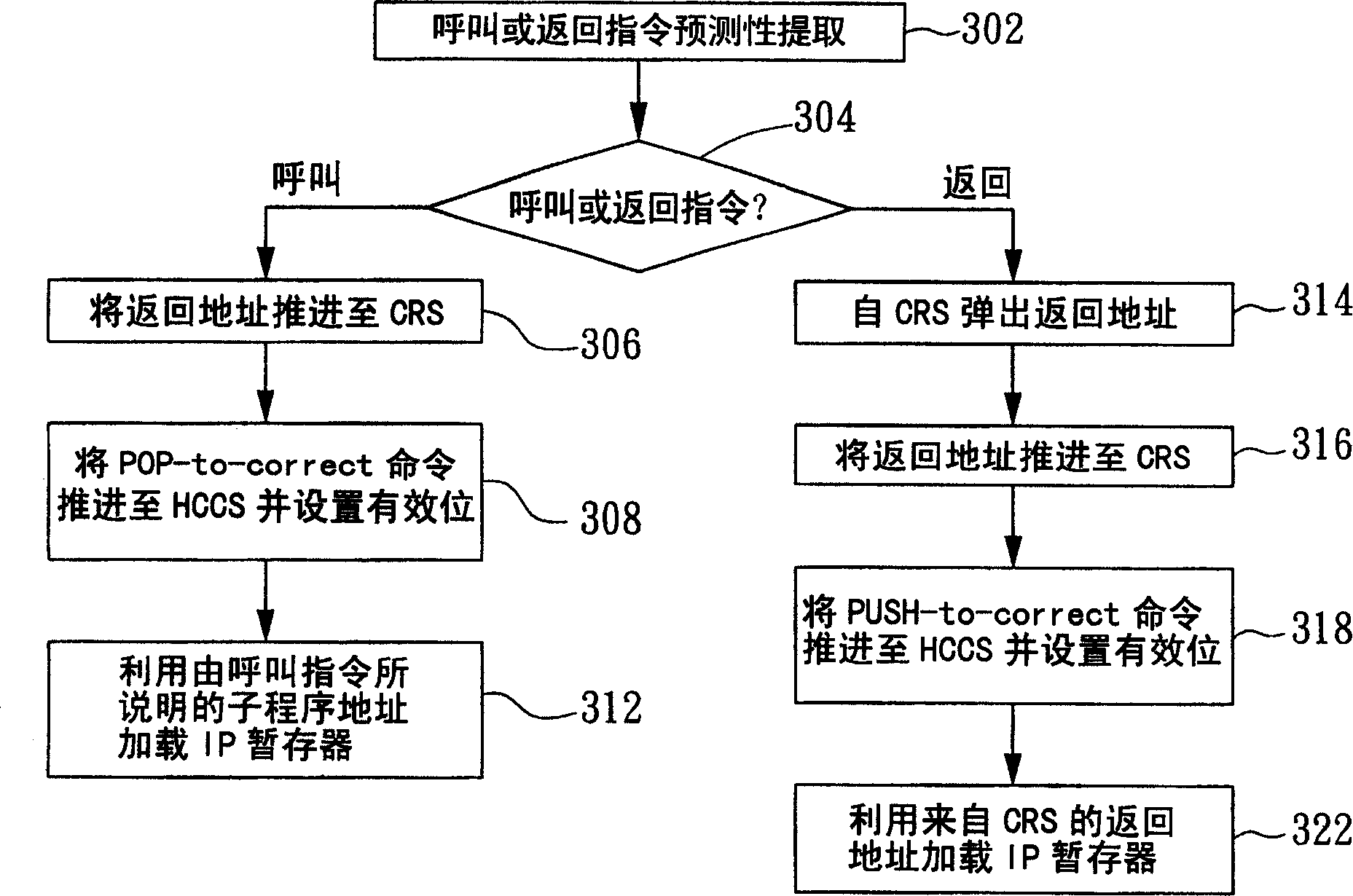

[0053] Please refer to figure 1 , which is a schematic block diagram of a pipelined microprocessor 100 of the present invention. In a preferred embodiment, the microprocessor 100 such as figure 1 Twelve strata are included as shown.

[0054] The microprocessor 100 includes an I level 102 (or called an instruction fetch level 102). The I-level 102 can provide a fetch address to an instruction cache to fetch instructions for execution by the microprocessor 100 . If the fetched address misses in the instruction cache, the I-level 102 fetches the missing cache line from a main memory coupled to the microprocessor 100 . In a preferred embodiment, the I-level 102 includes a branch target address cache. By fetching addresses from the instruction cache, such a branch target address cache may be stored along an instruction cache within the I-level 102. Pick. In addition, the branch target address cache can store target addresses of previously executed branch instructions, as well ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More