FIFO data buffering method and full up space accessing FIFO memory

A first-in-first-out and data cache technology, which is applied in the field of full-space first-in-first-out memory, can solve the problems that valid data cannot be read out, and full space cannot be written.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The present invention will be described in detail below with reference to the accompanying drawings. It is worth emphasizing that the following embodiments are only for making the description of the present invention clearer and easier to understand, rather than limiting the present invention.

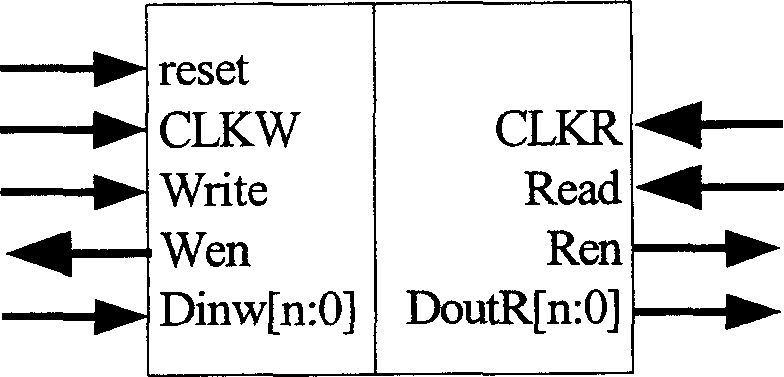

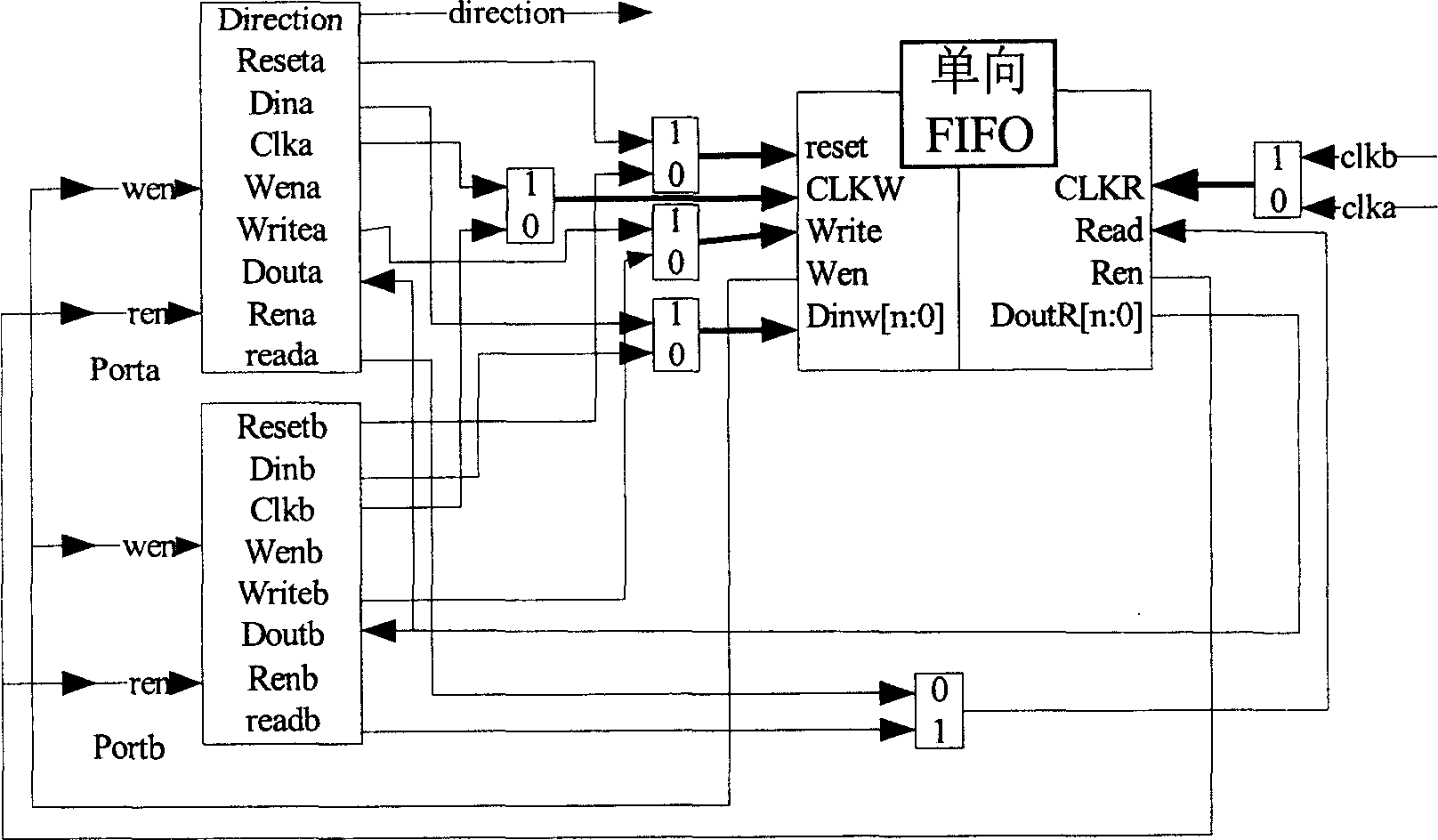

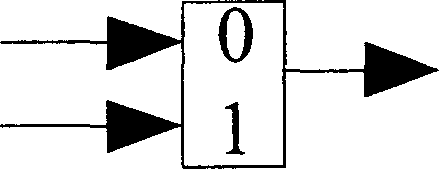

[0022] Figure 4 A schematic block diagram of a full-space first-in-first-out memory (FIFO) with a storage capacity of 2m·n bits according to the present invention is given. The present invention will be described below by taking the design of a 128*32 full space read-write FIFO as an example. Such as Figure 5 As shown, the 128*32 full space access first-in-first-out memory includes dual-port RAM, 8-bit counter A and counter B, and a read enable generation circuit and a write enable generation circuit. In this embodiment, the data bus width of the dual-port RAM 1 is 32 bits; the address bus width is 7 bits, that is, there are 128 addresses. Among them, the dual-port RAM can ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More