Topological structure optimization method of clock tree

A technology of topology structure and optimization method, applied in the field of electronics, to achieve the effect of strong versatility, reduced cost and good scalability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] Further illustrate the present invention below by specific embodiment:

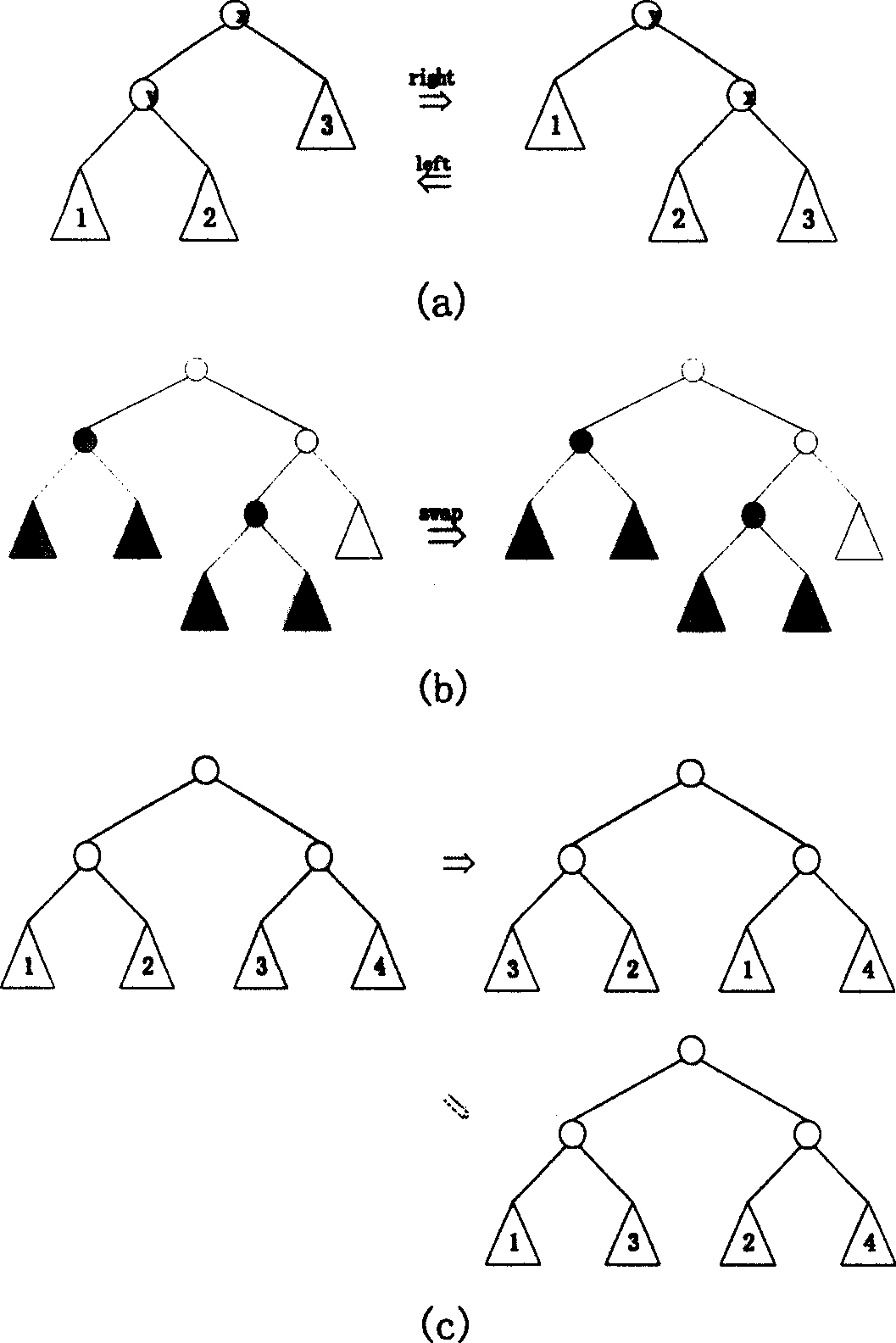

[0046] On a SoC chip whose physical and electrical parameters are known, the positions of the clock source and the clock receiving endpoint set have been determined. After topological division by a certain method, the initial topological relationship of the clock tree is obtained, such as figure 2 shown.

[0047] During a bottom-up local correction optimization process, it is assumed that the current operating point is node x. First perform a "trial" right-turn operation on node x, and calculate the topology information of the changed nodes along the way until reaching the root node to find the cost increment of the whole tree. During the calculation process, the topology structure remains undisturbed. Then perform a similar "trial" left-turn operation on node x, and calculate the corresponding cost increment. Choose the smaller one from the two cost increments, and then judge whether it is po...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More