Method for preventing fluorine diffusion in manufacturing process of fluorine-silicon glass

A technology using fluorosilicate glass and manufacturing technology, which is applied in the field of integrated circuit manufacturing technology and can solve problems such as corrosion and device failure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] Implementation steps of the present invention are as follows:

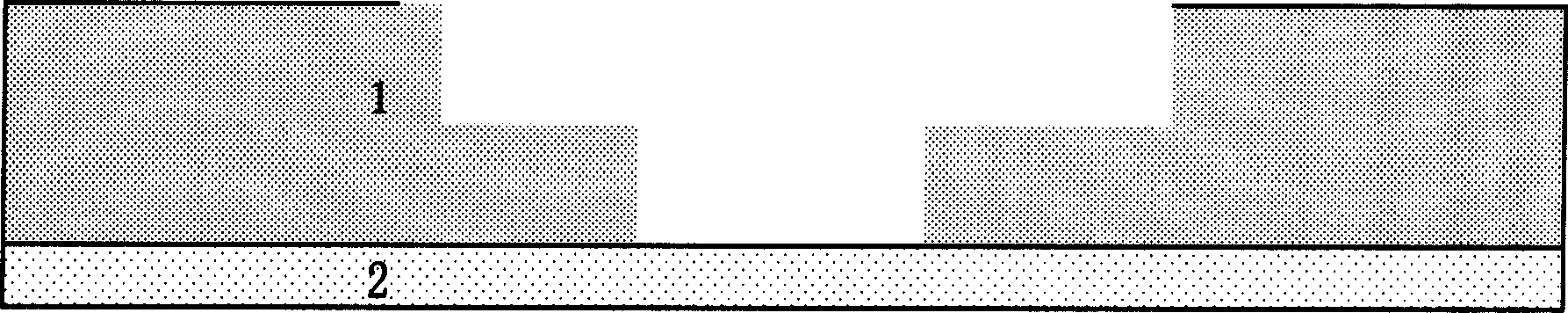

[0032] (1) According to the conventional process steps, the manufacture of the Damascus metal wire structure is completed. like figure 1 As shown, the fluorosilicate glass low dielectric material 1 is constructed on the bottom barrier layer 2 .

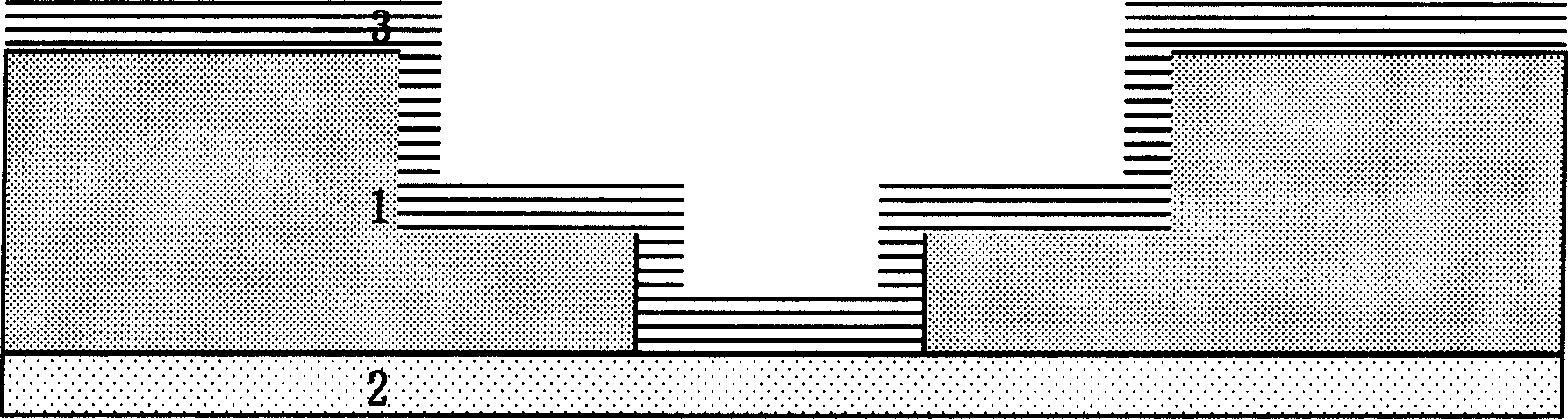

[0033] (2) if figure 2 As shown, the plasma surface treatment was carried out, the treatment time was 50 seconds, the air pressure was set to 5 Torr, 10 Torr, 30 Torr or 50 Torr, the power was selected to be 100 W, 150 W or 500 W, and the temperature was selected to be 150 W. degrees, 250 degrees or 400 degrees, the gas source is an inert gas helium, neon, argon, krypton or xenon, and the reaction gas source is carbon monoxide CO, carbon dioxide CO 2 , sulfur dioxide SO 2 , Nitrogen N 2 Then cleaning and annealing are carried out. After the plasma surface treatment, the fluorine concentration on the surface of the fluorosilicate glass low dielectric material...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More