Method for series and anti-series link data of equalizing complex strip parallel

A link data, plural technology, applied in the field of SERDES link data protection, can solve the problems of data loss, large delay, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

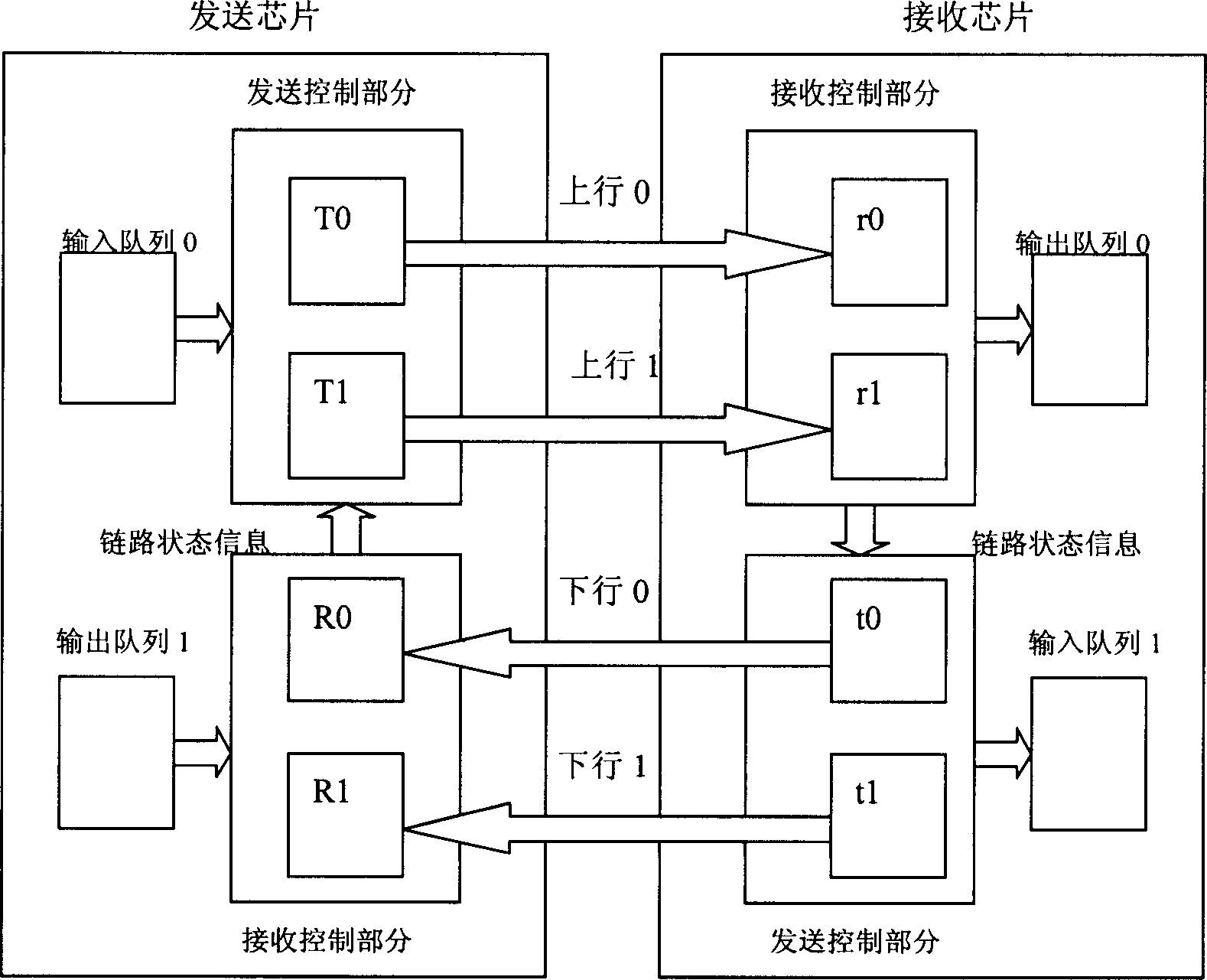

[0030] Such as figure 1 , the data link consists of two SERDES parallel links, uplink 0 and uplink 1, respectively. Both the sending chip and the receiving chip have a sending control part and a receiving control part, and there is a channel connection from the receiving control part in the chip to the sending control part to transmit link state information. T0, T1, t0, and t1 in the figure are four SERDES sending units, and R0, R1, r0, r1 are four SERDES receiving units. The data channels in the uplink direction and downlink direction (the two SERDES links from left to right are the uplink direction, and the two SERDES links from right to left are the downlink direction) together form a complete bidirectional digital channel.

[0031] The reception of the link state is accomplished by relying on the SERDES reception control part. Such as figure 1 As shown, r0 and r1 can respectively detect the states of the uplink 0 and uplink 1 links, while R0 and R1 can respectively dete...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More