Semiconductor memory cell array having mos transistors and method for forming the same

A storage unit and semiconductor technology, applied in semiconductor/solid-state device manufacturing, transistors, semiconductor devices, etc., can solve the problems of reducing coverage tolerance and inability to guarantee layer coverage accuracy, so as to reduce the standard distance, improve unit performance, and low The effect of contact resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029]The invention is illustrated by the process of forming a silicon-based DRAM. The individual structures of the dynamic memory cells are preferably formed by means of silicon planar technology, which comprises a series of individual processes carried out in each case in a full-area manner on the surface of the silicon substrate, where the Local changes. In DRAM memory fabrication, multiple memory cells are formed simultaneously.

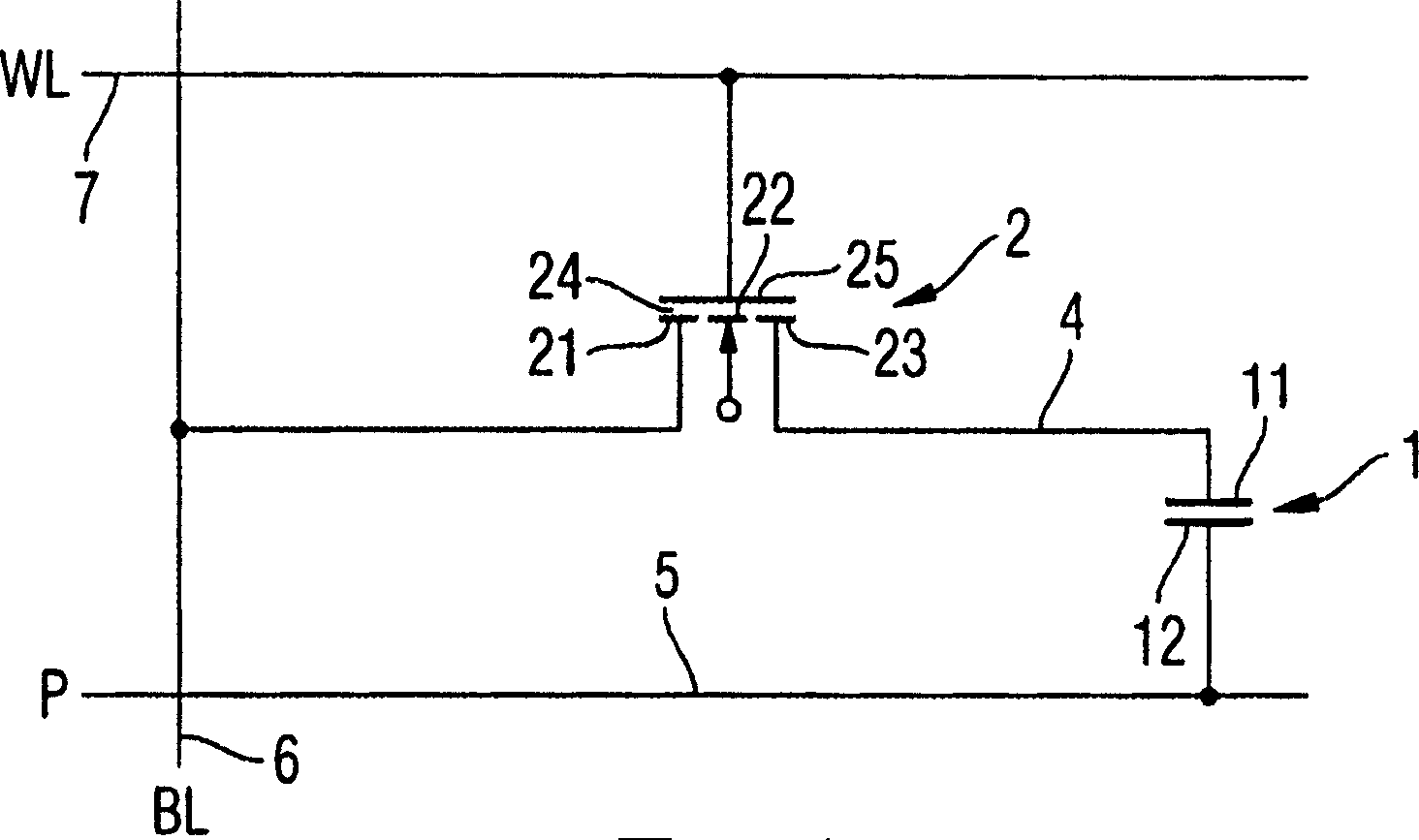

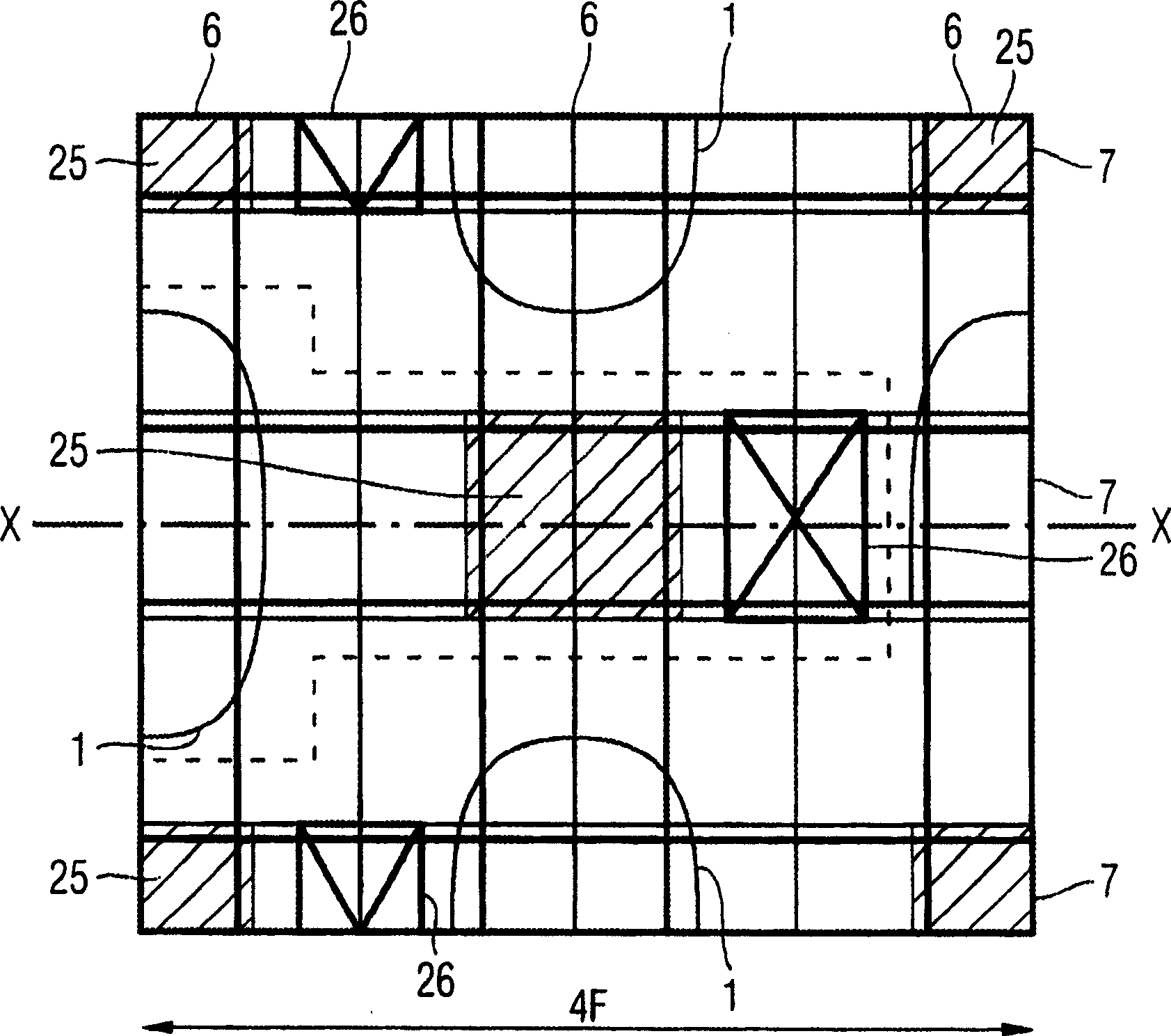

[0030] In DRAM, the application is mainly composed of a single-transistor memory cell, and its circuit diagram is as follows figure 1 shown. A one-transistor memory cell includes a storage capacitor 1 and a selection transistor 2 . The selection transistor 2 is preferably formed as a field effect transistor having a first source / drain electrode 21 , a second source / drain electrode 23 and an active region 22 therebetween. The gate insulating layer 24 and the gate 25 are positioned on the top of the active region 22, acting like a flat plate ca...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More