A stacking type wafer packaging structure

A chip packaging and stacking technology, applied in the direction of semiconductor/solid-state device components, semiconductor devices, electrical components, etc., can solve the problems of inability to be precise and the height cannot be reduced, and achieve the effect of reducing the height and volume.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

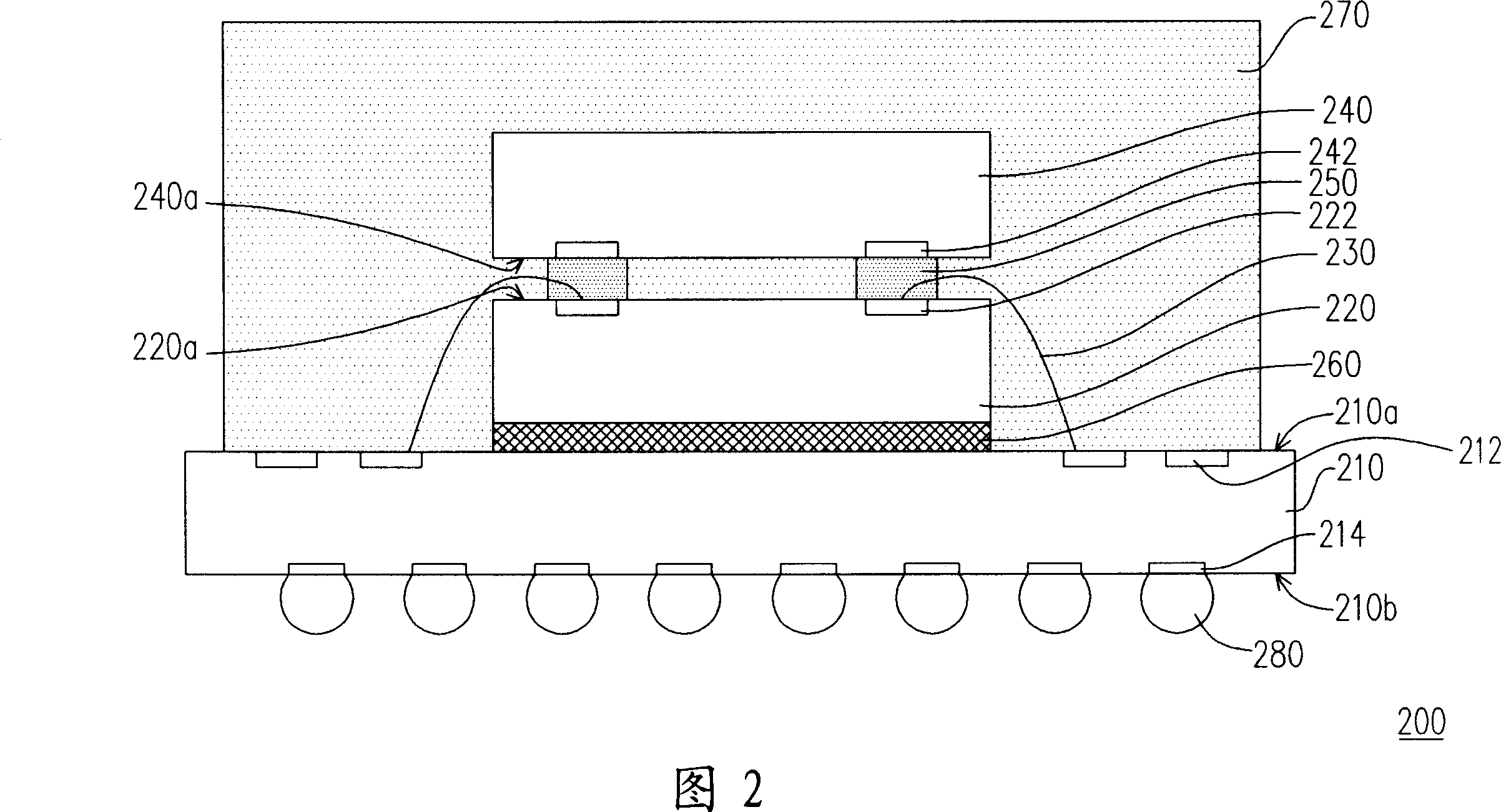

[0042] FIG. 2 is a schematic cross-sectional view of the first embodiment of the stacked chip package structure of the present invention. Referring to FIG. 2 , the stacked chip package structure 200 of the present invention mainly includes a substrate 210 , a first chip 220 , a plurality of bonding wires 230 , a second chip 240 and a plurality of B-stage conductive bumps 250 . A plurality of first solder pads 212 and a plurality of second solder pads 214 are respectively disposed on the first surface 210 a and the second surface 210 b of the substrate 210 . The first chip 220 is disposed on the first surface 210 a of the substrate 210 , and a plurality of third bonding pads 222 are disposed on the active surface 220 a. In an embodiment of the present invention, the first chip 220 is adhered on the substrate 210 through an adhesive layer 260 . However, the first chip can also be fixed on the substrate 210 by other methods, and the present invention does not impose any limitati...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More