Method for parallelly detecting synchronous communication chips

A communication chip and chip technology, which is applied in the direction of electronic circuit testing, measuring electricity, measuring devices, etc., to achieve the effect of shortening test time, shortening test time and reducing test cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

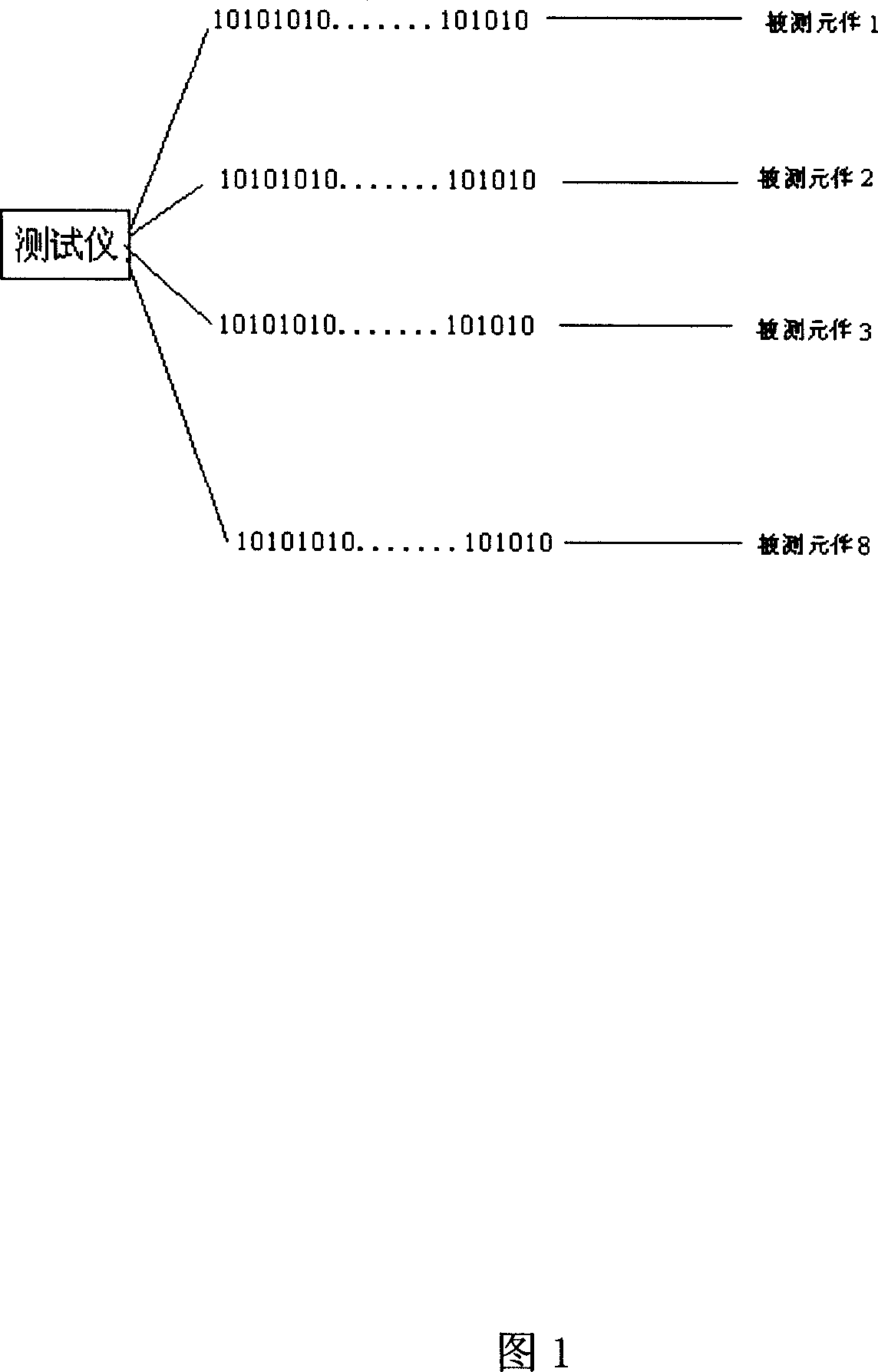

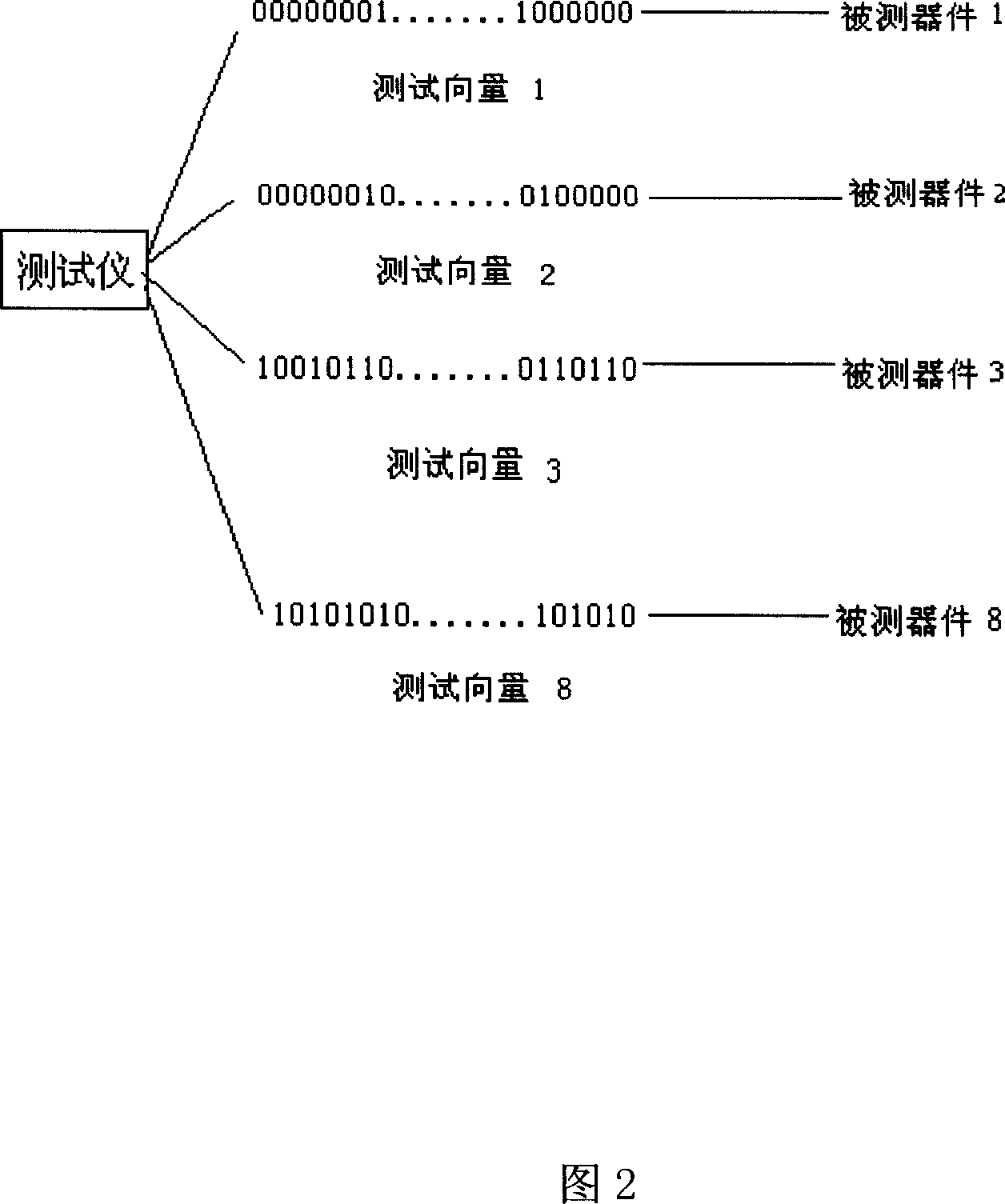

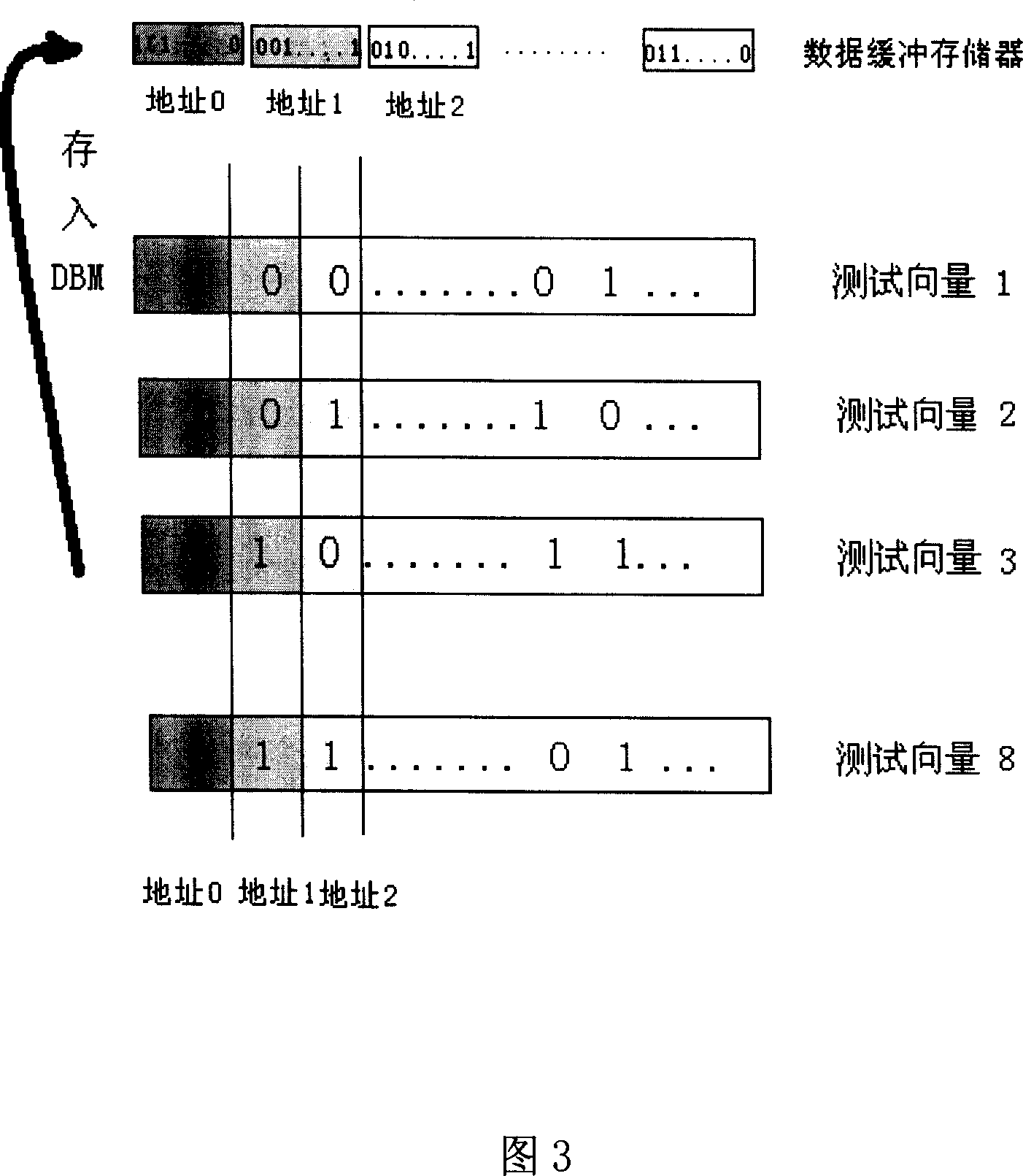

[0011] The method for parallel testing of synchronous communication chips of the present invention first divides the different test vectors of all tested components into the memory of the tester according to the clock cycle, and then outputs all the stored data in parallel according to the clock cycle, thereby obtaining multiple tested components. Parallel testing of multiple test vectors for components, and simultaneous pass / failure judgments. Realize the simultaneous testing of different test vectors on multiple chips of the synchronous communication chip (see Figure 2).

[0012] The process of dividing and storing is: the first DUT coordinates of each simultaneous measurement are obtained through the probe station communication of the tester, and then according to the relative position of each DUT during the simultaneous measurement, the coordinate of each DUT can be calculated for each simultaneous measurement. The specific coordinates of a DUT. Then according to the specific ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More