PLL circuit

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

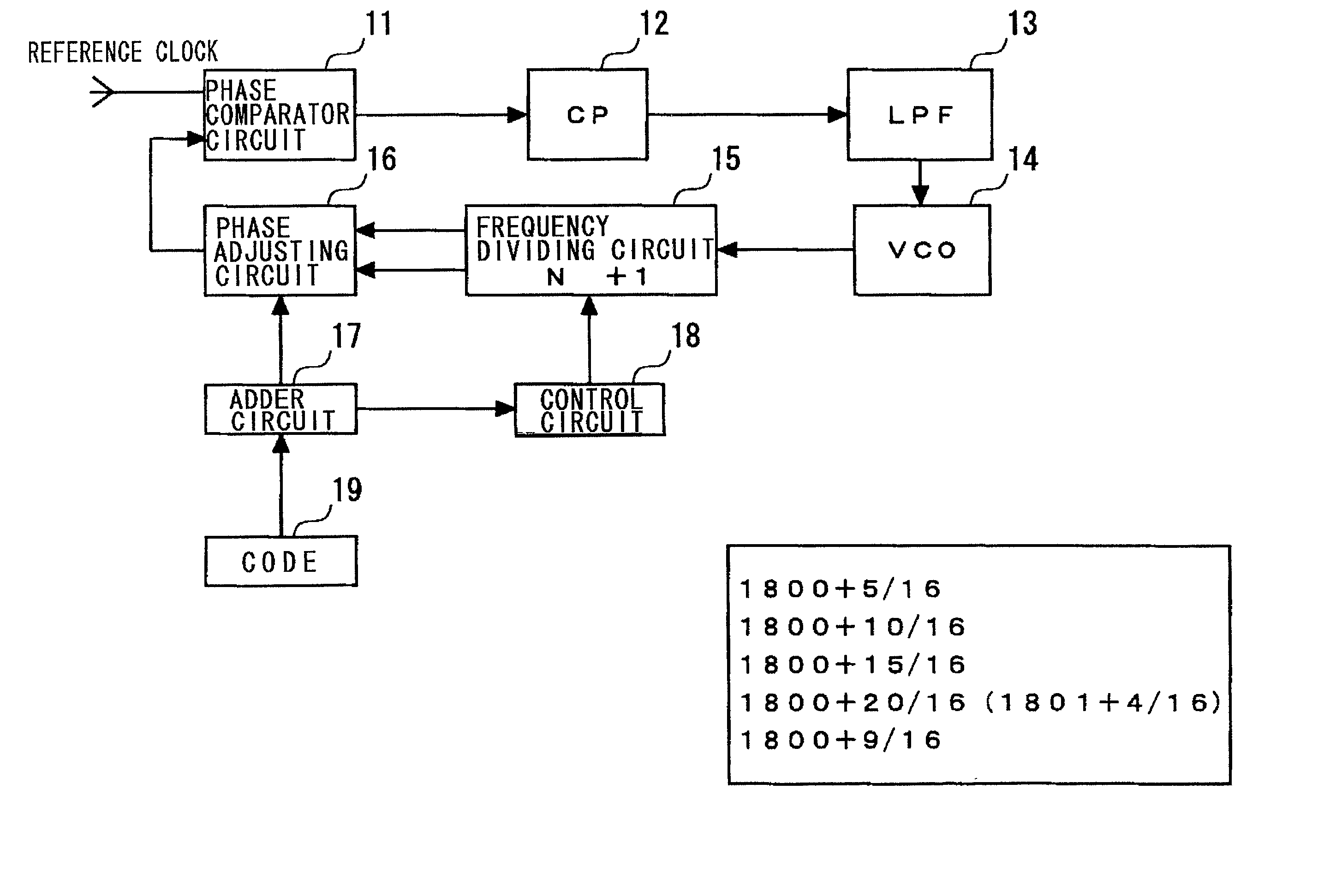

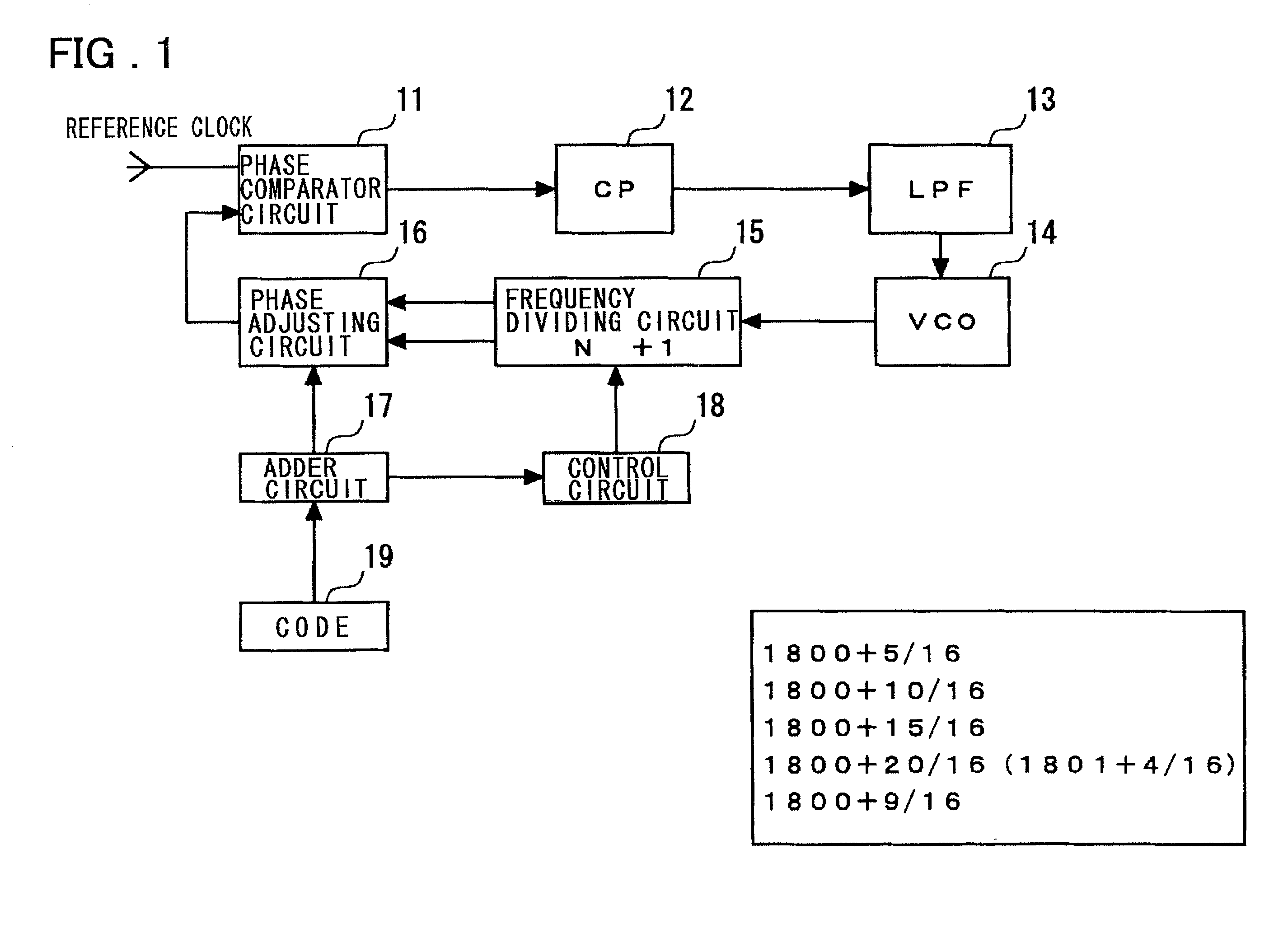

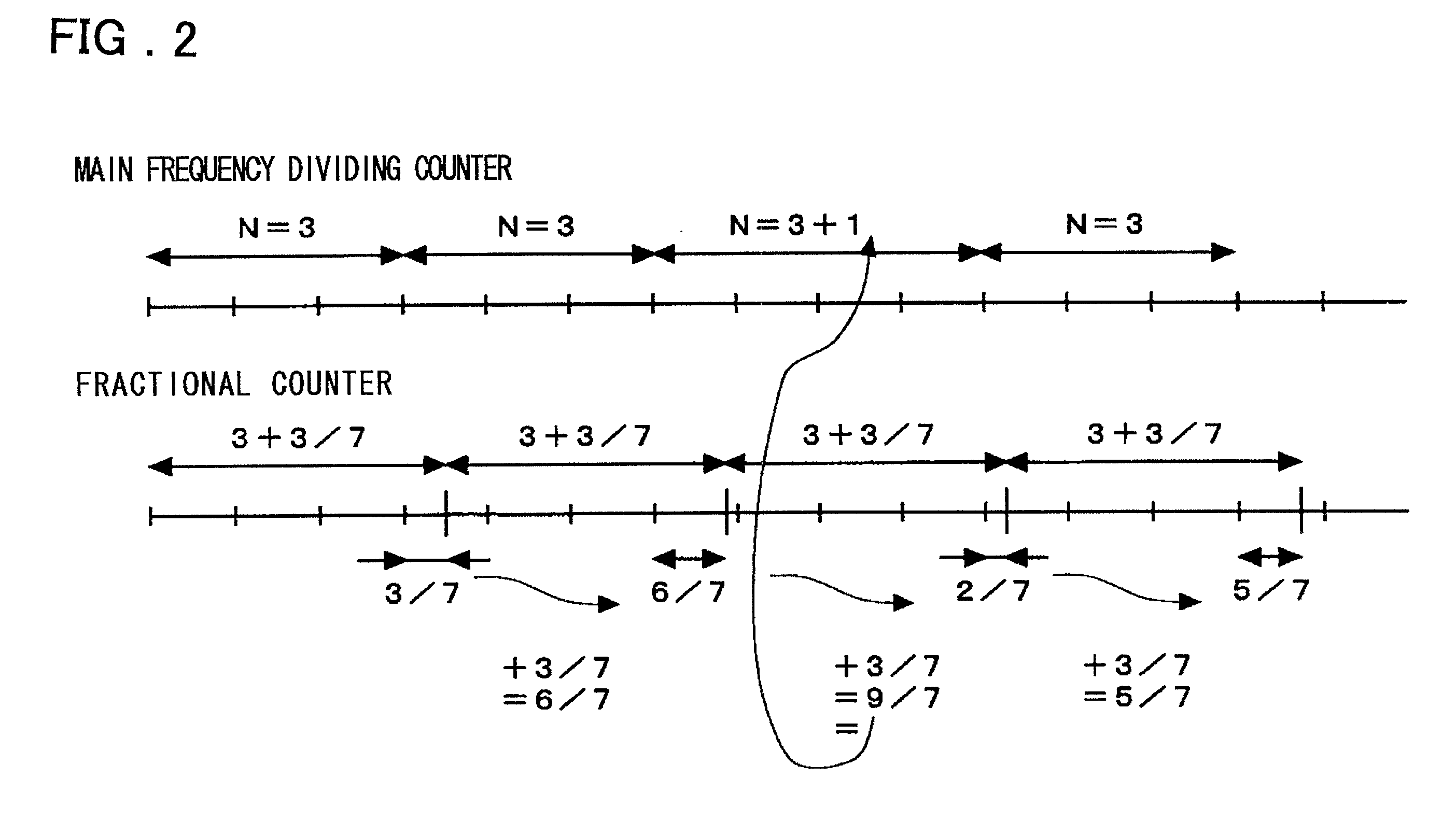

[0046] In the present invention, as shown in FIG. 1, a PLL circuit comprises: a frequency dividing circuit (15) for frequency dividing an integral part of an output signal from a voltage-controlled oscillator (14); a phase adjusting circuit (16), which receives two frequency-divided clocks of mutually different phases obtained by integral frequency division of the frequency dividing circuit(15) and generates an output signal which includes, as a delay time, a time that is the result of internally dividing a timing difference between the two frequency-divided clocks in accordance with a prescribed interior division ratio; a phase comparator circuit (11) for receiving a frequency-divided clock output from the phase adjusting circuit (16) and a reference signal to detect a phase difference between the signals received; a charge pump (12) for generating a voltage conforming to the phase difference output from the phase comparator circuit (11); and a loop filter (13) for supplying an out...

second embodiment

[0140] FIG. 9 illustrates a structure of the present invention, FIG. 10 is a diagram illustrating the connections to the interpolator portion of FIG. 9, and FIG. 11 is a diagram illustrating the timing waveforms on principal signals.

[0141] As shown in FIG. 9, the second embodiment of the invention has an interpolator 200 comprising 16-step first and second interpolators 216, 217 and a third interpolator 218 the inputs to which are the outputs of the first and second interpolators.

[0142] This embodiment includes a 16 / 17 prescaler 207 for frequency-dividing the output of a voltage-controlled oscillator 206. A signal obtained by converting a 16 / 17-divided output of the prescaler 207 to the CMOS level using an ECL / CMOS converter circuit 208 is input to an A counter 209 and to the clock input terminals of D-type flip-flops 214, 215. It should be noted that since the 16 / 17 prescaler 207, A counter 209, a B counter 210, an adder 211 and a register 212 operate in the same manner as the 32 / 3...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More