Reconfigurable measurement system utilizing a programmable hardware element and fixed hardware resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

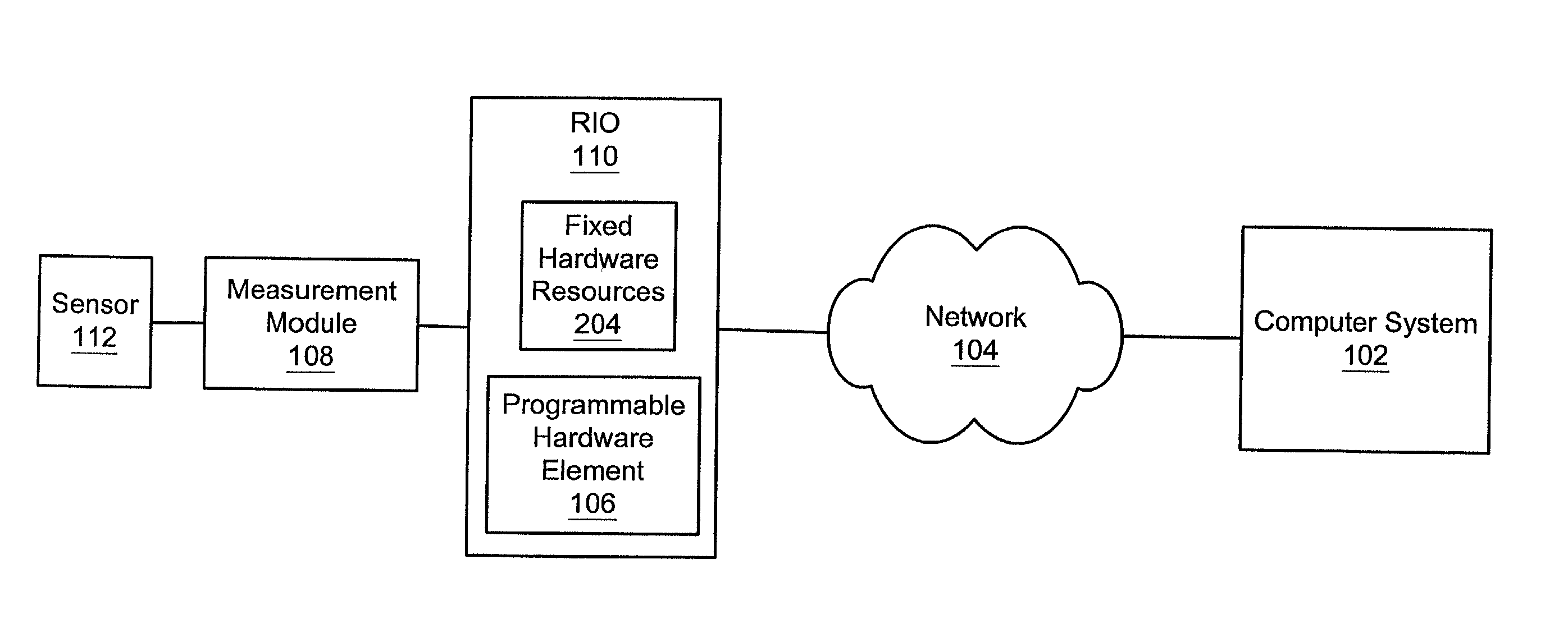

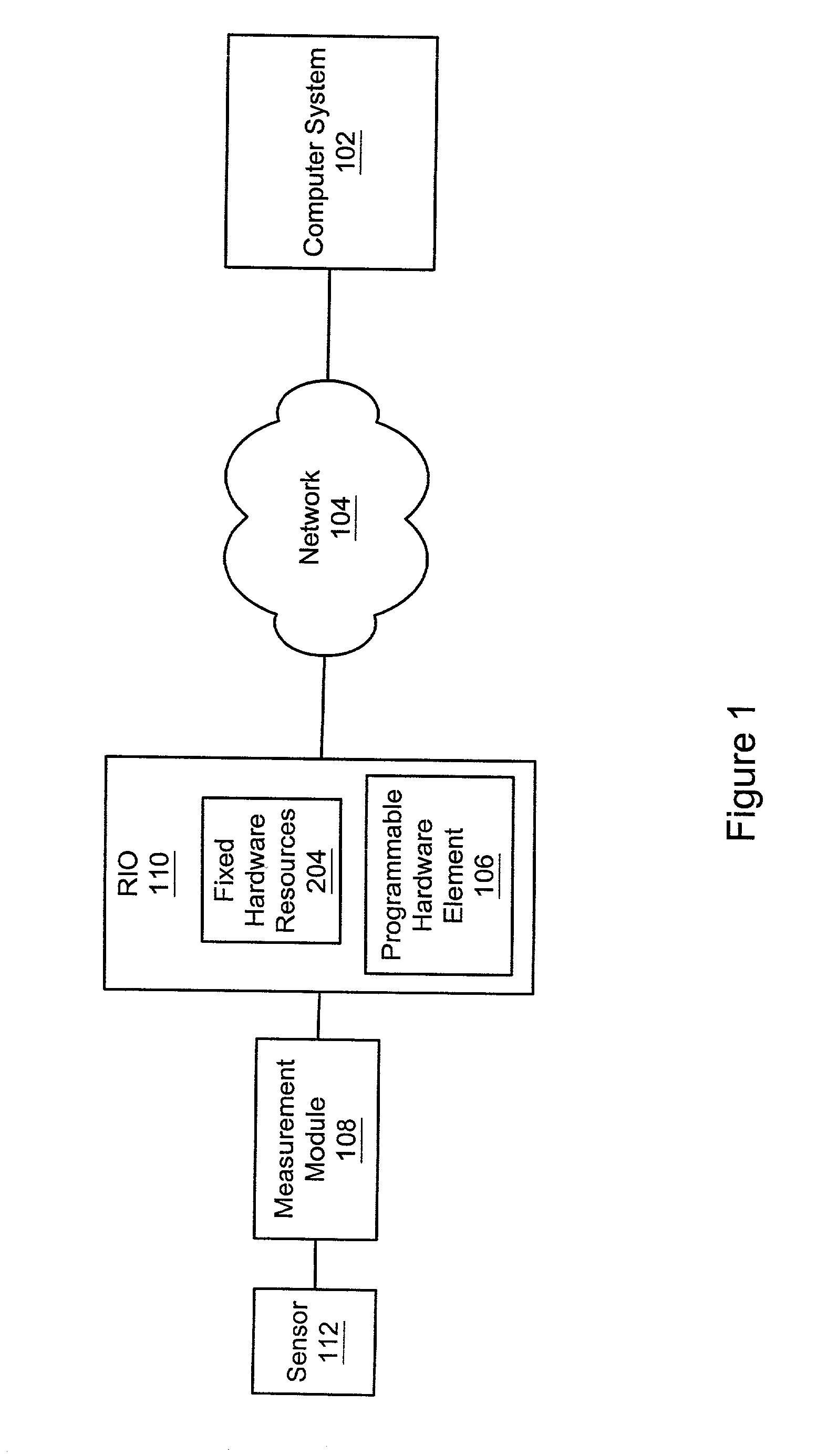

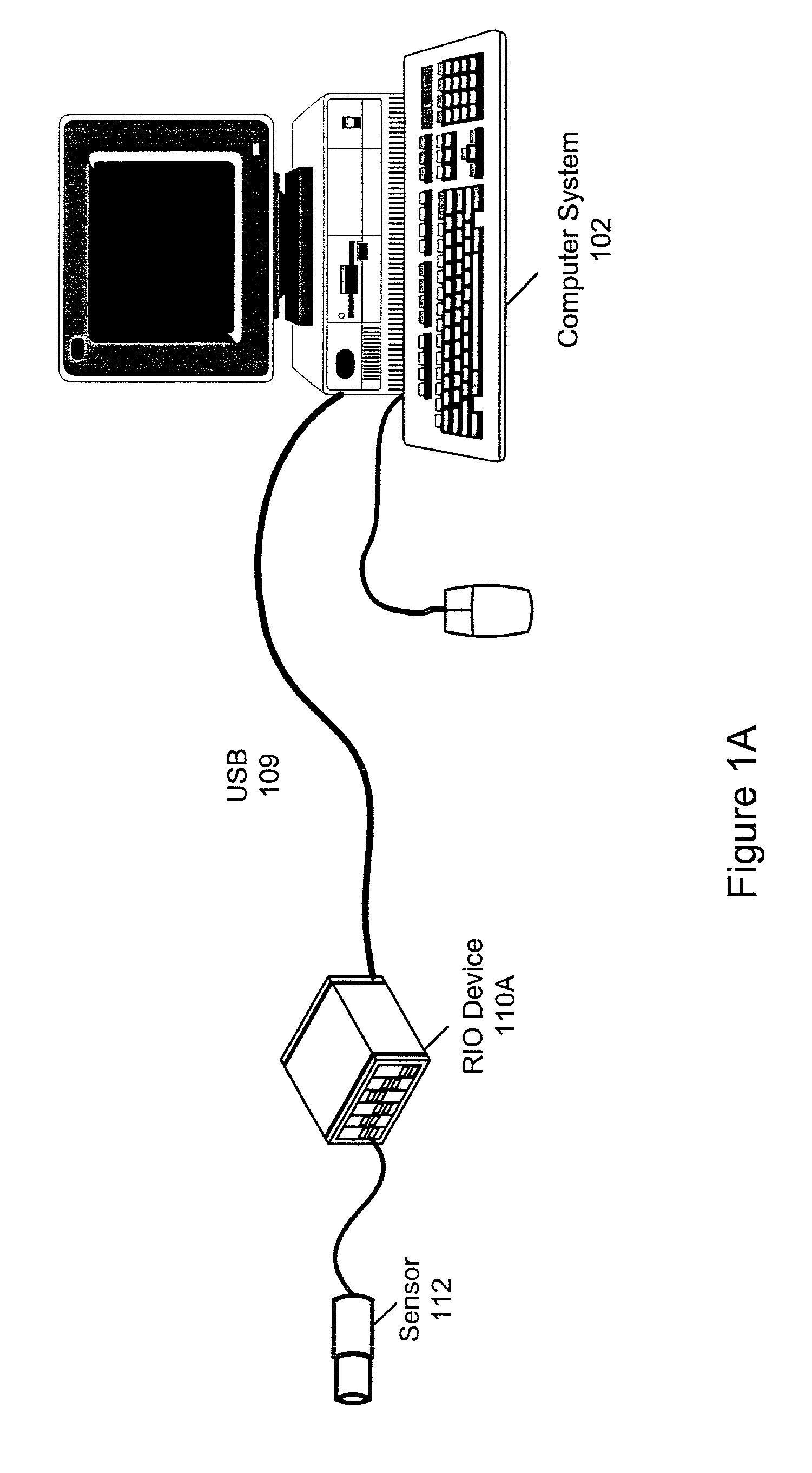

Image

Examples

example

[0386] A customer wishes to implement a control loop with National Instruments LabVIEW RT for an algorithm and LabVIEW FPGA for the timing and triggering. A control wizard may query the user about the I / O structure: How many synchronous analog inputs, analog outputs, digital inputs, digital outputs, and counters are in the system? How many asynchronous channels are in the system?

[0387] After receiving user input answering these queries, the control wizard may script a diagram with just the I / O the customer needs, as well as the required controls and indicators. The customer may then focus on the LabVIEW RT control algorithm instead of low level I / O details. If the customer discovers later that further customization of the timing and triggering is needed, the LabVIEW FPGA diagram may be modified directly.

[0388] In one embodiment, wizards may only include support for rudimentary functionality. In other words, wizards for basic acquisition, control loops, hardware in the loop testing, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More