Single-event upset immune frequency divider circuit

a frequency divider circuit and single-event technology, applied in pulse manipulation, pulse technique, instruments, etc., can solve the problems of phase shift in output signals, runt pulses on clock paths,

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

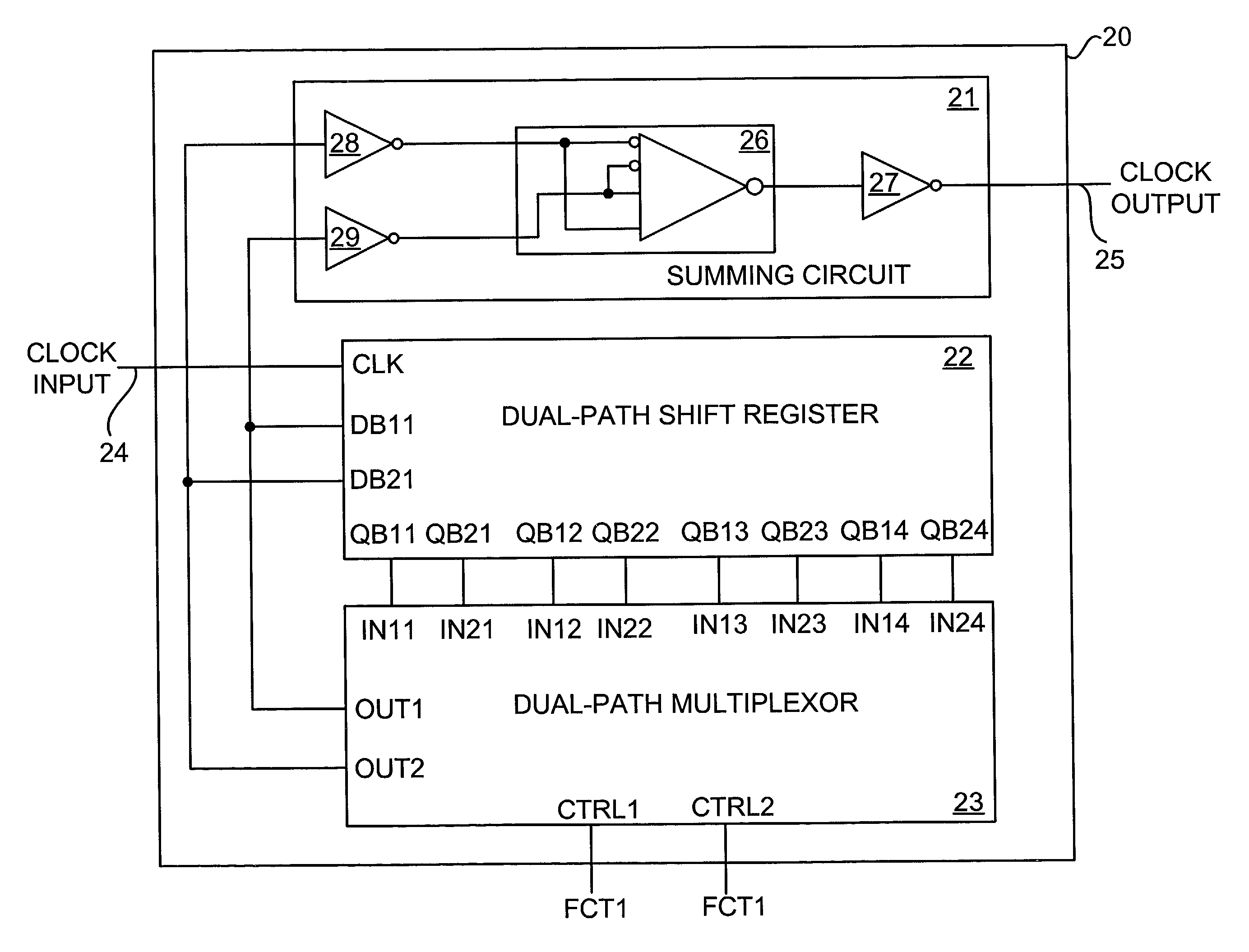

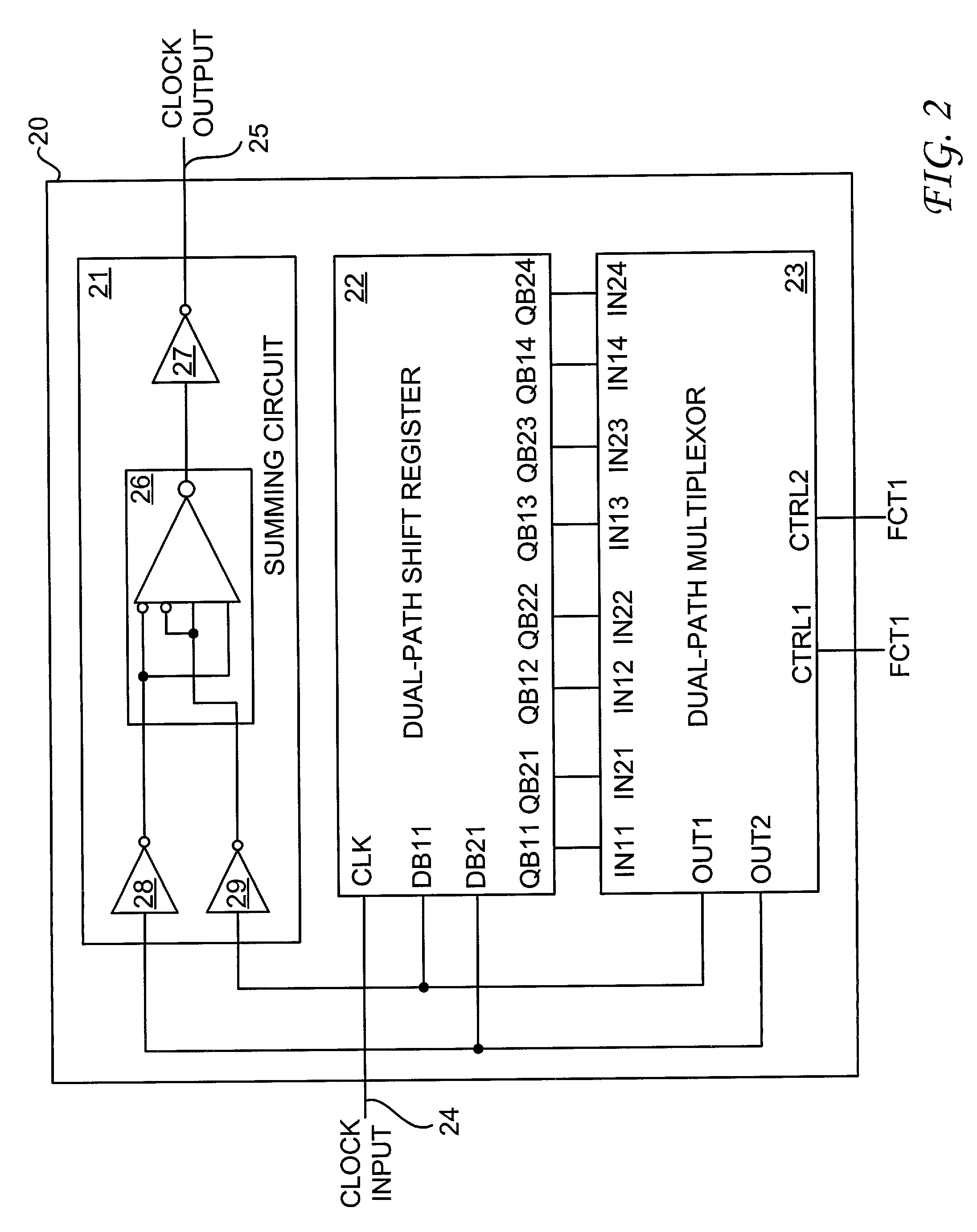

[0018] With reference now to FIG. 2, there is depicted a block diagram of a single-event upset (SEU) immune frequency divider circuit, in accordance with the preferred embodiment of the present invention. As shown, an SEU immune frequency divider circuit 20 includes a summing circuit 21, a dual-path shift register 22 and a dual-path multiplexor 23. SEU immune frequency divider circuit 20 also includes a clock input 24 and a clock output 25. Dual-path shift register 22 includes four output pairs, namely, QB11-QB21, QB12-QB22, QB13-QB23 and QB14-QB24. Dual-path multiplexor 23 may select any one of the four output pairs of dual-path shift register 22 to be fed back to an input pair DB11-DB12 of dual-path shift register 22. Depending on the selected output pair to be fed back, SEU immune frequency divider circuit 20 may divide an input clock signal from, for example, a system clock at clock input 24 by 2, 4, or 8 times in order to produce an output clock signal that is one-half, one-fou...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More