System resource router

a router and system resource technology, applied in the field of electronic circuits, can solve the problems of increasing limitations, impracticality of the bus switch architecture, and all data passing over the same wires, and achieve the effect of reducing unnecessary connections and increasing the bandwidth of the system

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The present invention is a system resource router for SOC applications. This disclosure describes numerous specific details that include specific hardware and data structures, circuits, architectures, and logic devices and functions in order to provide a thorough understanding of the present invention. One skilled in the art will appreciate that one may practice the present invention without these specific details.

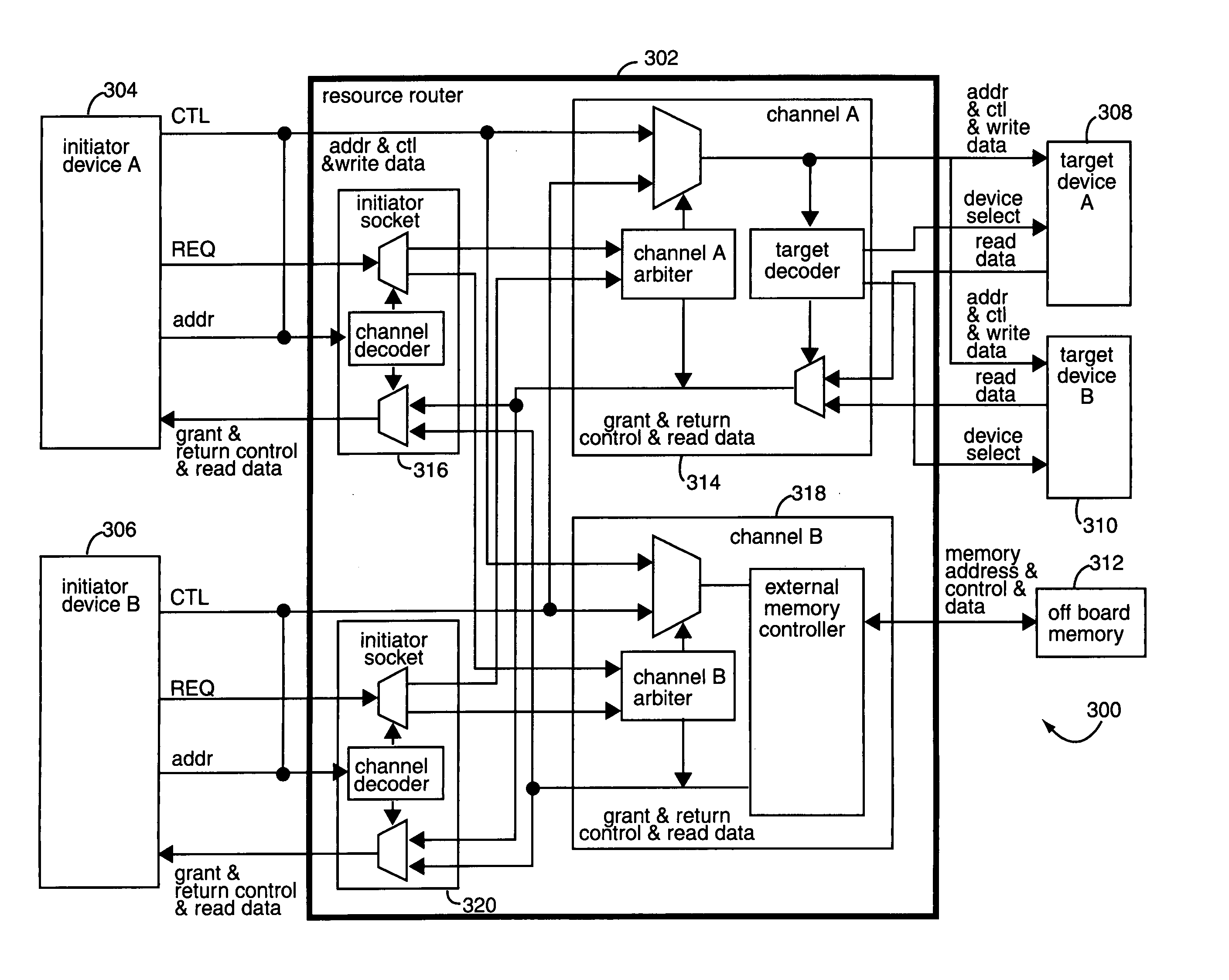

[0027]FIG. 1 shows a computer system embodiment of the present invention, and is referred to herein by the general reference numeral 100. The system 100 comprises a Harvard-architecture processor subsystem 102 connected through a system resource router 104 to a variety of resources on several buses. The system resource router 104 interfaces to a mix of bus initiators 106,108, 110, and 112 through channel sockets. It further interfaces to M-channel buses, e.g., a set of three M-channel buses 114, 116, and 118.

[0028] The M-channel bus 114 is shown with a typical com...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More