FPGA integrated circuit having embedded sram memory blocks with registered address and data input sections

a technology of integrated circuits and memory blocks, applied in the field of integrated circuits, can solve the problems of limiting the ability of a given fpga architecture to implement certain speed-critical designs, unable to complete its mission successfully on a first try, and modern fpga's tend to be fairly complex, so as to maximize the data output (data reading) bandwidth of embedded memory, increase the overall system bandwidth, and maximize bandwidth

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

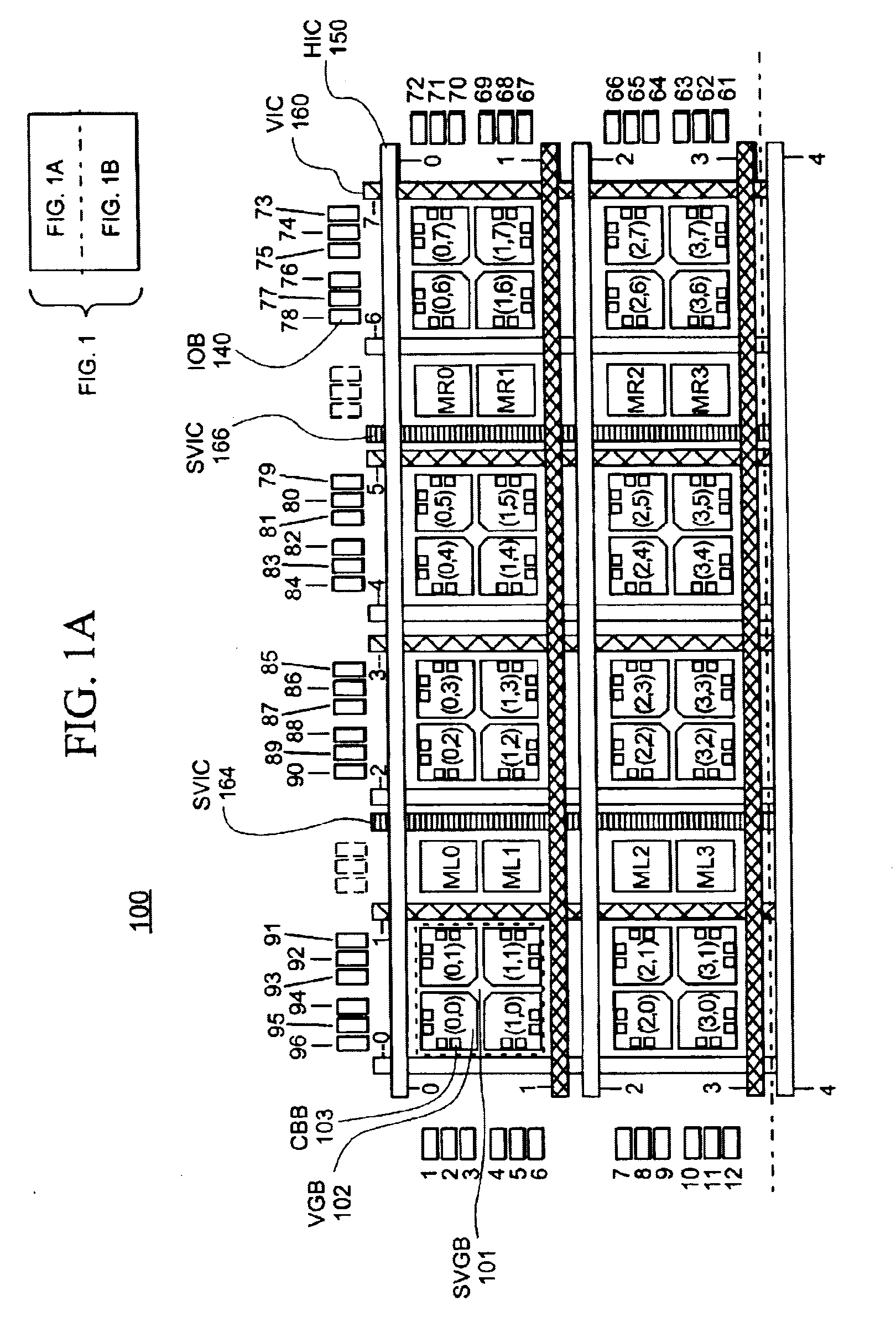

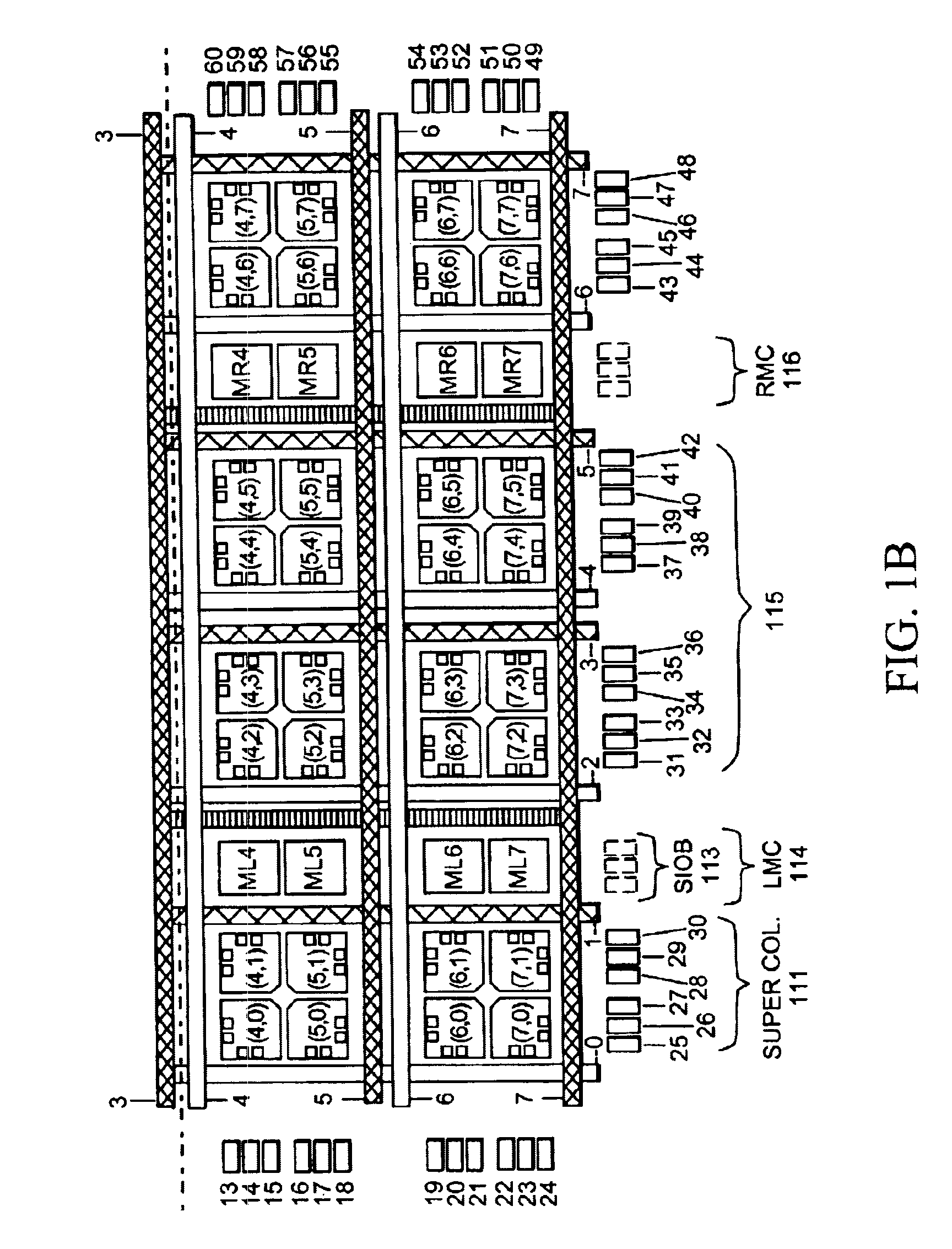

[0075]FIG. 1 shows a macroscopic view of an FPGA device 100 in accordance with the invention. The illustrated structure is preferably formed as a monolithic integrated circuit.

[0076]The macroscopic view of FIG. 1 is to be understood as being taken at a magnification level that is lower than later-provided, microscopic views. The more microscopic views may reveal greater levels of detail which may not be seen in more macroscopic views. And in counter to that, the more macroscopic views may reveal gross architectural features which may not be seen in more microscopic views. It is to be understood that for each more macroscopic view, there can be many alternate microscopic views and that the illustration herein of a sample microscopic view does not limit the possible embodiments of the macroscopically viewed entity. Similarly, the illustration herein of a sample macroscopic view does not limit the possible embodiments into which a microscopically viewed embodiment might be included.

[00...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More