Fabrication method of semiconductor integrated circuit device

a technology of integrated circuit devices and fabrication methods, which is applied in the direction of individual semiconductor device testing, semiconductor/solid-state device testing/measurement, instruments, etc., can solve the problems of not being able to detect, breaking the natural oxide film over and damaging the surface of the test pad itself. , to achieve the effect of reducing the inter-layer insulating film, and reducing the damage to the test pad

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

embodiment 1

(Embodiment 1)

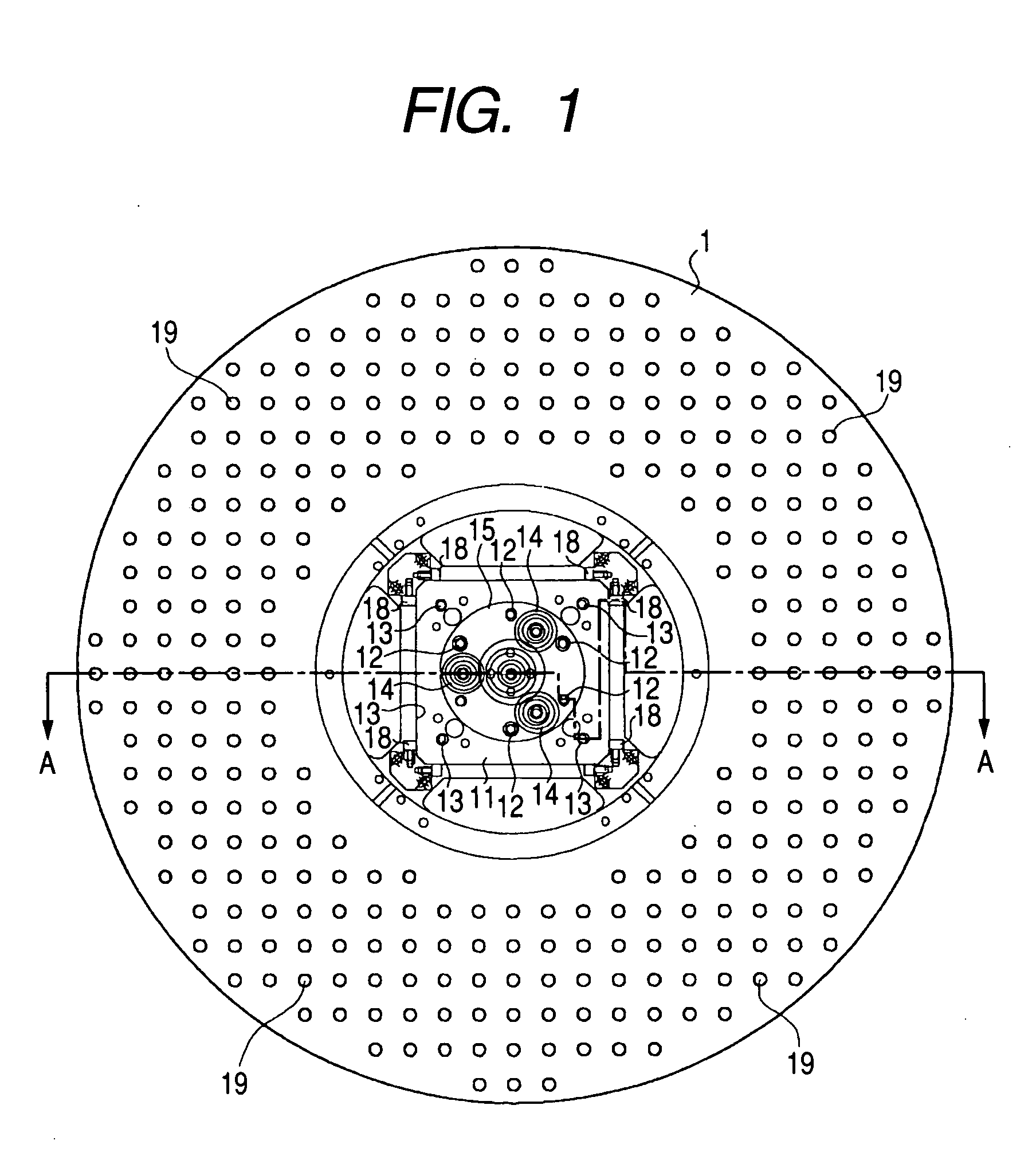

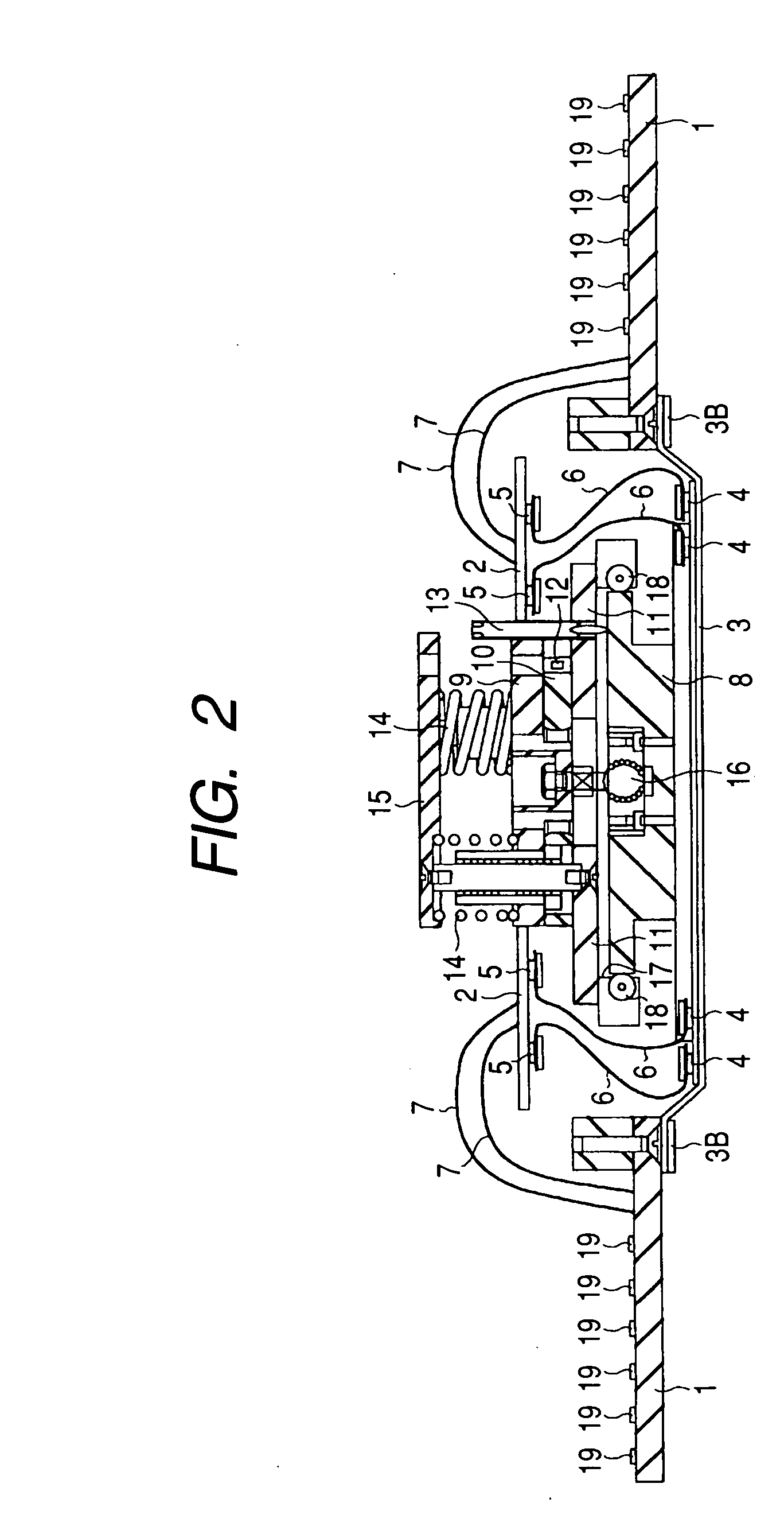

[0092]FIG. 1 is a plan view of a probe card (a first card), which represents Embodiment 1 of the invention, and FIG. 2 shows a section taken along line A-A in FIG. 1.

[0093] As shown in FIG. 1 and FIG. 2, in the probe card according to Embodiment 1, there are formed, for instance, a multi-layered wiring board (third substrate) 1, an auxiliary substrate 2, suppressing means, a thin film probe (first sheet) 3 and so forth. Further, in the probe card of this Embodiment 1, circuits (wirings) are formed in each of the multi-layered wiring board 1, the auxiliary substrate 2 and the thin film probe 3. By forming circuits in each of the multi-layered wiring board 1, the auxiliary substrate 2 and the thin film probe 3, the need to repair the whole probe card in the event of trouble in any one of the multi-layered wiring board 1, the auxiliary substrate 2 and the thin film probe 3 is dispensed with, but only the member in trouble (the multi-layered wiring board 1, the auxiliary ...

embodiment 2

(Embodiment 2)

[0175] Next, an Embodiment 2 of the invention will be described.

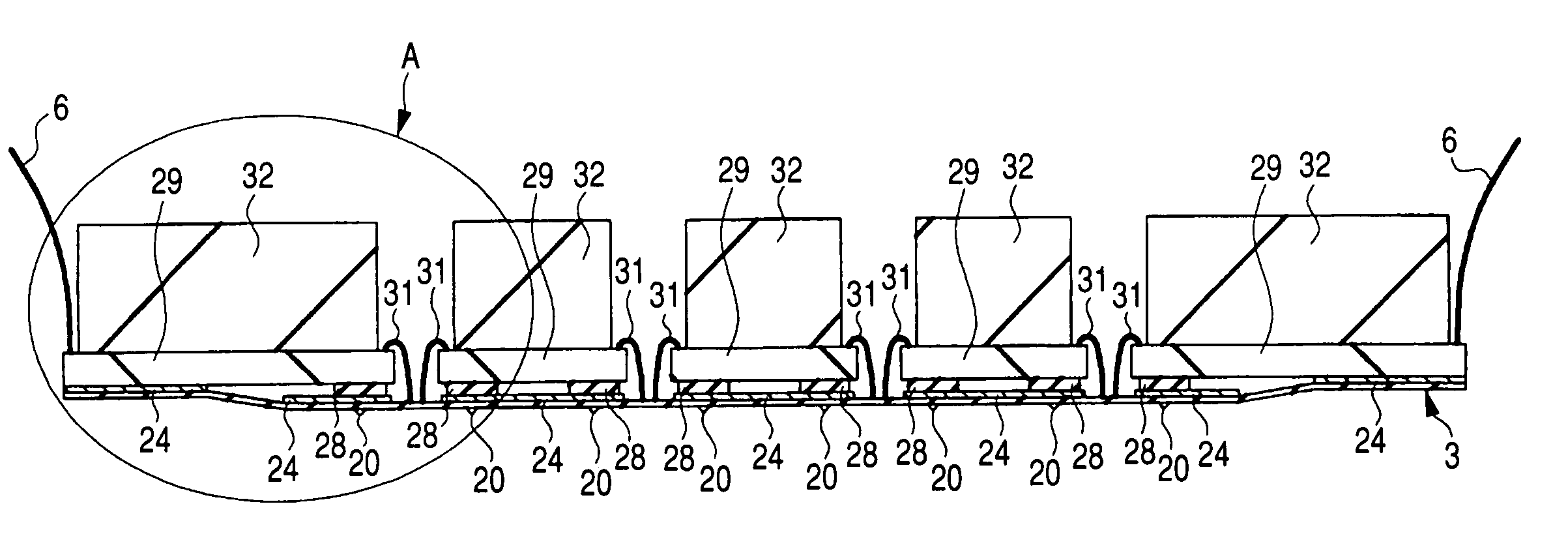

[0176] Among the electrodes (test pads) formed on the main face of the wafer to be inspected, there are some through which relatively large currents flow, including for instance power supply wiring and ground wiring. In this Embodiment 2, as shown in FIG. 28, a plurality of wires 31 are bonded between the bonding pads 21A electrically connected to the probes 20 which come into contact with such electrodes (test pads) and the pads 30. The current capacity between the bonding pads 21A and the pads 30, in which relatively large currents flow, can be enlarged.

[0177] The electrical load on the probes 20 in contact with the electrodes (test pads) in which relatively large currents flow, if formed in the same size as other probes 20, will also be greater. If this electrical load is greater, there may arise such troubles that those probes 20 are heated and welded onto the electrodes (test pads) or are broken. In...

embodiment 3

(Embodiment 3)

[0181] Now, an Embodiment 3 of the invention will be described.

[0182] As shown in FIG. 33, a probe card of this Embodiment 3 is configured by fitting, over the glass epoxy substrate 29 (see also FIG. 4) in the probe card of Embodiment 1, electronic elements 71 electrically connected to a circuit (wiring) formed within the glass epoxy substrate 29. Conceivable examples of the electronic elements 71 in this Embodiment 3 include elements that can constitute relays, capacitors and built-out self test (BOST) circuits (second circuits). The shorter these electronic elements 71 are in electrical distance from the probes 20, the better they will be able to transmit electrical characteristics, such as analog clocks. For this reason, the electronic elements 71 can achieve better electrical characteristics when they are fitted to the glass epoxy substrate 29 than when they are fitted to, for instance, the multi-layered wiring board 1 (see FIG. 1 and FIG. 2).

[0183] Where the ele...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More