Flash ADC receiver with reduced errors

a technology of flash adc and receiver, which is applied in the field of reducing decoding errors, can solve the problems of world channel imparting distortion to the signal, channel distortion, temporal spreading of the signal, etc., and achieve the effect of reducing the decoding errors of symbols at the receiver utilising flash analog to digital converters (adc)

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

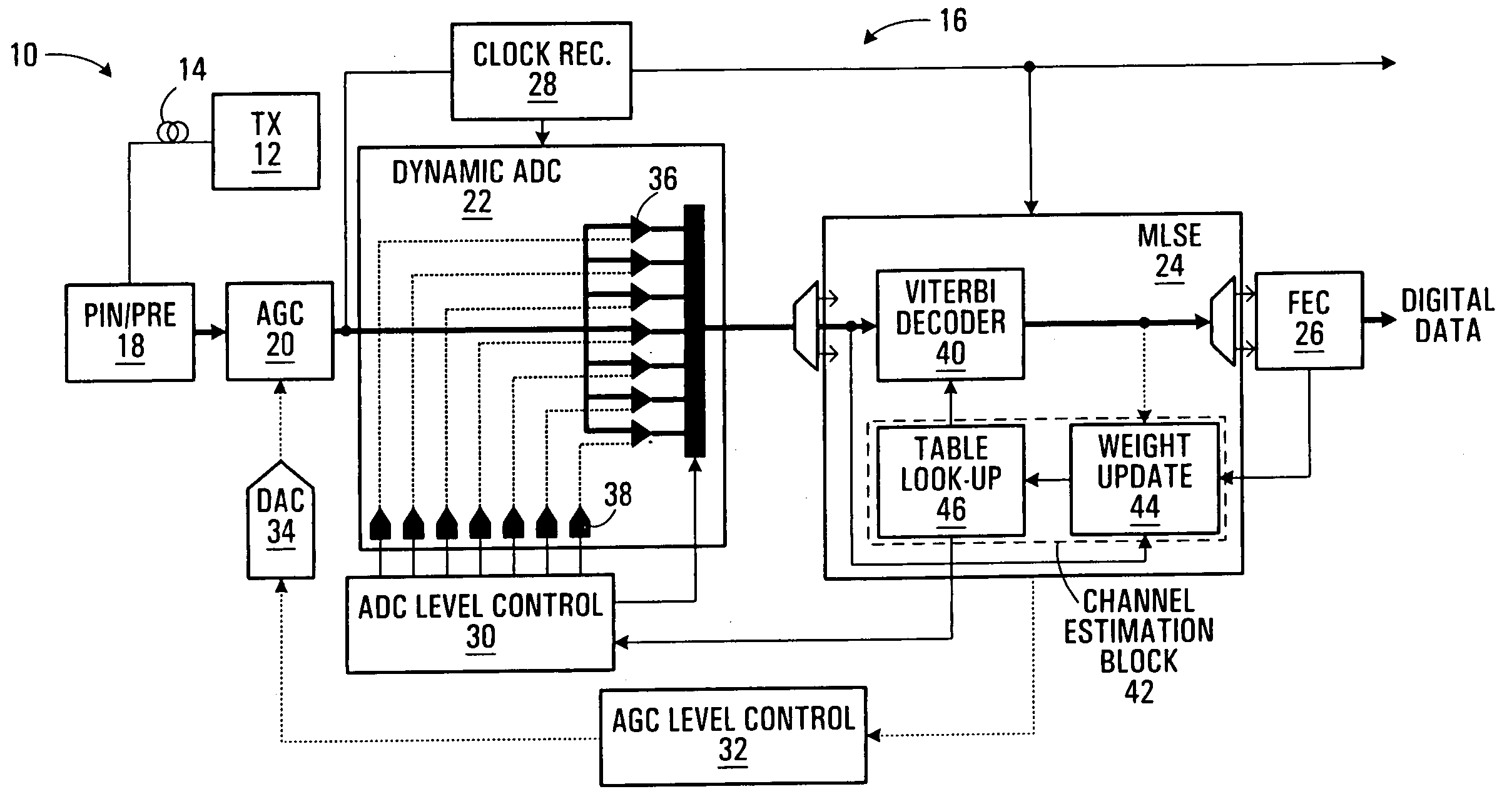

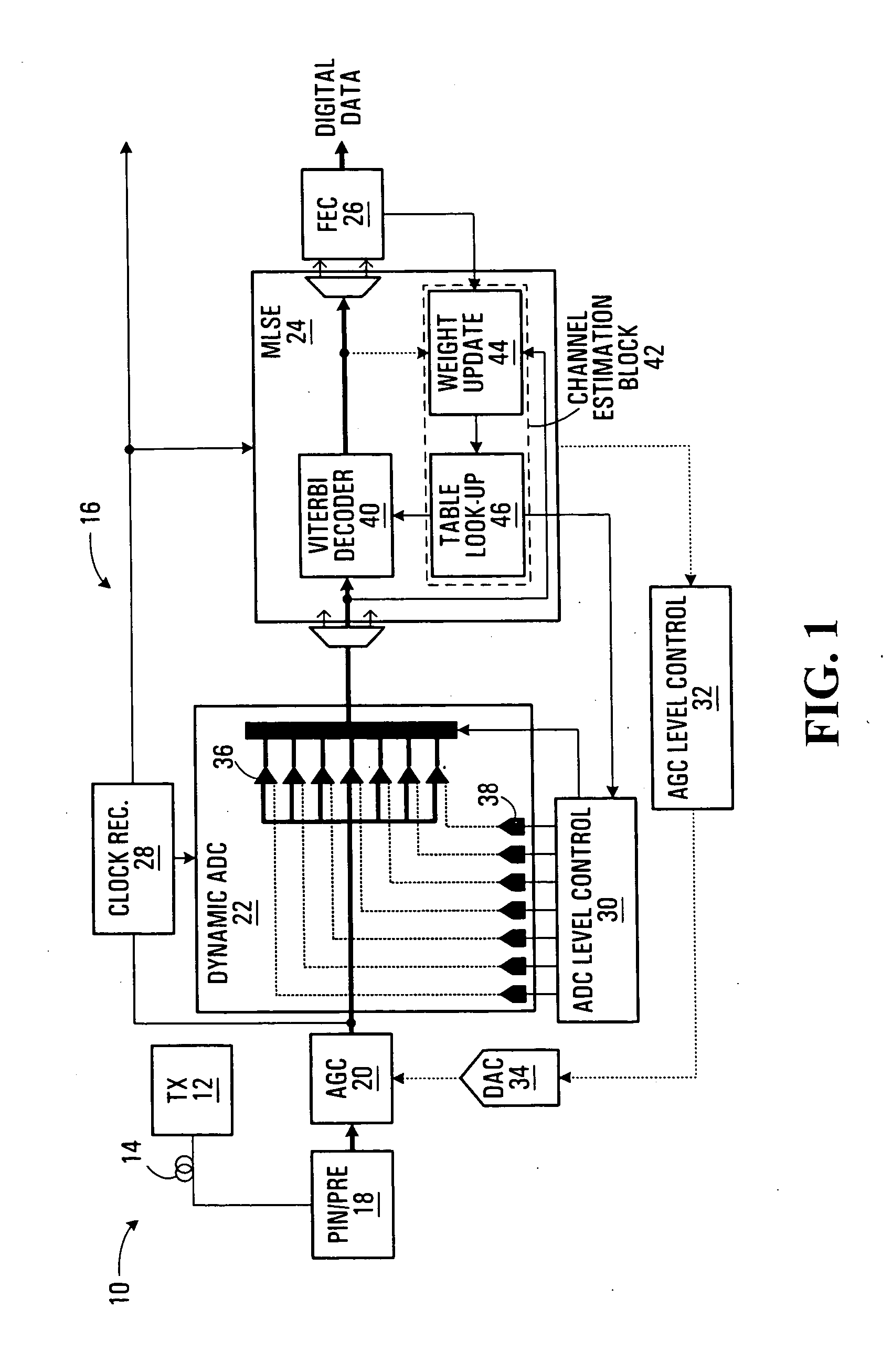

[0017] Turning to FIG. 1, a transmission system 10 comprises a transmitter 12, a channel 14, and a receiver 16. The channel may be, for example, an optical channel on an optical fibre. The receiver may comprise a serially arranged pre-processing block 18, adaptive gain controller (AGC) 20, flash ADC 22, equaliser 24, and forward error corrector (FEC) 26. A clock recovery block 28 may recover a clock signal upstream from the ADC and input the recovered clock to the ADC and the equaliser. The equaliser may output to an ADC level controller 30 which inputs reference voltages to the ADC 22. The equaliser 24 may also output to an AGC level controller 32, which in turn outputs to the AGC 20 through a digital to analog converter (DAC) 34. Each of the preprocessor 18, AGC level controller 32, and AGC 20 operate in a conventional manner and so is not further described herein.

[0018] As illustrated, the flash ADC 22 has (22−=1=) seven comparators 36, each input by any signal at the AGC 20. Th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More