Semiconductor device and method of fabrication thereof

a technology of semiconductor devices and semiconductor layers, applied in the direction of semiconductor devices, basic electric elements, electrical apparatus, etc., can solve the problems of affecting device operation performance, reliability and the like, and the characteristic of the silicon layer that contacts the first silicon layer thus deposited is impaired, so as to achieve the effect of improving device operation performan

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

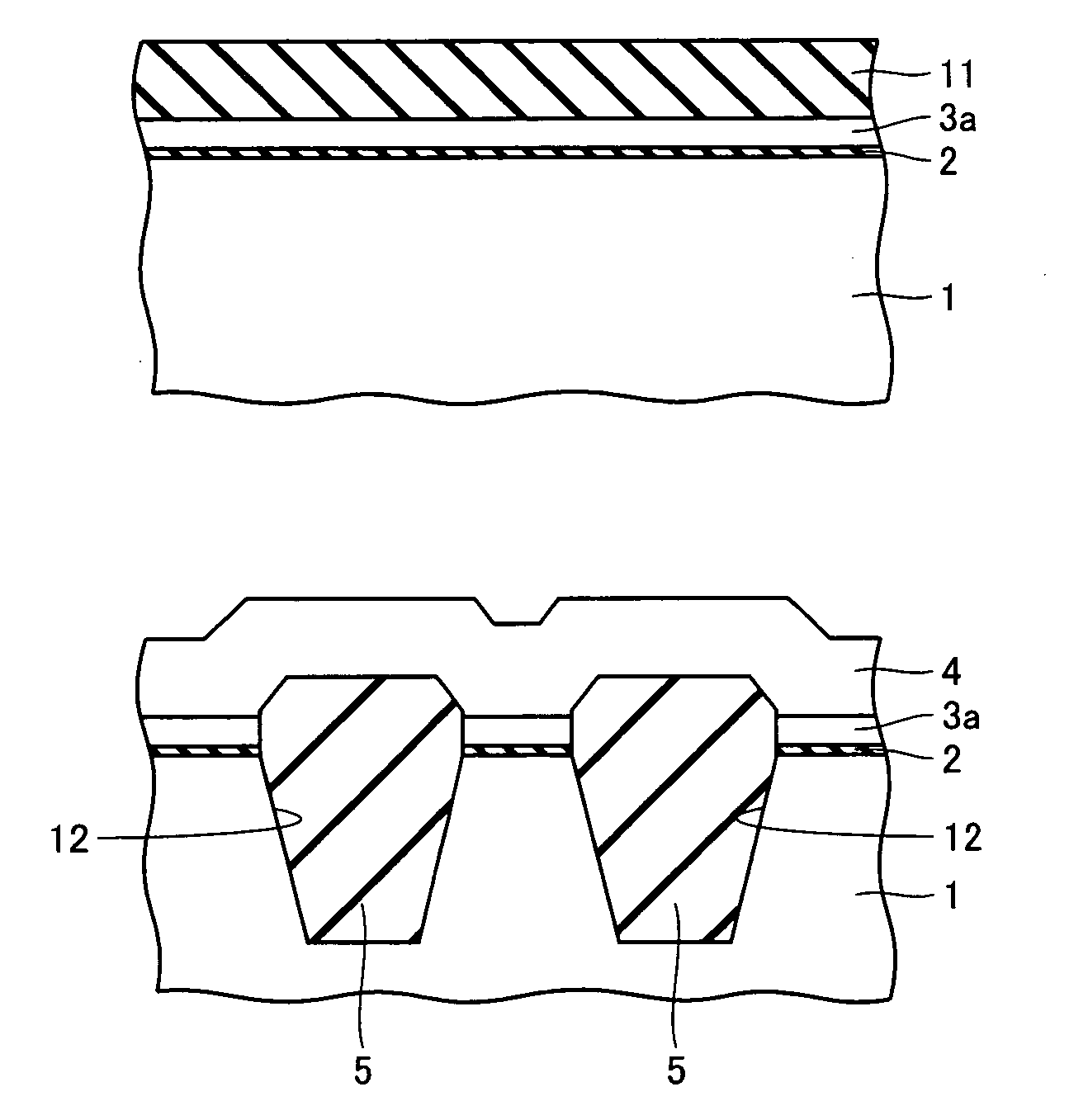

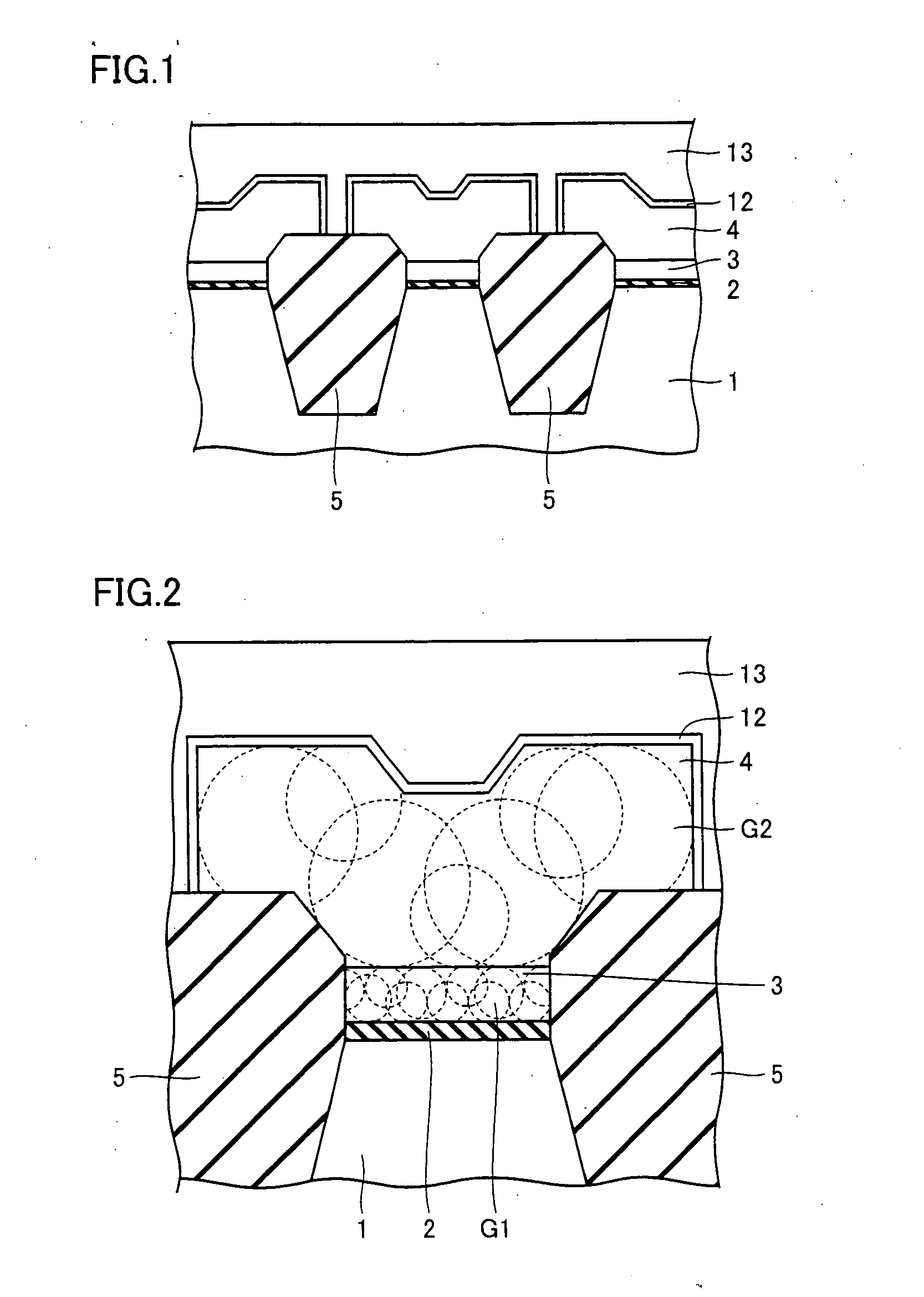

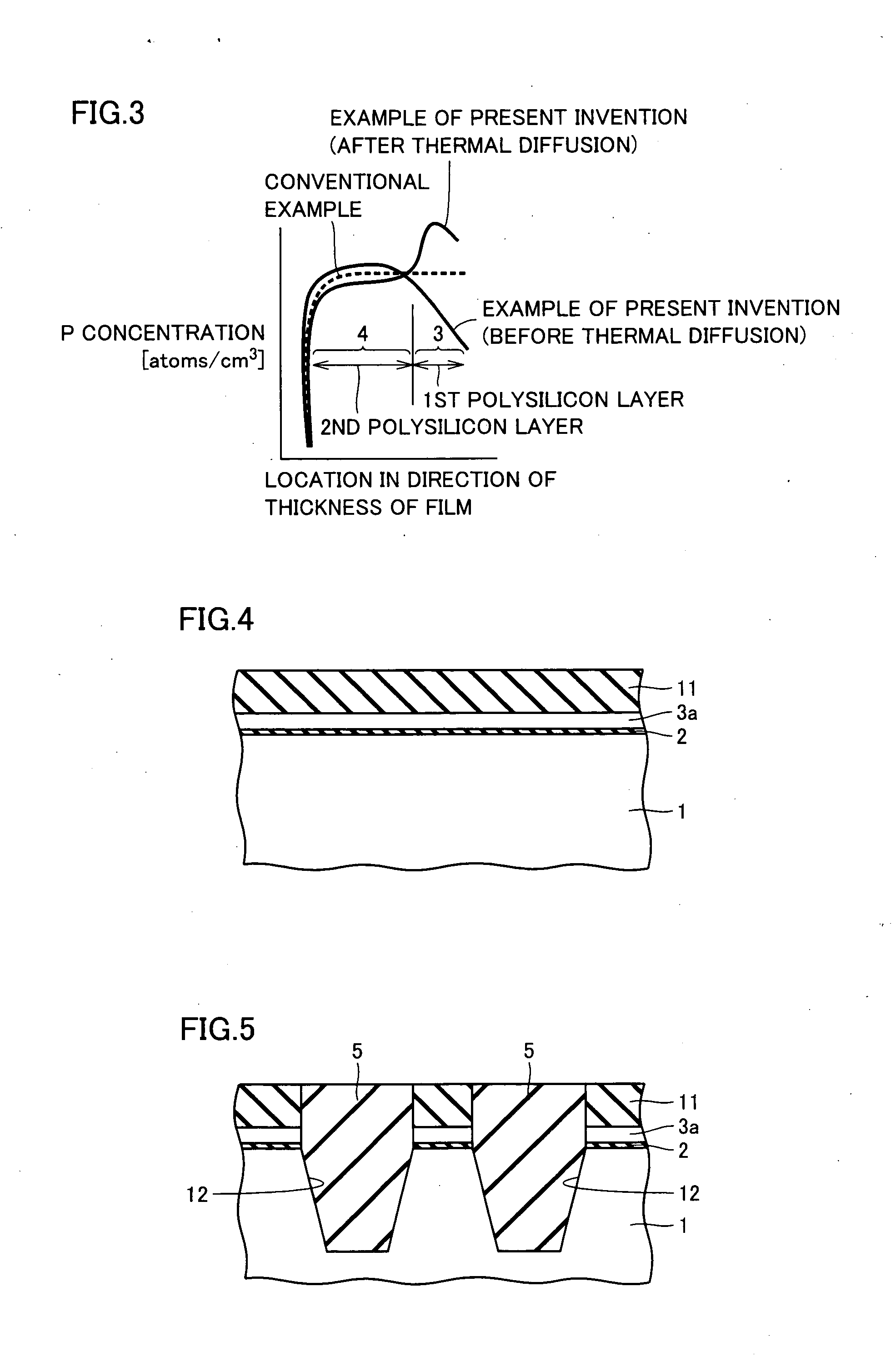

[0031]FIG. 1 is a cross section of the present nonvolatile memory device in a first embodiment as fabricated by SA-STI. In the figure, a semiconductor substrate 1 is provided with a plurality of element isolating insulation films (STIs) 5. Between STIs 5 is located an active region having a tunnel insulation film arranged thereon to form a gate insulation film 2. Furthermore on tunnel insulation film 2 a first silicon layer 3 and a second silicon layer 4 are deposited in layers to act as a floating gate, and thereon a control gate 13 is provided with an interlayer dielectric film 12 posed therebetween. Note that the first silicon layer 3 is located between two isolating insulation films 5 protruding above semiconductor substrate 1 and preferably has a thickness to have a height smaller than that of that portion of isolating insulation film 5 which protrudes.

[0032]FIG. 2 is a partially enlarged view of FIG. 1. In the present embodiment, as shown in FIG. 2, tunnel insulation film 2 c...

second embodiment

[0044] The present invention in a second embodiment is characterized in that the first polysilicon layer is increased in thickness and in addition thereto the first embodiment's satisfactory characteristic can be obtained. In the first embodiment a device structure, a method of fabrication and the like can require that the first silicon layer have a thickness of at least 50 nm. In that case, using amorphous silicon results in a crystal grain size increasing with film thickness and the present invention's object cannot be achieved. For such large film thickness, originally forming a polysilicon layer having a thickness in a range, as described hereinafter, allows as small a crystal grain size as approximately at most 30 nm.

[0045] More specifically, if the first polysilicon layer as originally deposited has a thickness set to be 50 to 70 nm, depositing the film at 600 to 650° C., preferably 620 to 630° C. allows the present invention's object to be achieved. Furthermore, if the first...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More