Display

a display and display technology, applied in the field of display, can solve the problems of disadvantageous input of on-state at unintentional timing, shift register circuit disadvantageous output, and unintentional timing of /b>, etc., to suppress fluctuation, suppress destabilization of operations, and suppress occurrence

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

[0056] (First Embodiment)

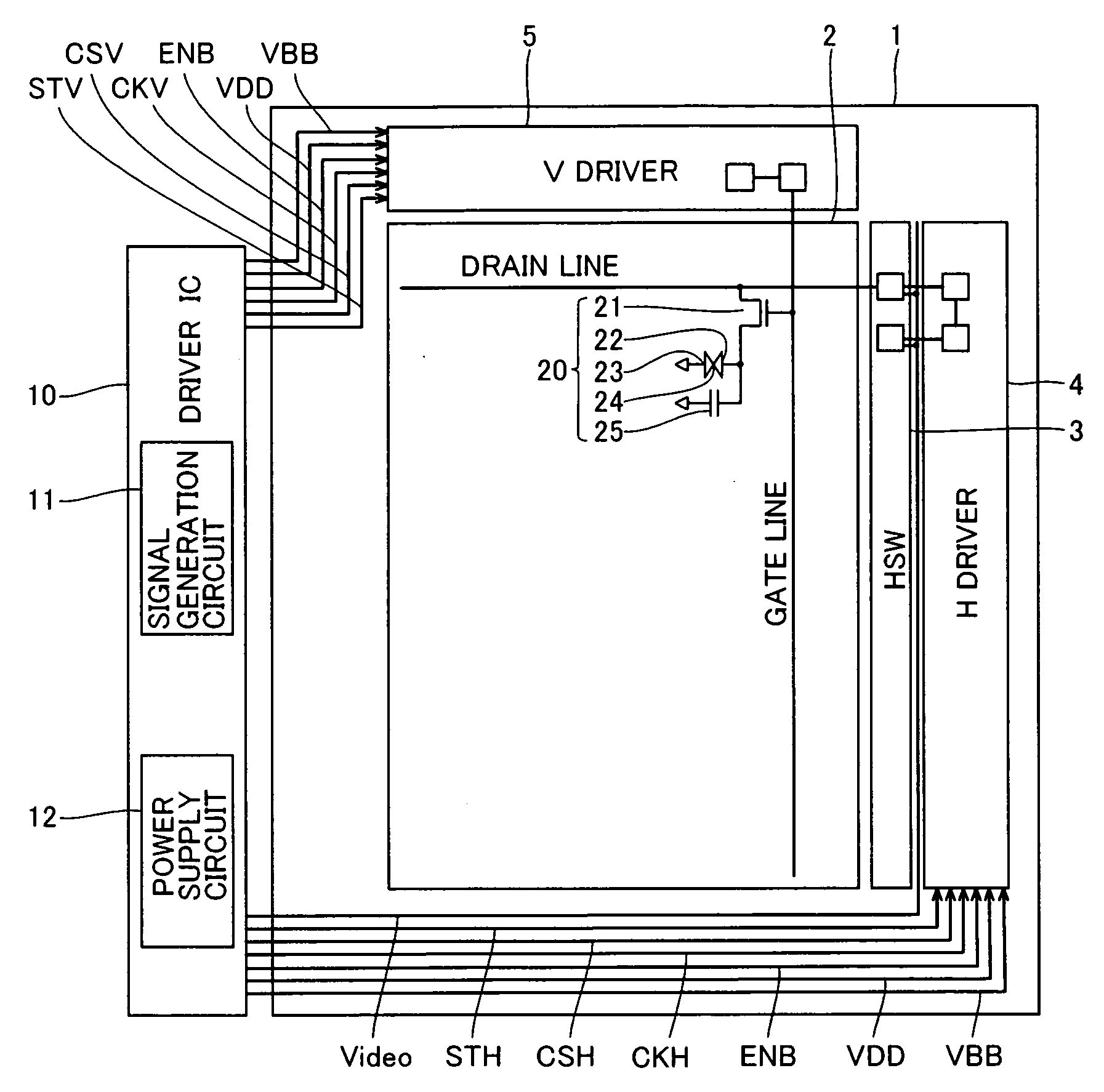

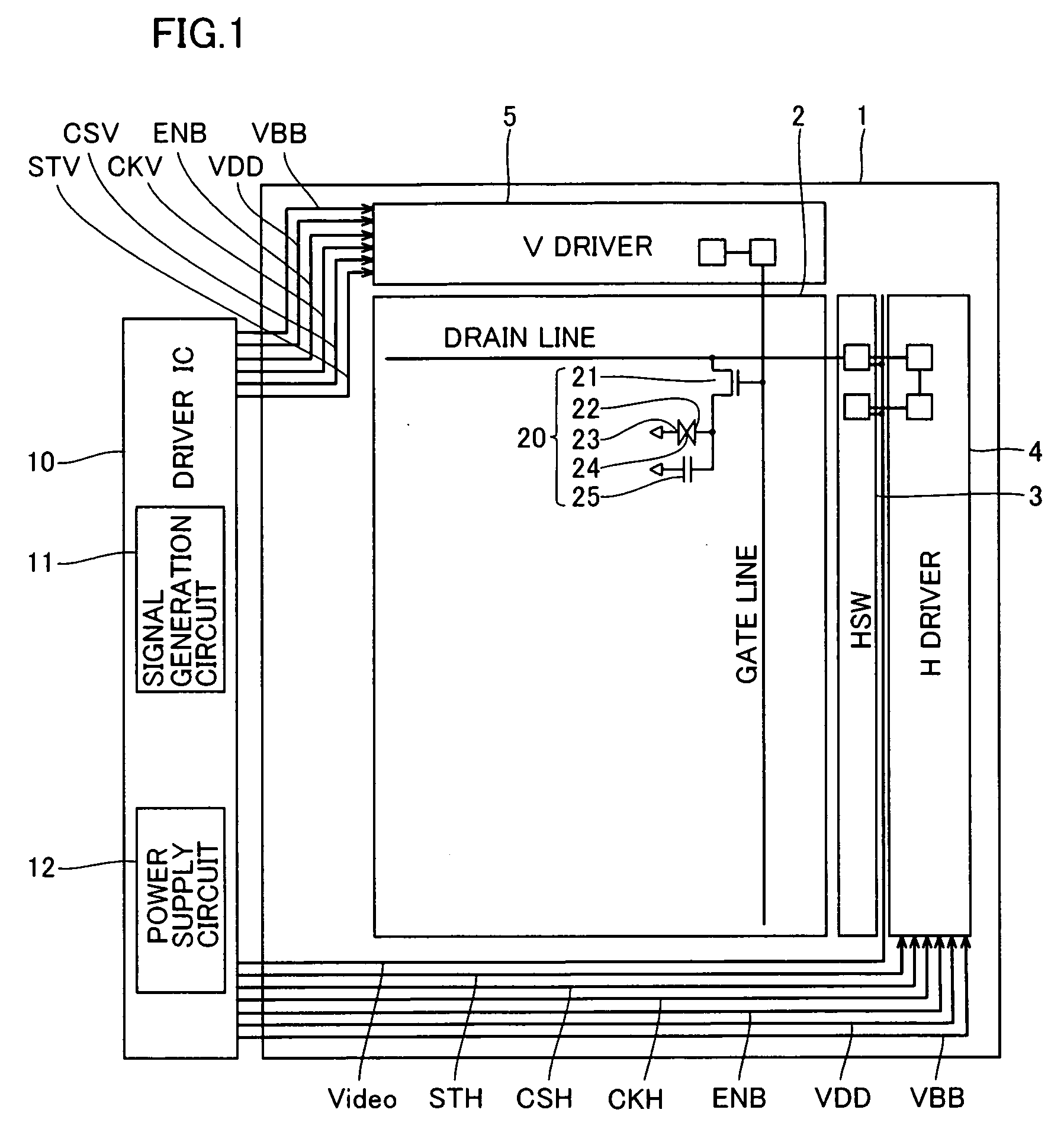

[0057]FIG. 1 is a plan view showing a liquid crystal display according to a first embodiment of the present invention. Referring to FIG. 1, a display portion 2 is provided on a substrate 1 in the liquid crystal display according to the first embodiment. Pixels 20 are arranged on the display portion 2 in the form of a matrix. FIG. 1 shows only one of the pixels 20, in order to simplify the illustration. Each pixel 20 is constituted of an n-channel transistor 21 (hereinafter referred to as a transistor 21), a pixel electrode 22, a common electrode 23, opposed to the pixel electrode 22, common to each pixel 20, a liquid crystal 24 held between the pixel electrode 22 and the common electrode 23 and a subsidiary capacitor 25. The source of the transistor 21 is connected to the pixel electrode 22 and the subsidiary capacitor 25, while the drain thereof is connected to a drain line. The gate of the transistor 21 is connected to a gate line.

[0058] Horizontal switch...

second embodiment

[0162] (Second Embodiment)

[0163] Referring to FIGS. 4 and 5, a V driver 5a similar to the V driver 5 according to the aforementioned first embodiment is constituted of p-channel transistors in a liquid crystal display according to a second embodiment of the present invention.

[0164] Referring to FIG. 4, a display portion 2a is provided on a substrate la in the liquid crystal display according to the second embodiment. Pixels 20a are arranged on the display portion 2a in the form of a matrix. FIG. 4 shows only one of the pixels 20a, in order to simplify the illustration. Each pixel 20a is constituted of a p-channel transistor 21a (hereinafter referred to as a transistor 21a), a pixel electrode 22a, a common electrode 23a common to each pixel 20a opposed to the pixel electrode 22a, a liquid crystal 24a held between the pixel electrode 22a and the common electrode 23a and a subsidiary capacitor 25a. The source of the transistor 21a is connected to a drain line, while the drain thereof ...

third embodiment

[0189] (Third Embodiment)

[0190] Referring to FIG. 7, a liquid crystal display according to a third embodiment of the present invention supplies a higher voltage supply source VDD to the drains of transistors connected to nodes outputting output signals while holding shift output signals output from logic composition circuit portions in states fixed to low levels through the output signals from the shift register circuit portions in a structure similar to that of the aforementioned first embodiment.

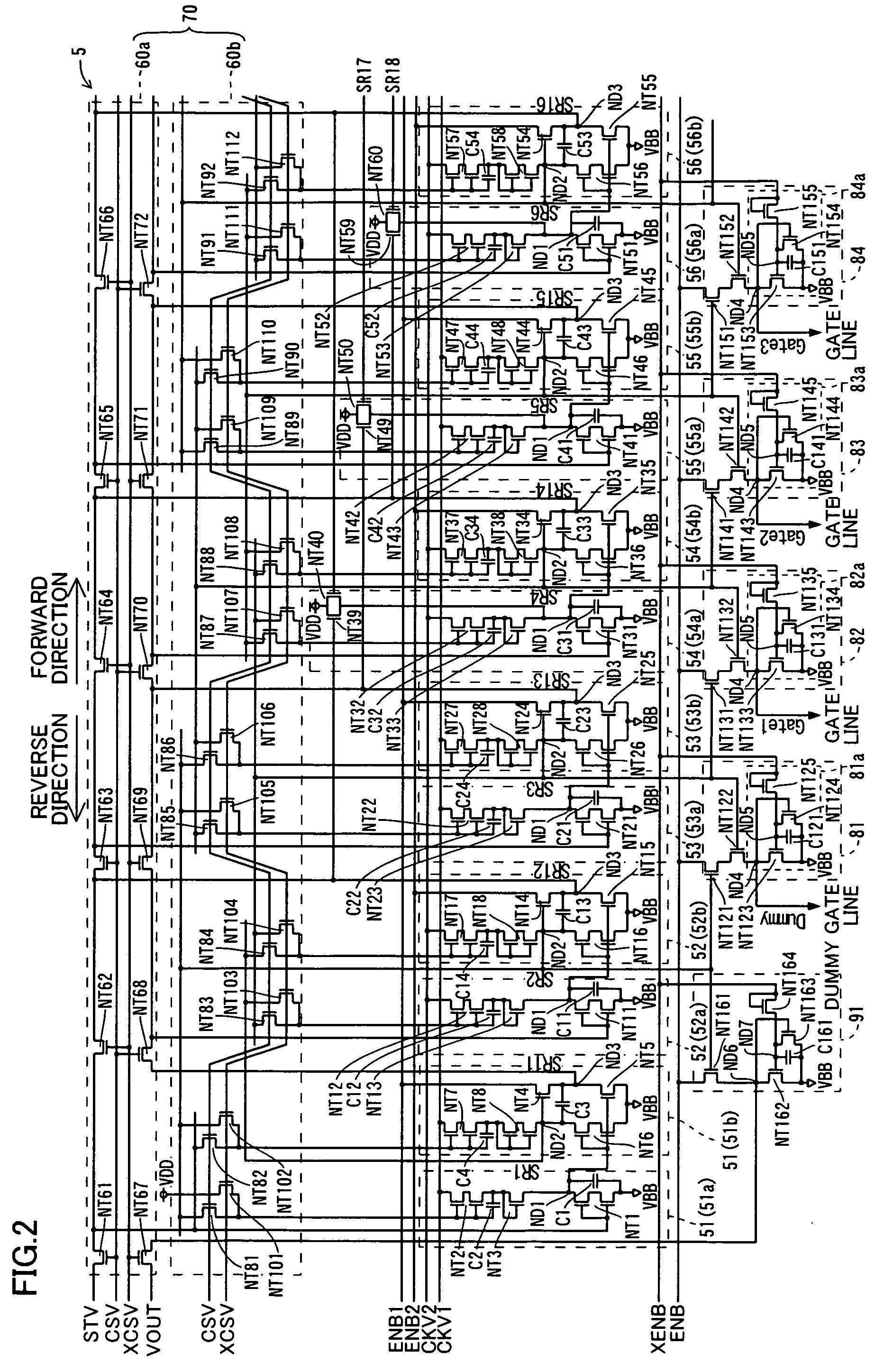

[0191] As shown in FIG. 7, a V driver of the liquid crystal display according to the third embodiment is provided with a plurality of stages of shift register circuit portions 511 to 516, a scanning direction switching circuit portion 710 formed by an output signal input switching circuit portion 610a and a shift signal input switching circuit portion 610b and a plurality of stages of logic composition circuit portions 811 to 814. The shift register circuit portions 512 to 516 are example...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More