Patents

Literature

54results about How to "Manufacturing process is complicated" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Light emitting device

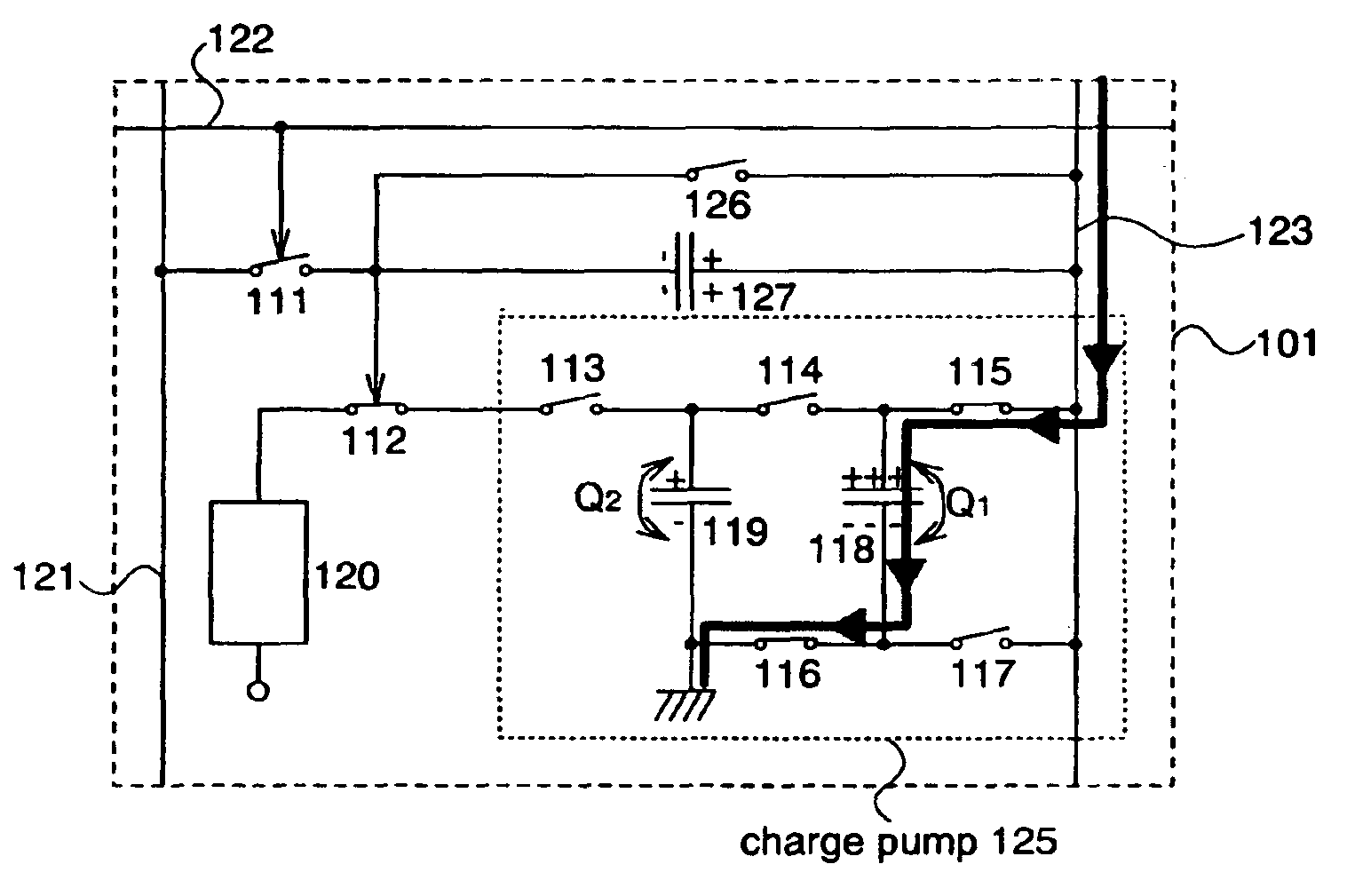

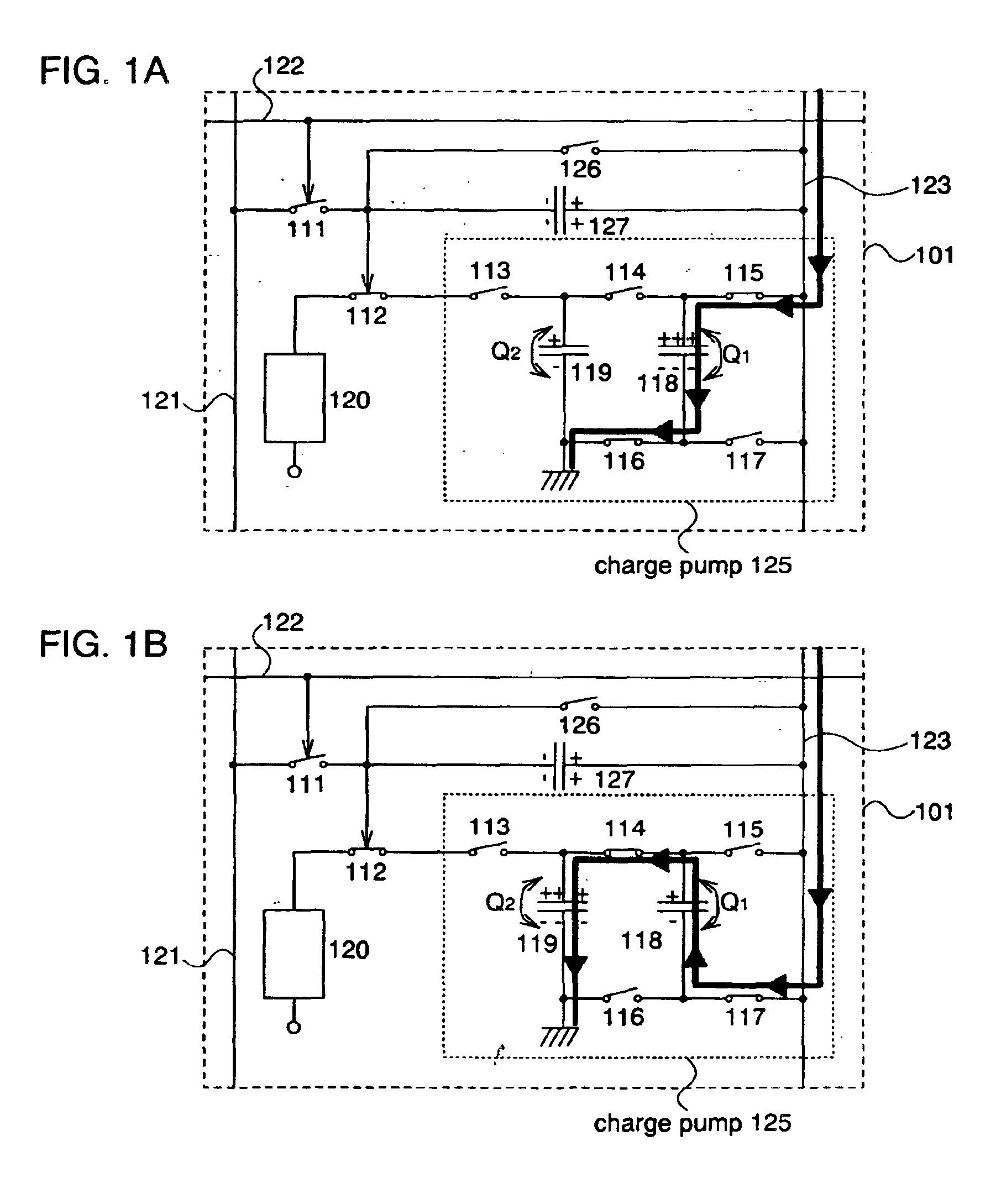

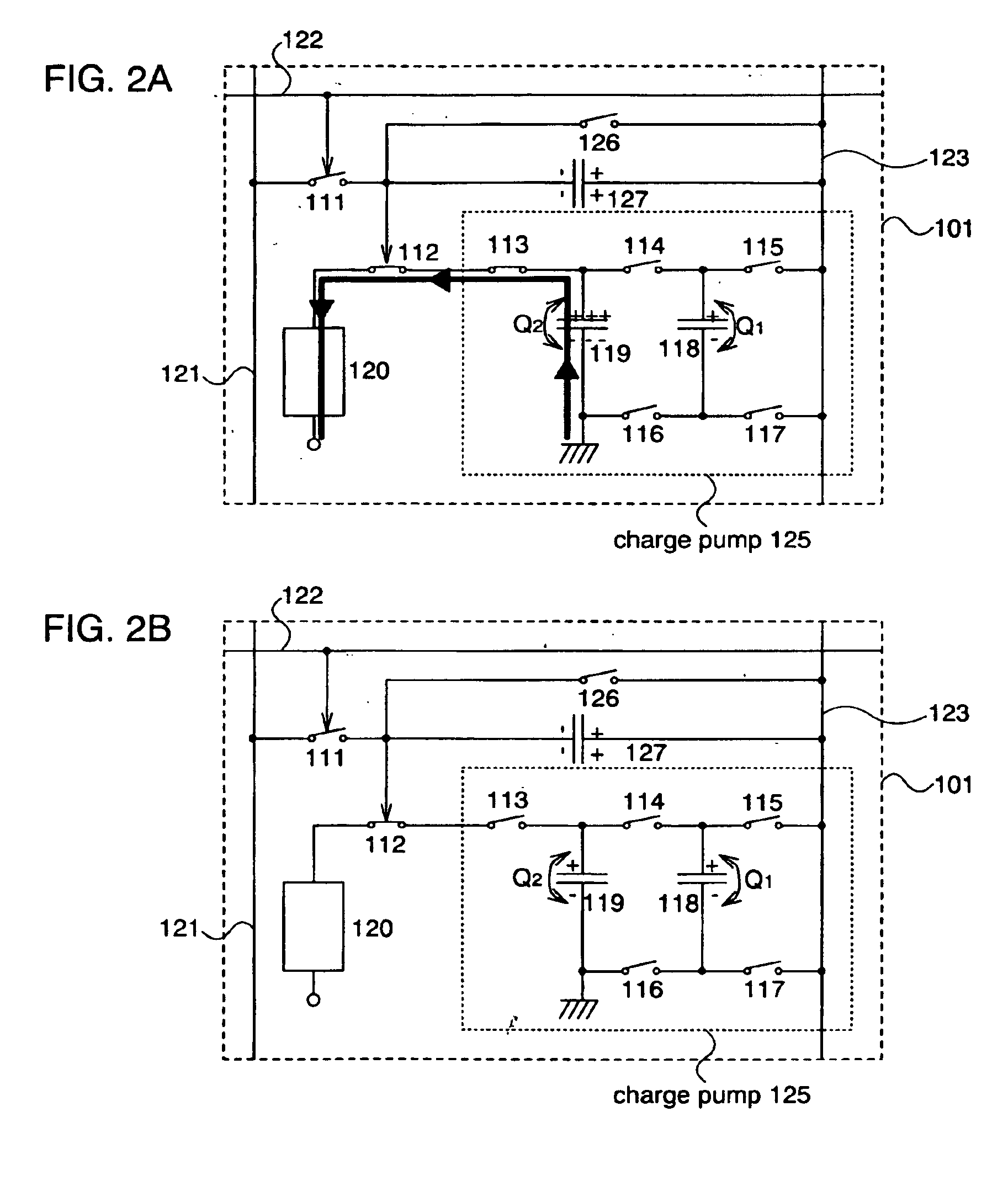

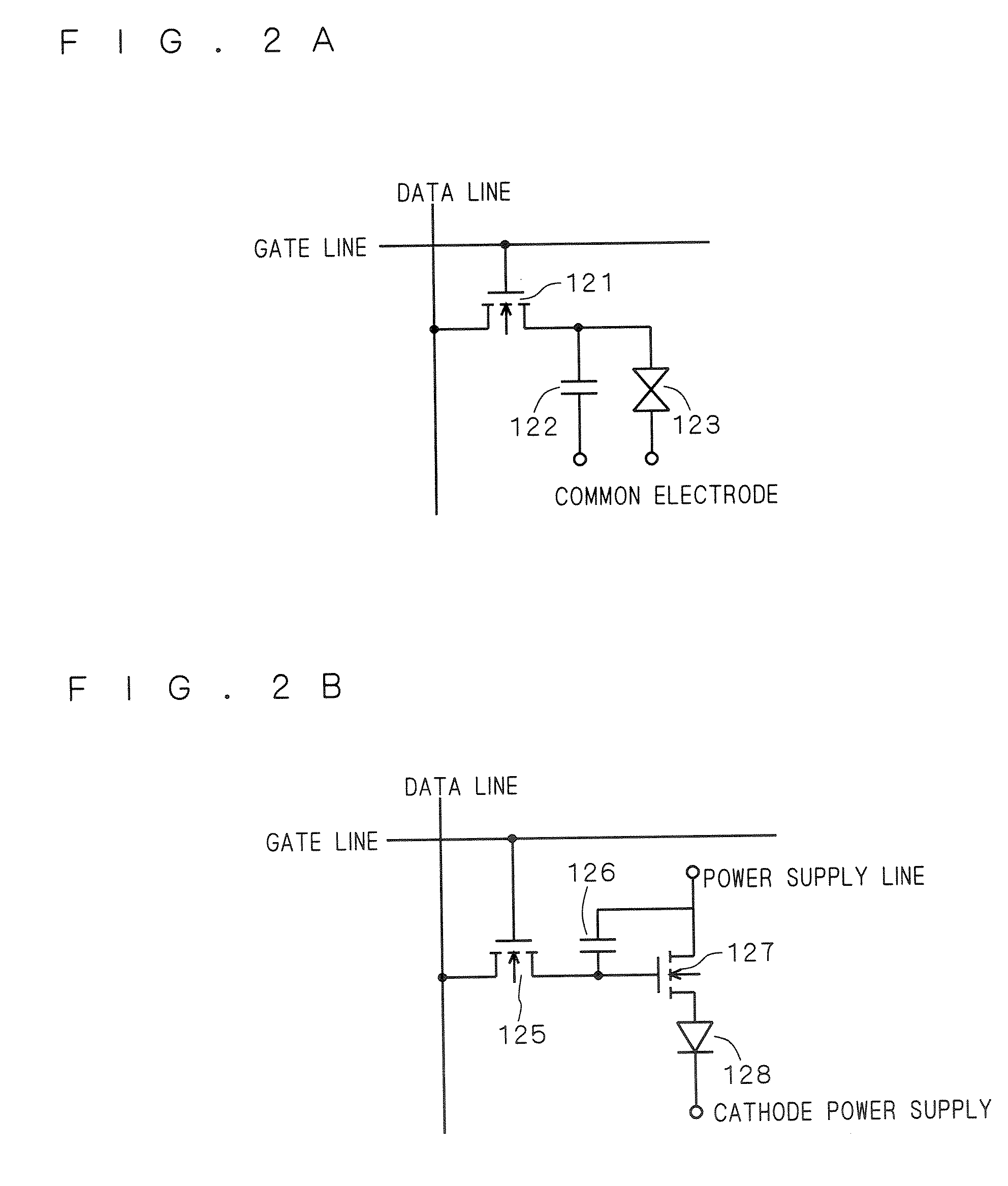

InactiveUS6873116B2Manufacturing process is complicatedInfluence of a variation in characteristics of a driver transistor is suppressedStatic indicating devicesSolid-state devicesLinear regionLight emitting device

In order to suppress the influence of deterioration of a light emitting element resulting from a change over time, the present invention provides a light emitting device in which an electrical circuit for flowing a constant charge between both electrodes of the light emitting element is provided in each pixel. In addition, the present invention provides a light emitting device in which a transistor provided in each pixel is operated in a linear region and used as only a switch, so that the light emitting device is not influenced by a variation in characteristic of the transistor.

Owner:SEMICON ENERGY LAB CO LTD

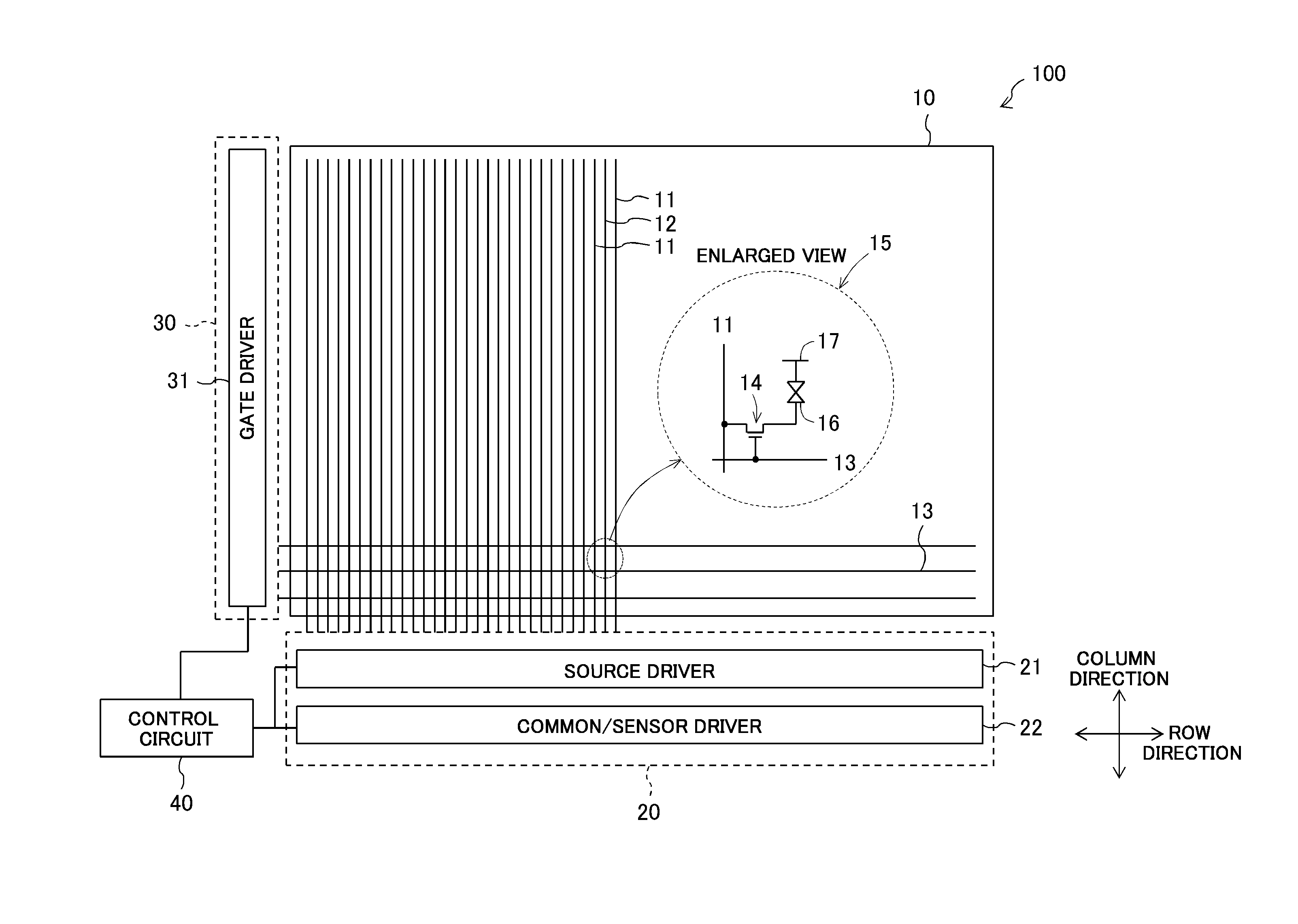

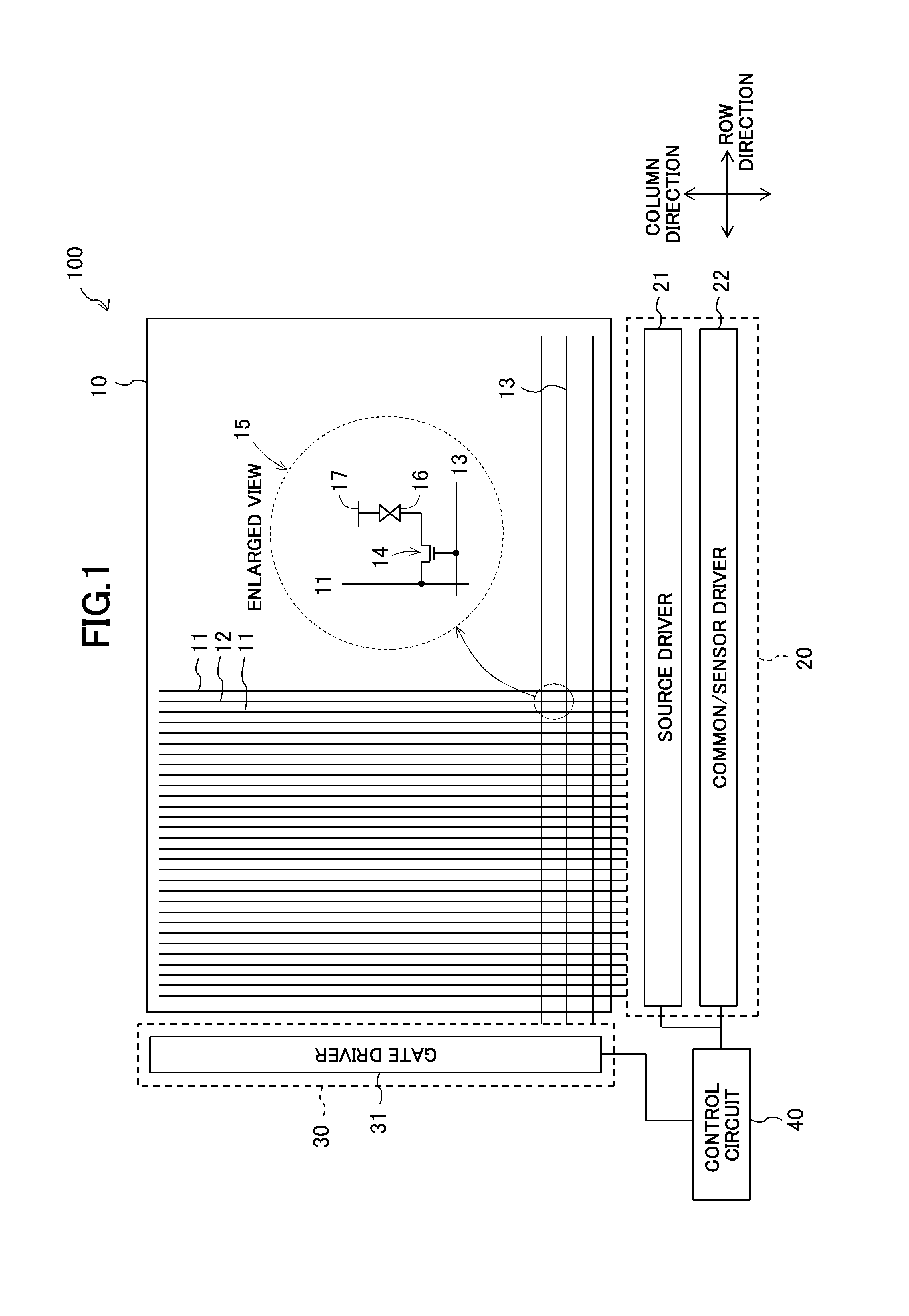

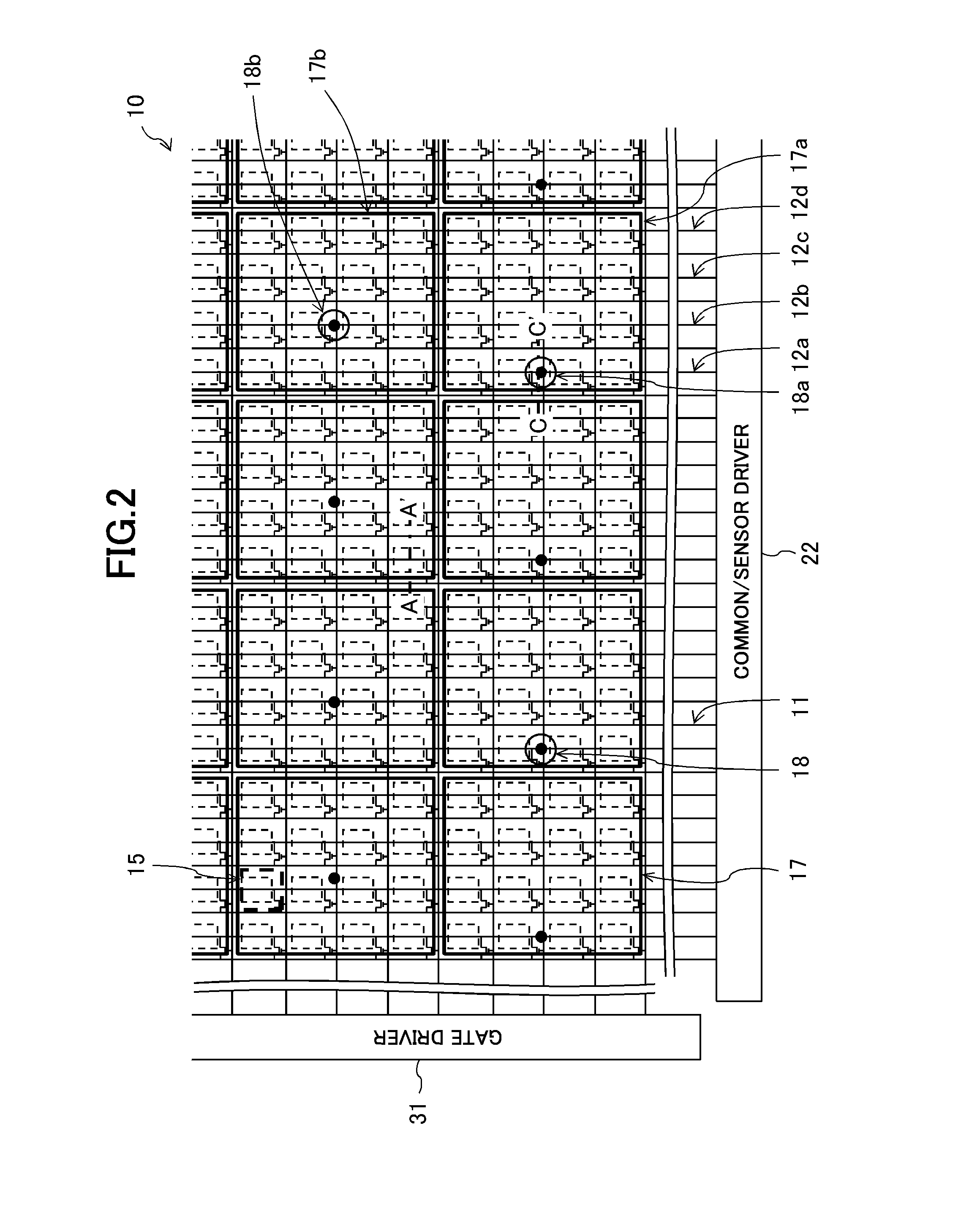

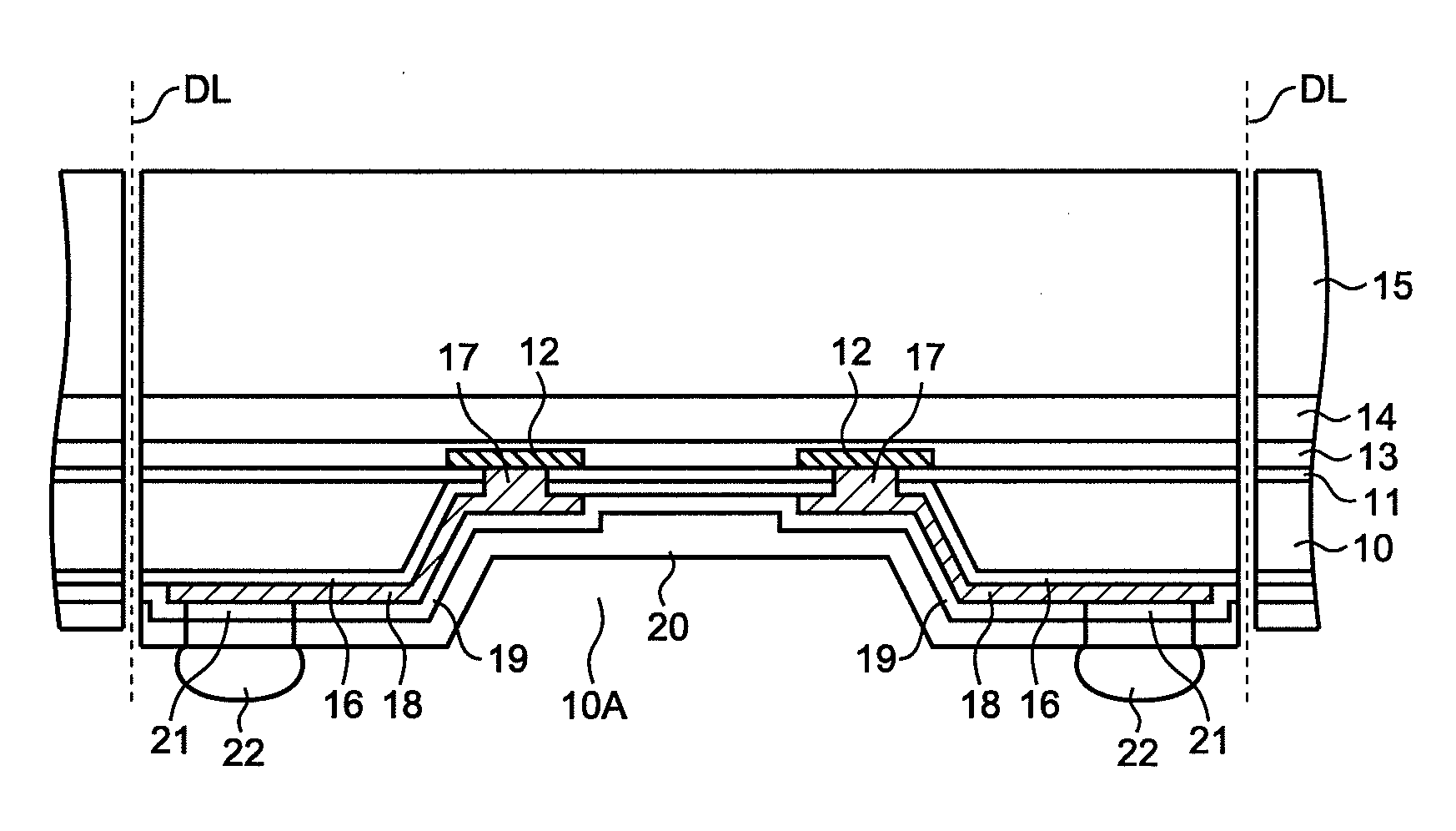

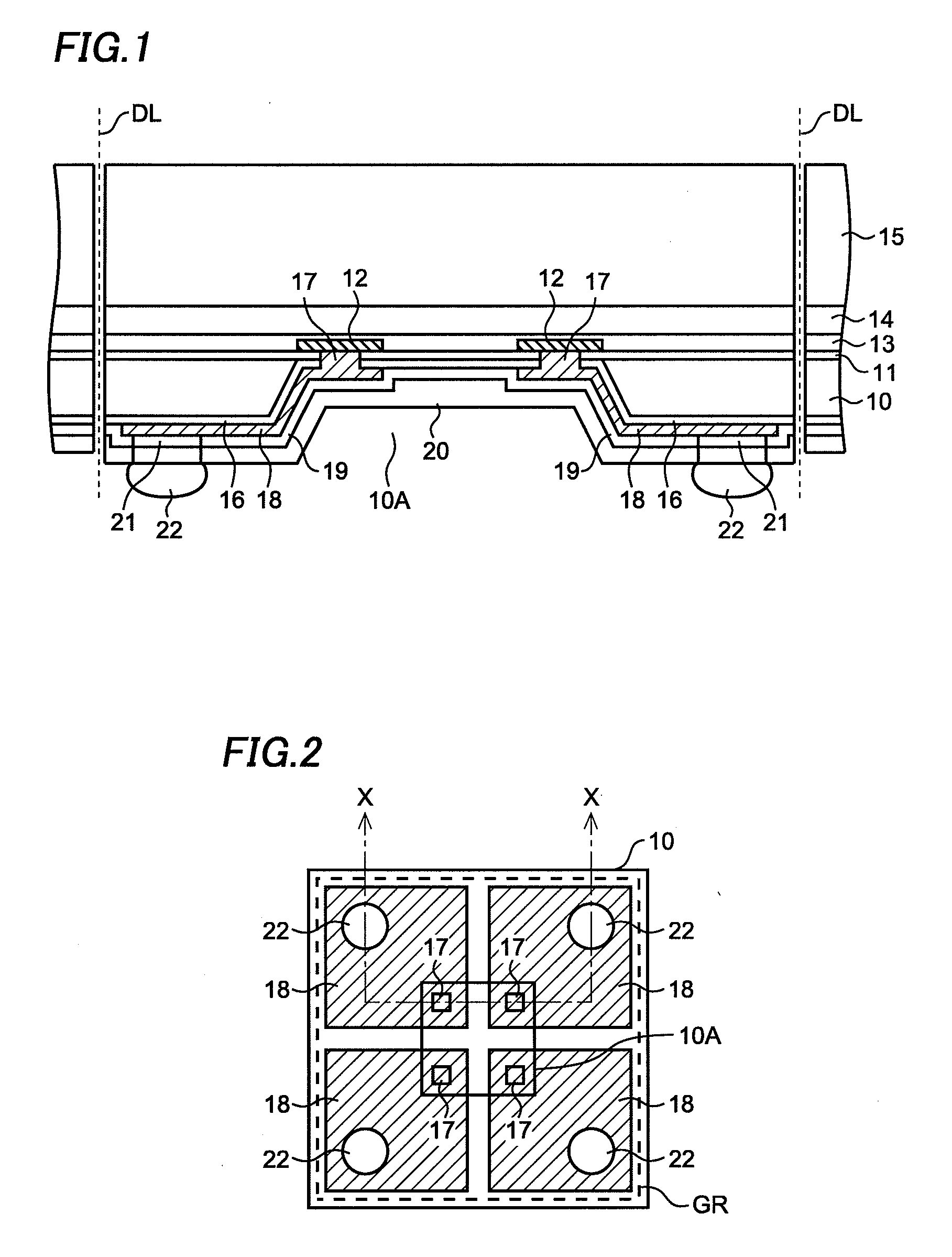

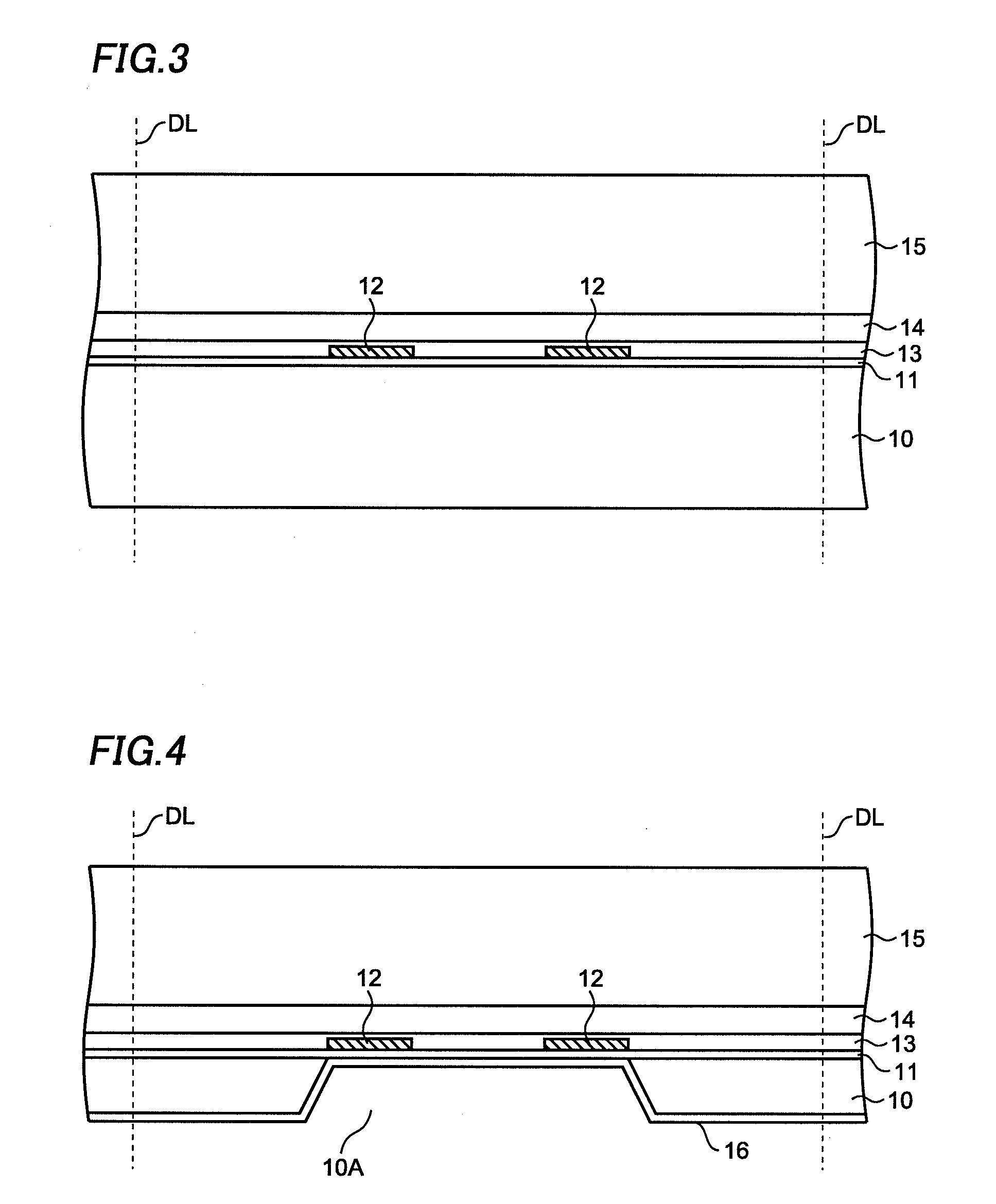

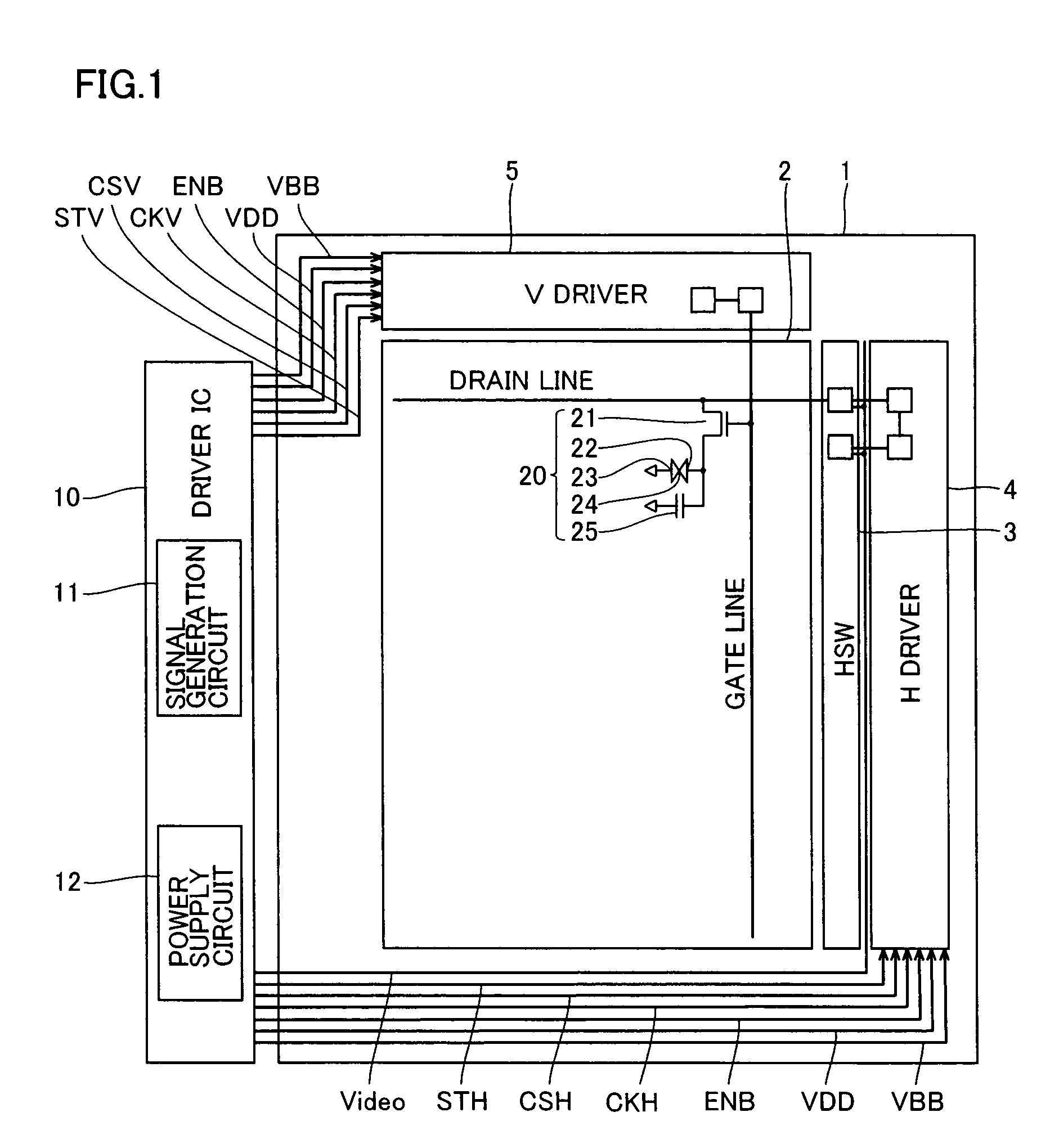

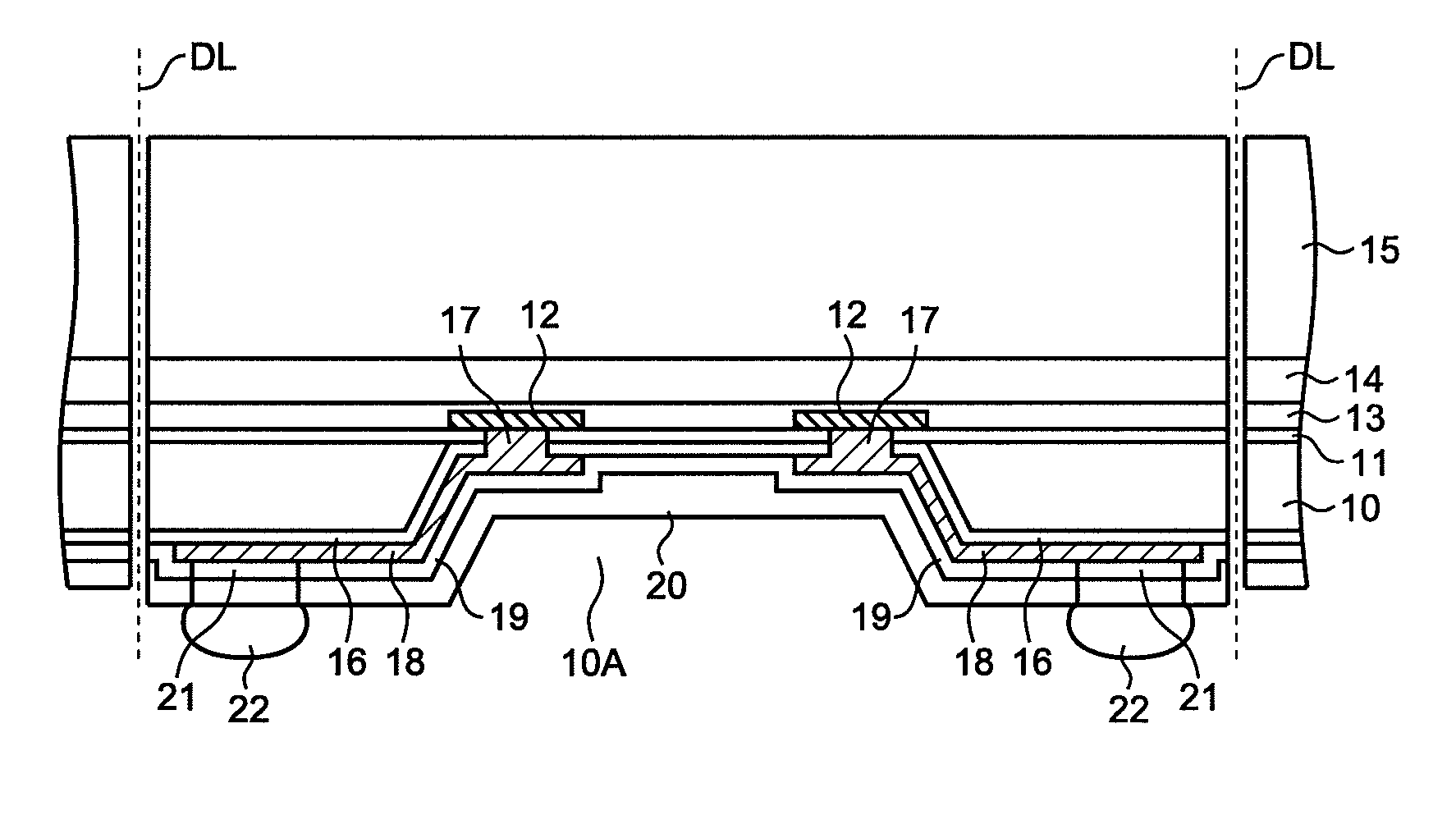

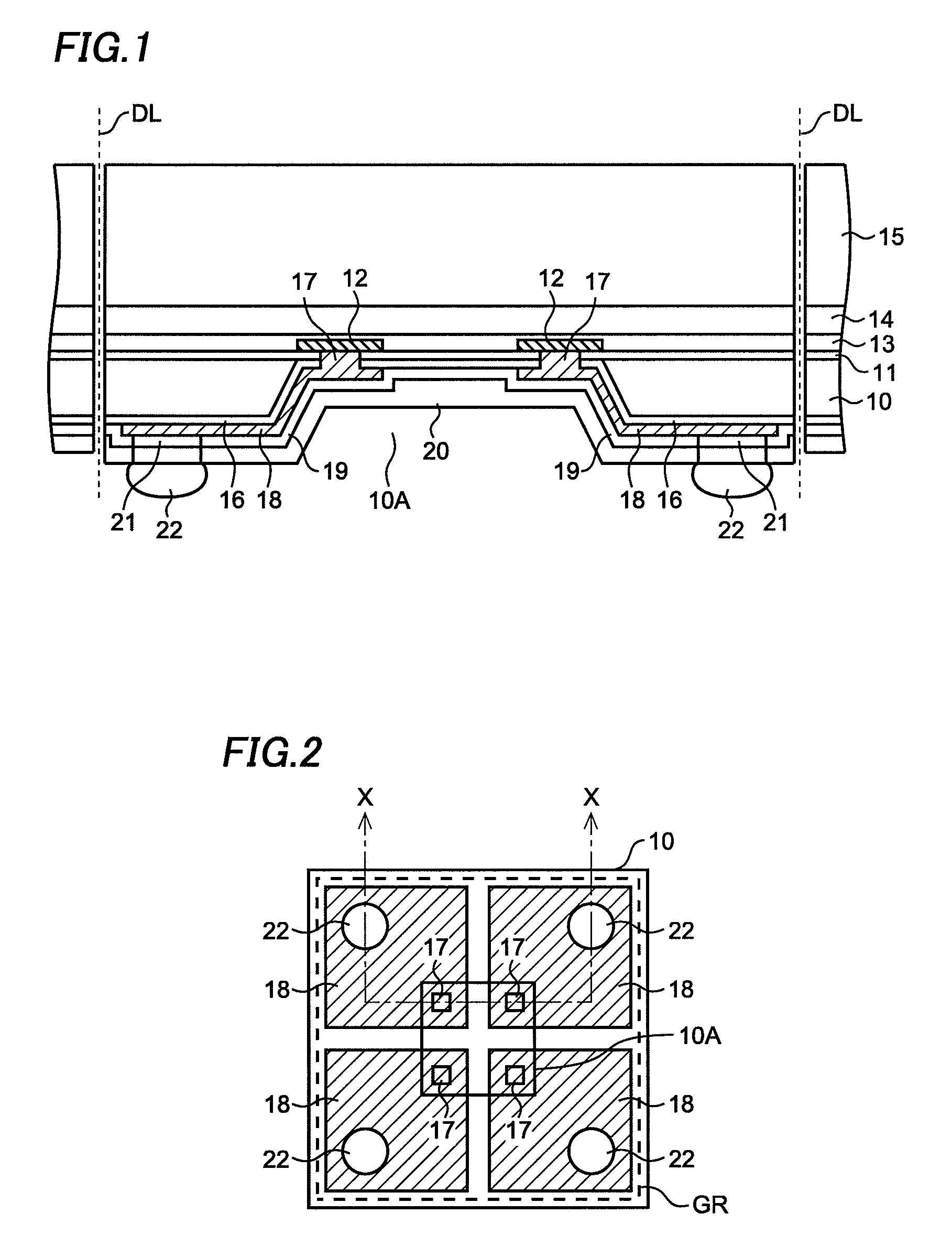

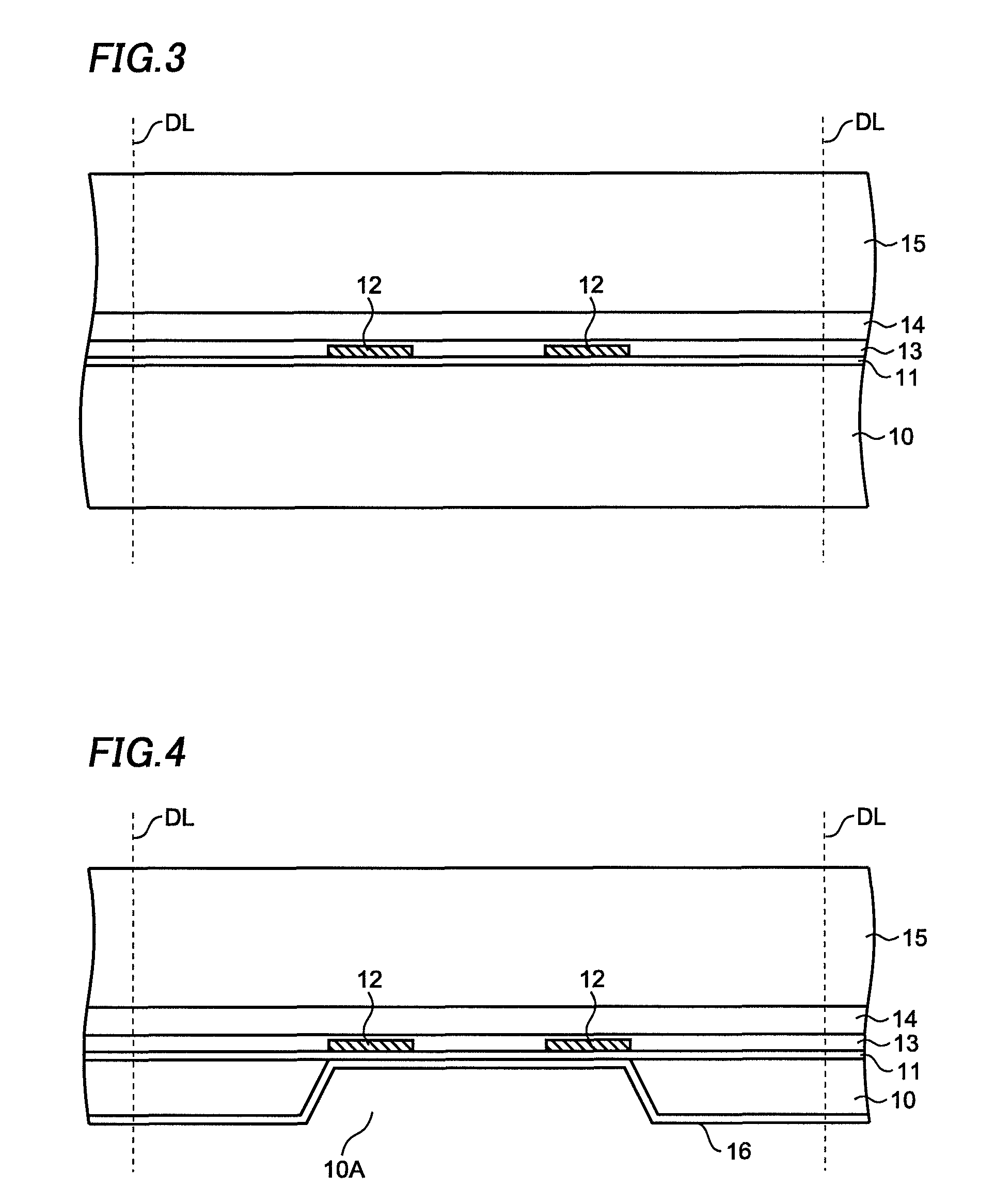

Display panel with touch detection function

InactiveUS20160253024A1Reduce detection accuracyIncrease production costStatic indicating devicesInput/output processes for data processingData signalBiomedical engineering

Provided is a display panel including: a plurality of pixel electrodes divided into a plurality of groups; and a plurality of common electrodes arranged at a ratio of one to a plurality of pixel electrodes included in one of the plurality of groups. A plurality of sensor electrode lines are arranged in the same layer as a plurality of data signal lines. The plurality of sensor electrode lines and each of the plurality of common electrodes overlap each other in plan view. The each of the plurality of common electrodes is electrically connected to at least one of the plurality of sensor electrode lines. At least one insulating film is formed between each of a region between the data signal lines and the sensor electrode lines, a region between the sensor electrode lines and the common electrodes, and a region between the common electrodes and the pixel electrodes.

Owner:PANASONIC LIQUID CRYSTAL DISPLAY CO LTD +1

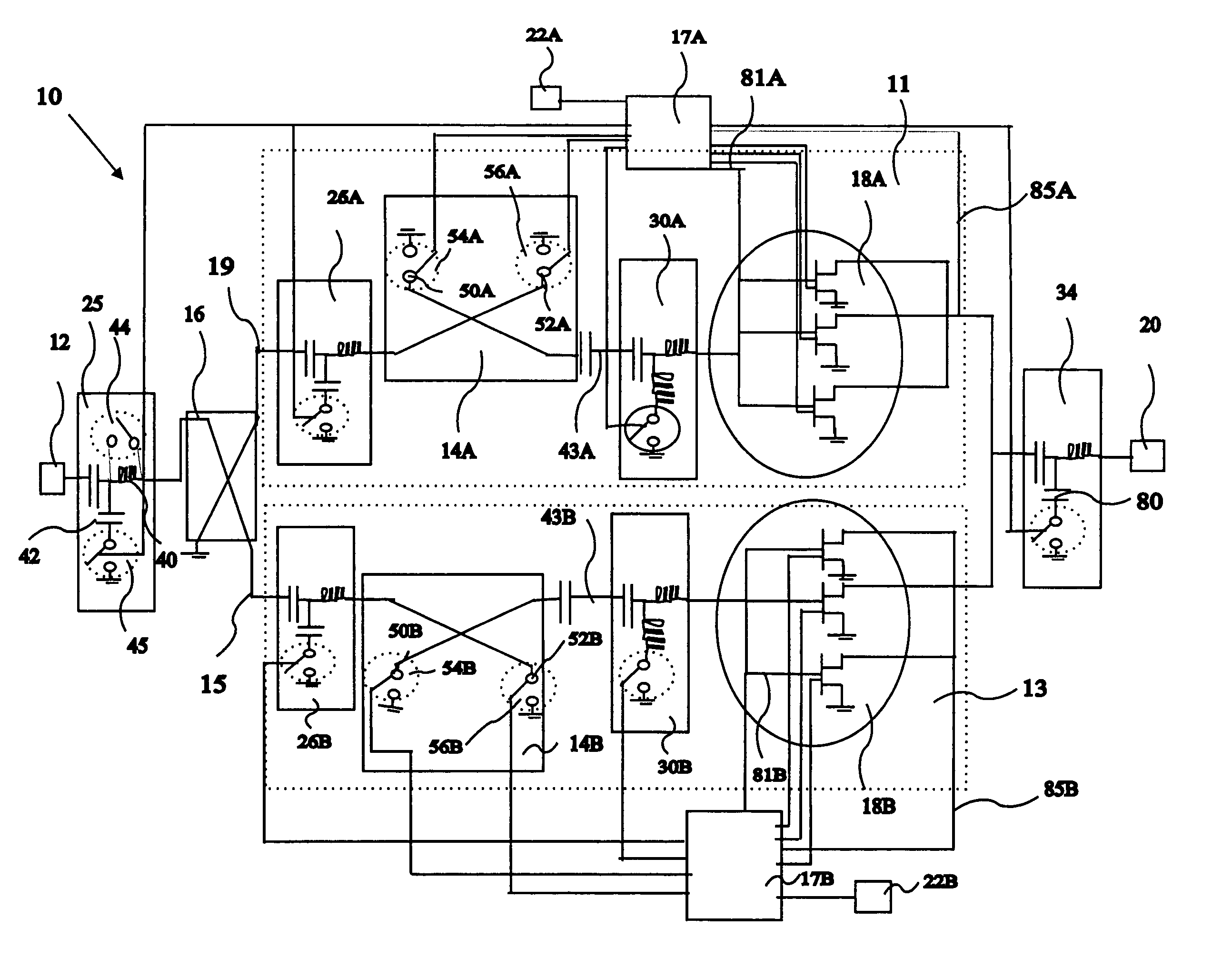

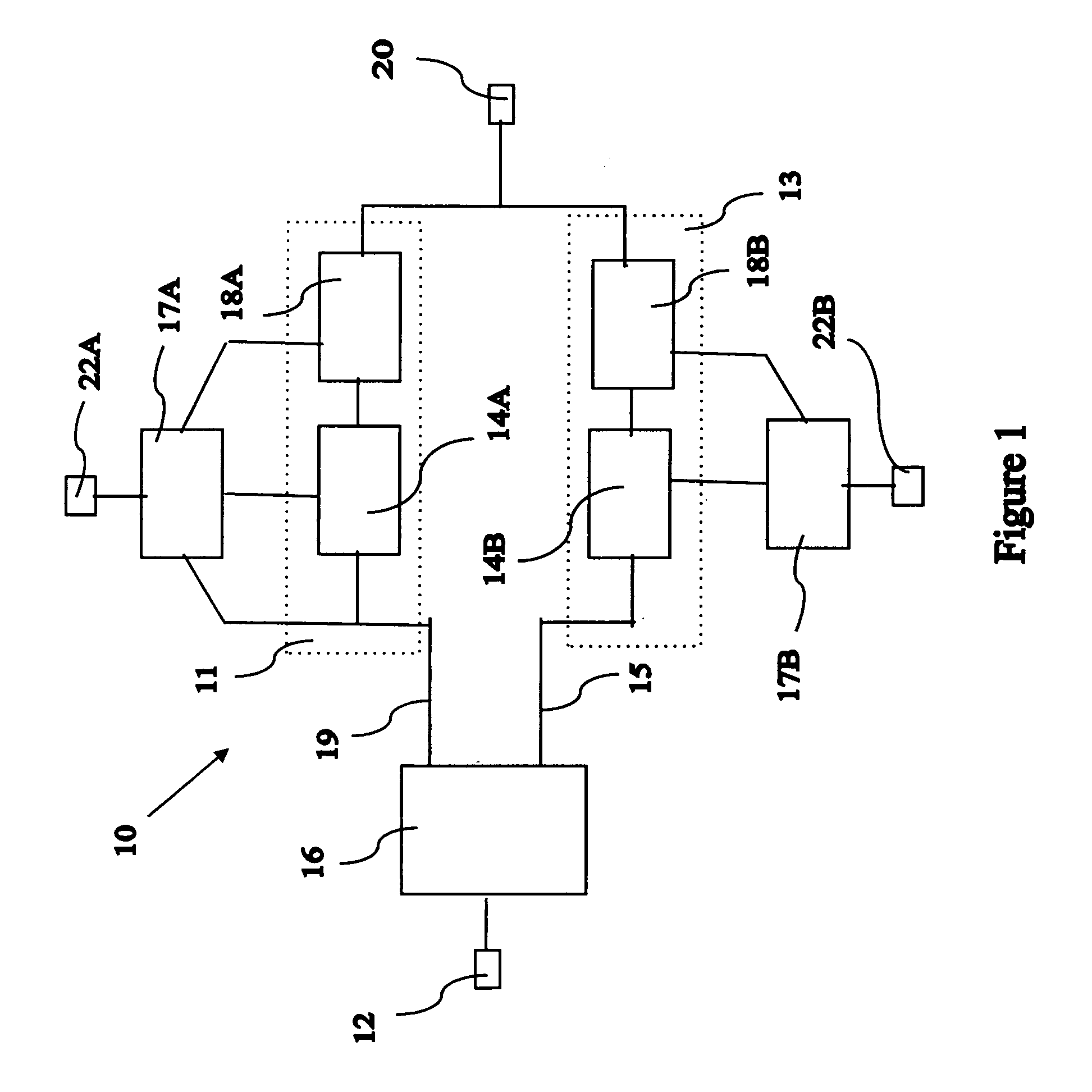

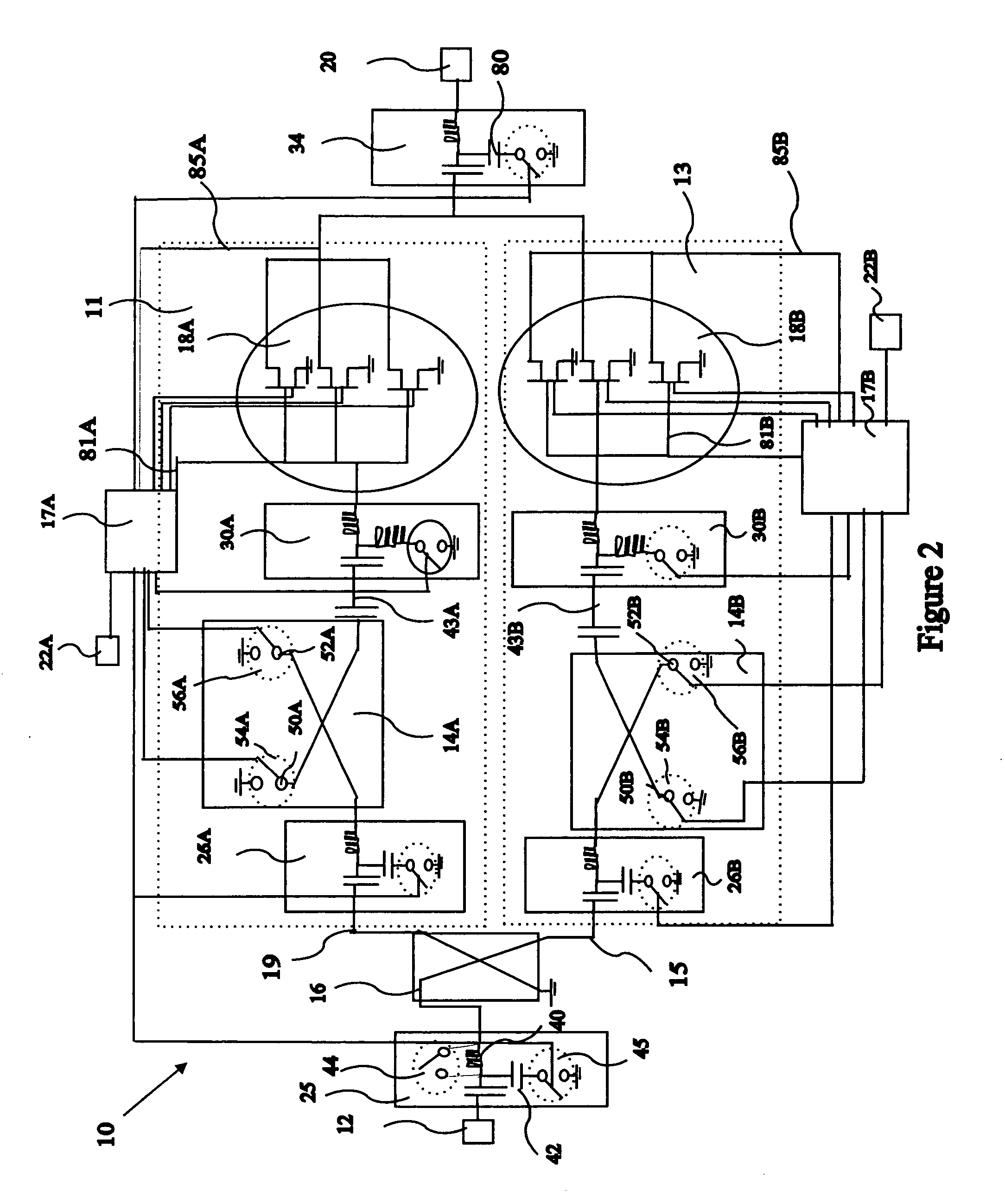

Electronically programmable multimode circuit

An electronically programmable multimode circuit is described. More particularly, the present invention is an electronically programmable multimode circuit that includes a first path and a second path wherein a mode and a signal directional flow direction is controlled through the selective biasing of the first path and the second path. A multimode circuit is produced that contains modes such as a phase shifter mode, an IQ modulation mode, an amplifier mode, a mixer mode, and a multiplier mode.

Owner:NORTHROP GRUMMAN SYST CORP

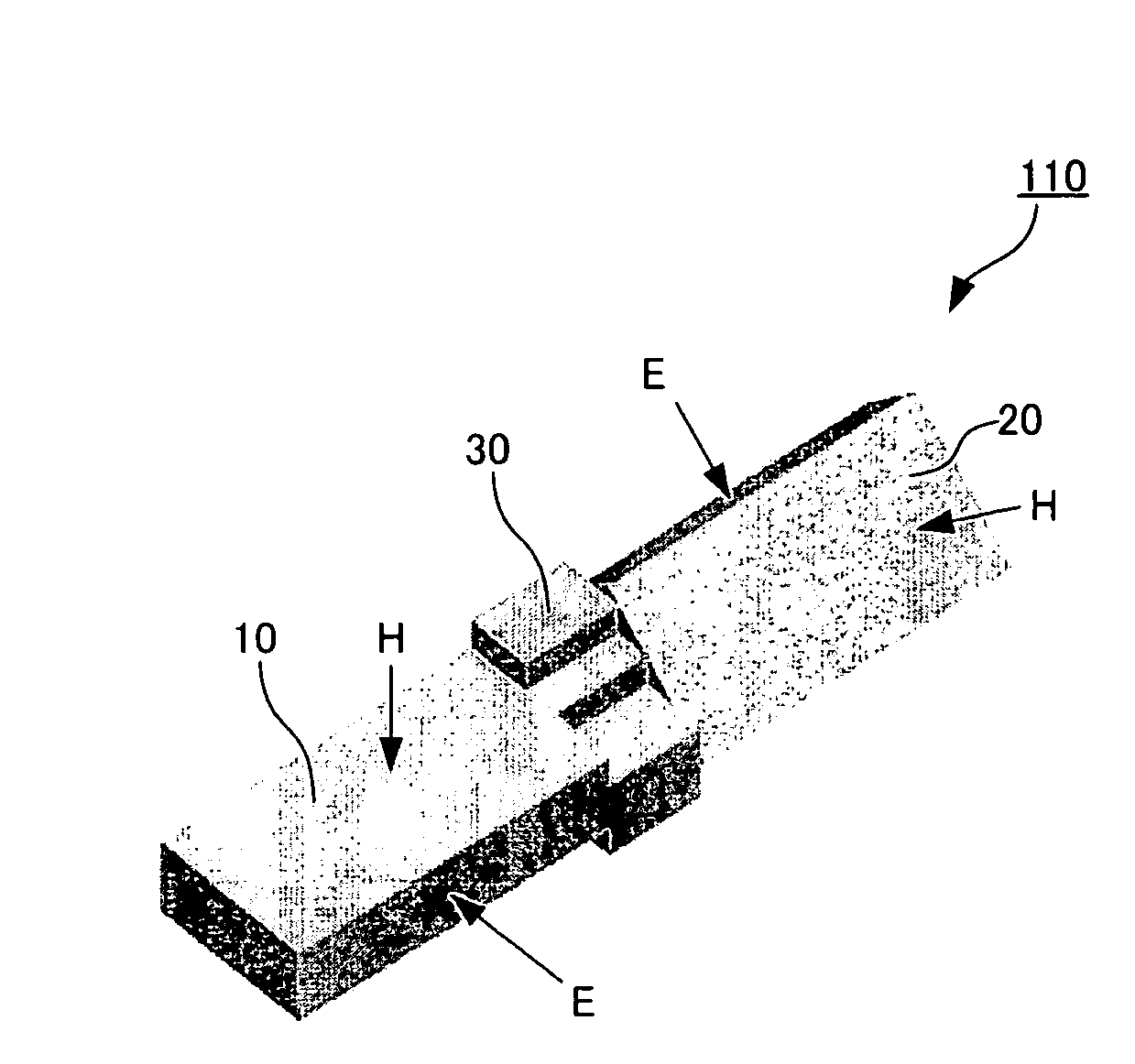

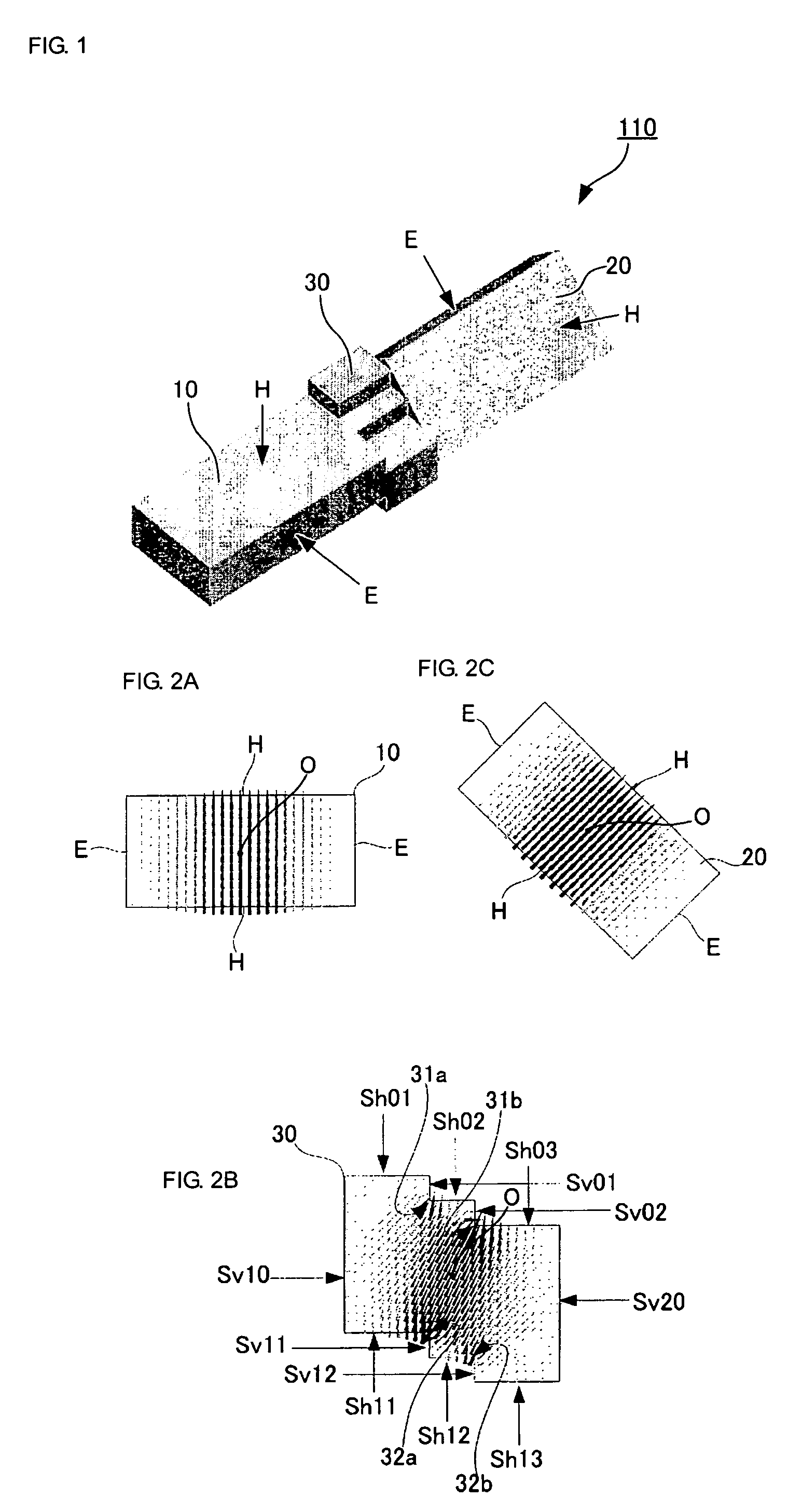

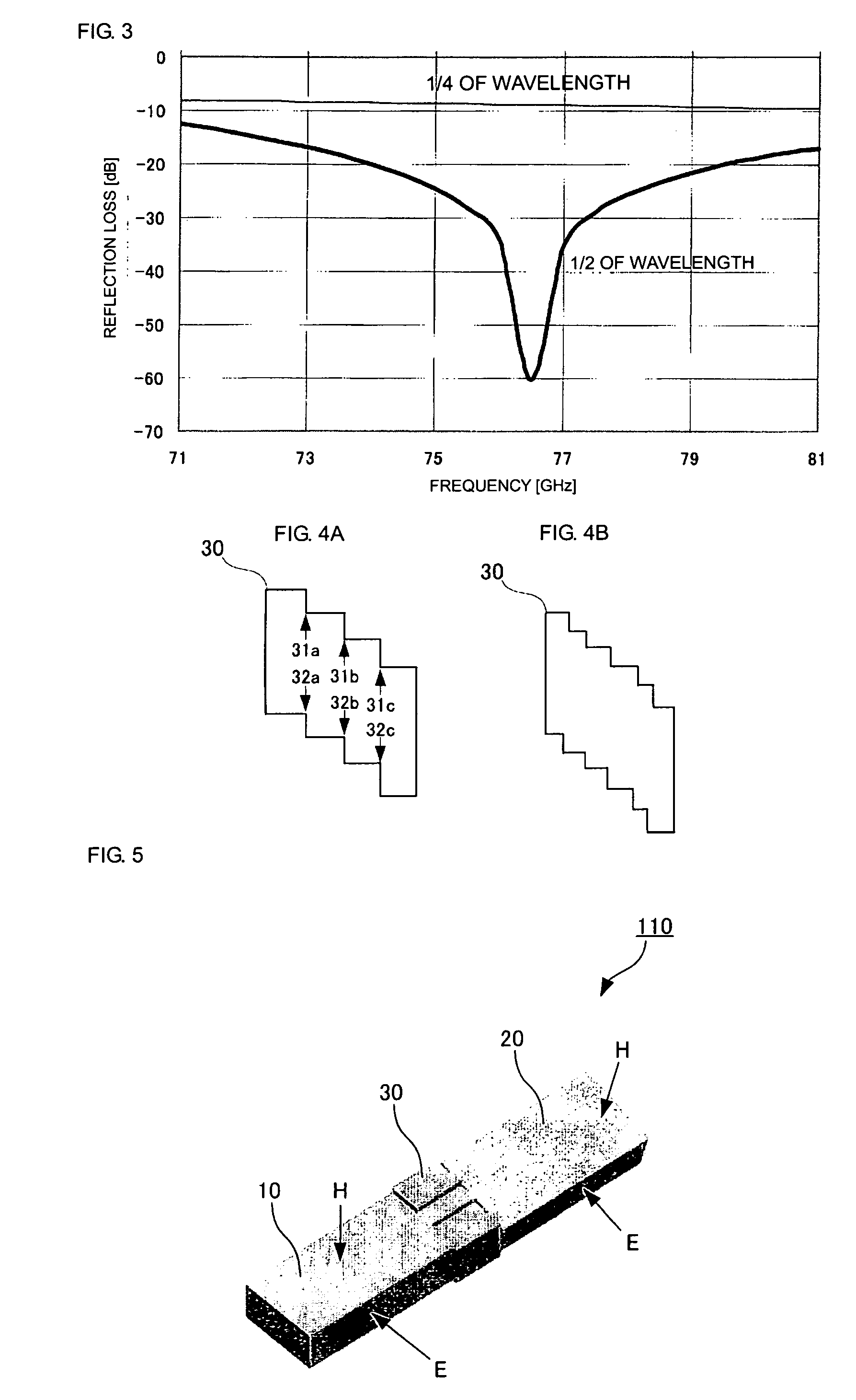

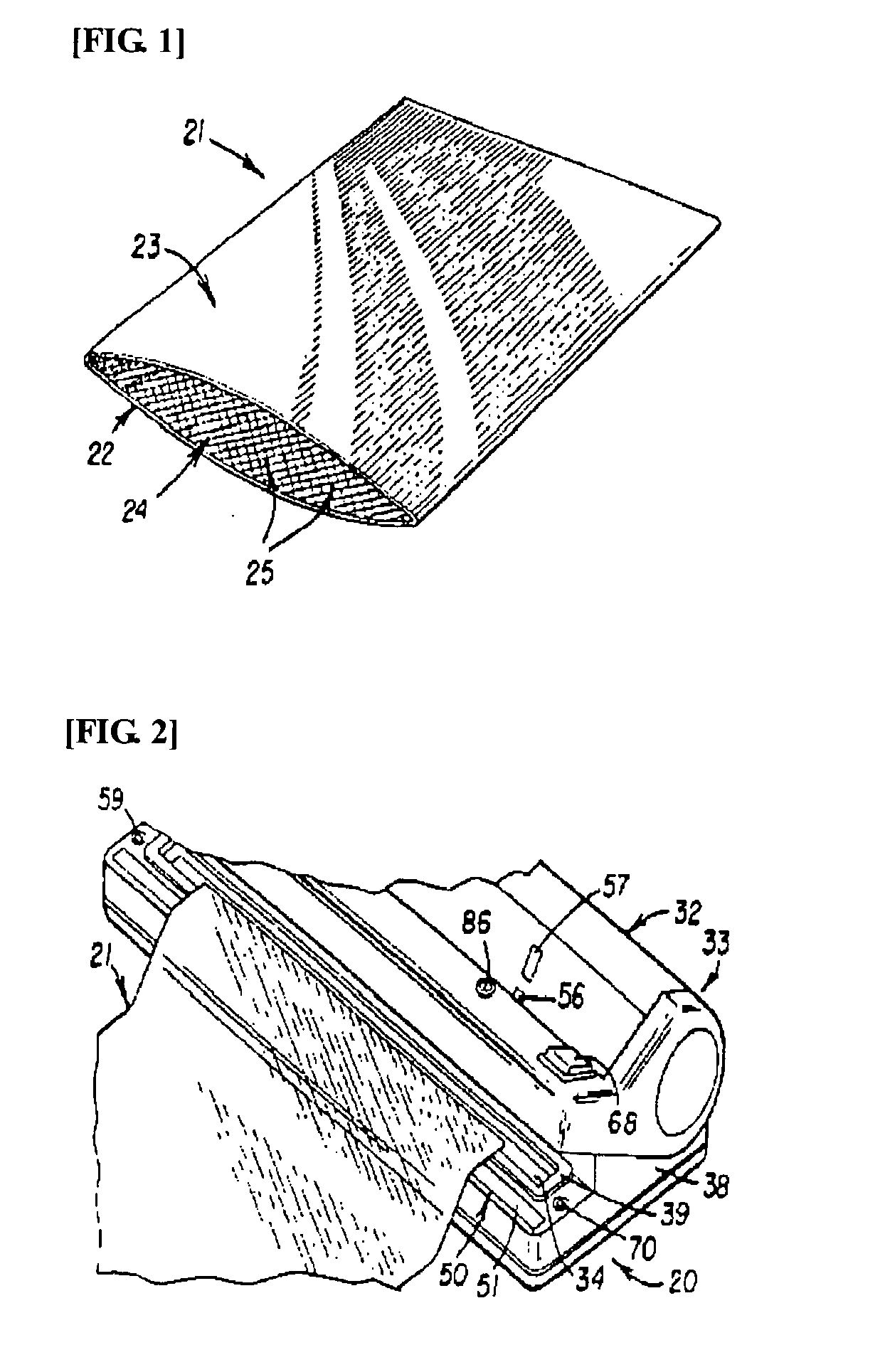

Twisted waveguide and wireless device

InactiveUS7212087B2Manufacturing process is complicatedNarrow rangeCoupling devicesAntennasClassical mechanicsWaveguide

Owner:MURATA MFG CO LTD

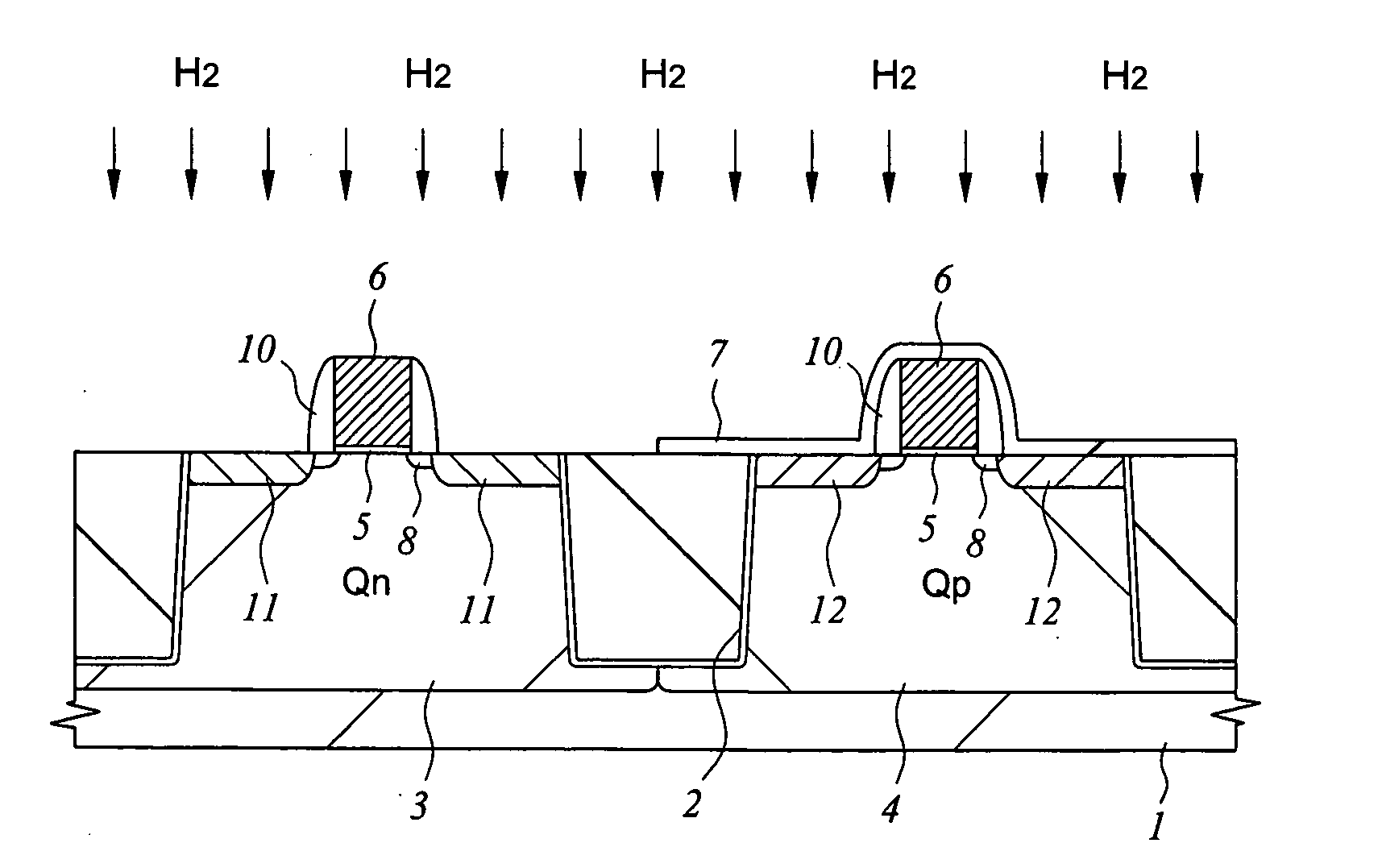

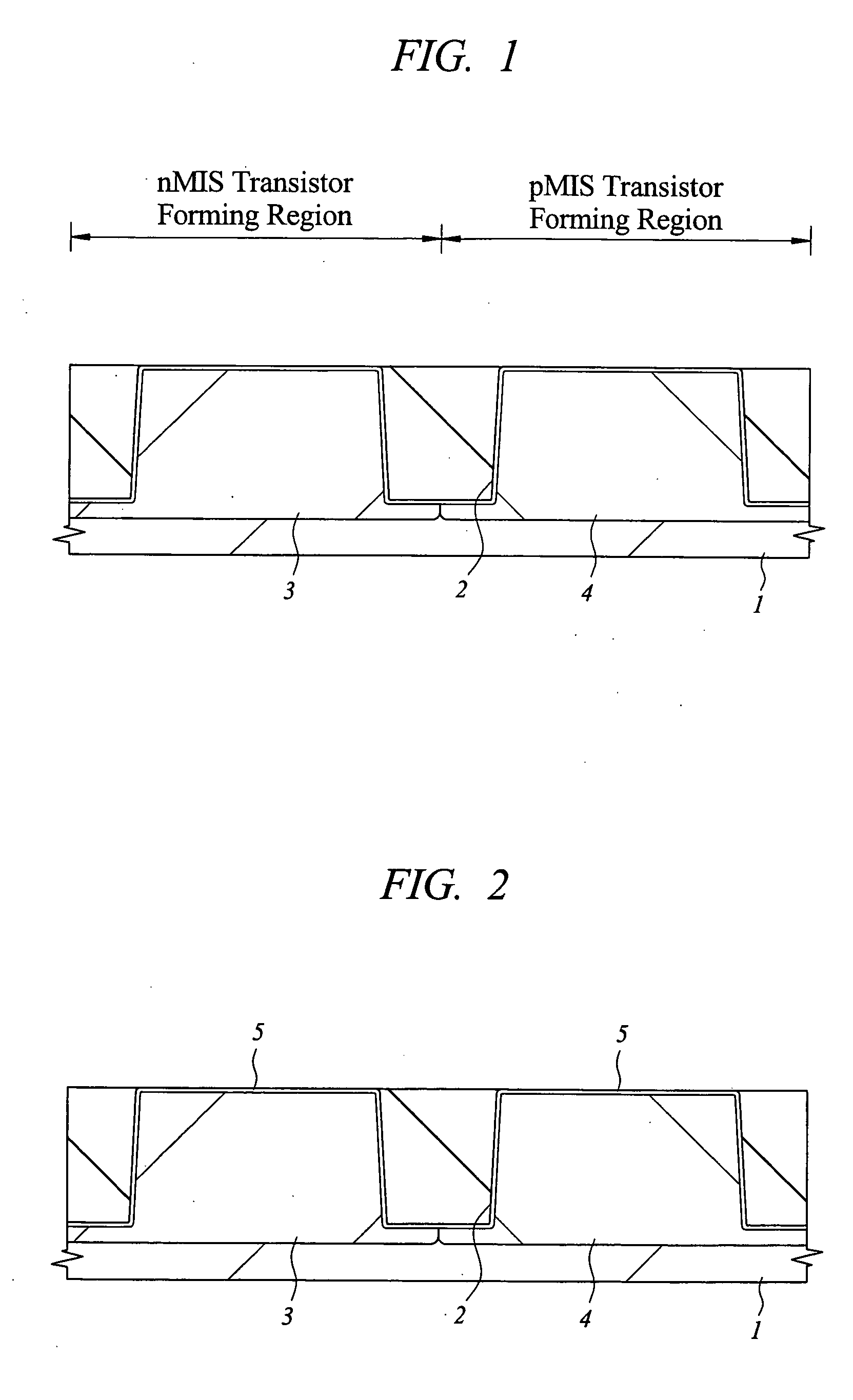

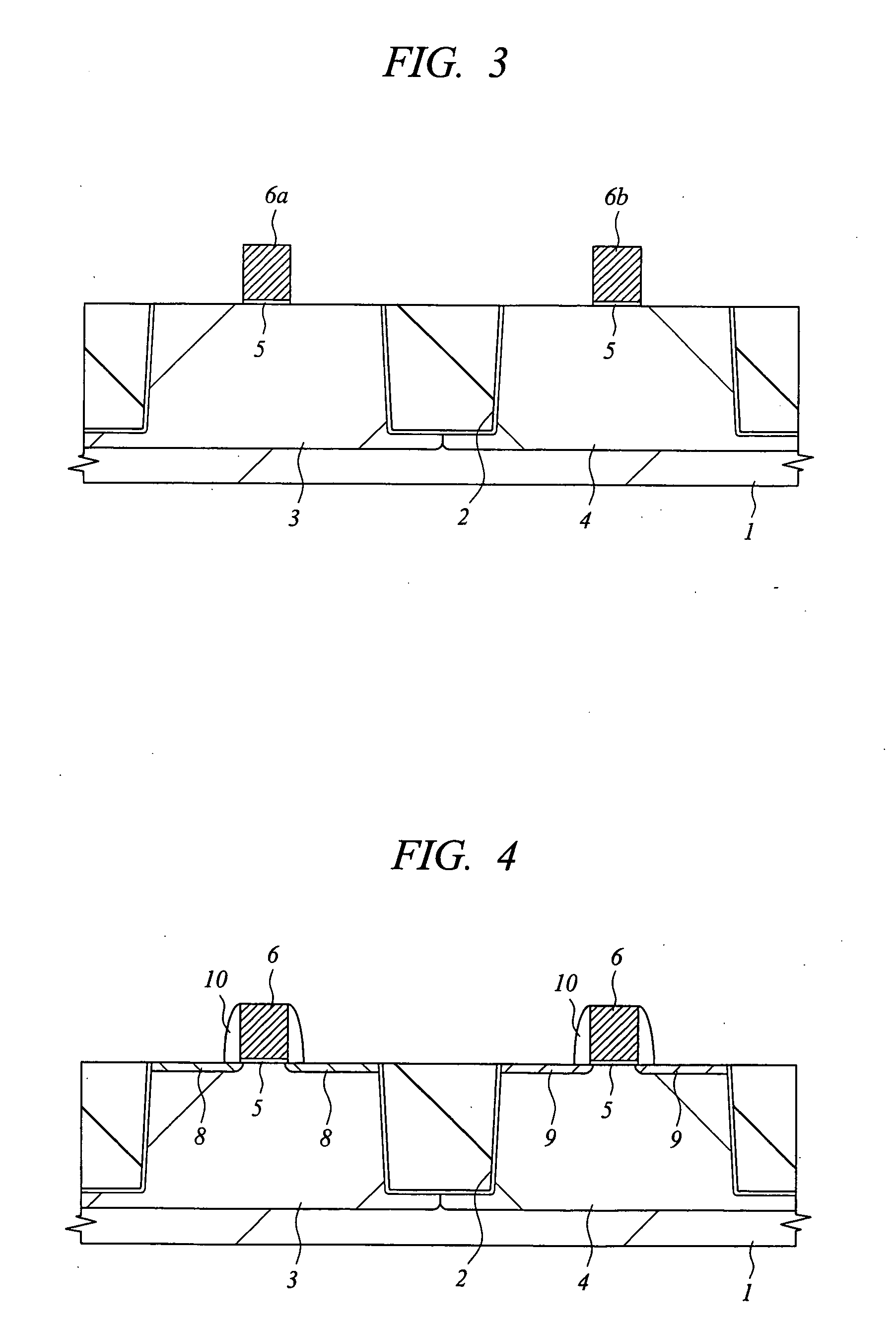

Semiconductor device and manufacturing method thereof

InactiveUS20060091474A1Prevent penetrationManufacturing process is complicatedTransistorSolid-state devicesCMOSMetallic materials

The manufacturing process of a semiconductor device in which a n channel MIS transistor and a p channel MIS transistor each having a gate electrode made of a metal material formed on a gate insulator made of a high dielectric constant material are used to form a CMOS circuit is simplified. After simultaneously forming the gate electrodes of the n channel MIS transistor and the p channel MIS transistor by patterning a platinum film deposited on a gate insulator made of a hafnium oxide film, only the gate insulator on the side of the n channel MIS transistor is selectively reduced by using the catalytic reduction of the platinum film. By doing so, the work function of the gate electrode of the n channel MIS transistor is changed.

Owner:RENESAS TECH CORP

Heat sealable and oriented multi-layer polypropylene-based films for shrink applications

InactiveUS20120052273A1Reduce the amount of processingLess-costly to produceSynthetic resin layered productsLabelsElastomerPlastomer

The present invention relates to a multi-layer oriented shrink film comprising a first and a second skin layer comprising a propylene-based polymer having a melting point greater than 130 C and at least one core layer comprising a propylene-based plastomer or elastomer. The films are preferably primarily oriented in either the machine or the cross direction. These films are ideally suited for use as a shrink label which can be applied either as a CD shrink sleeve or applied using a continuous roll process. The films ideally have an overall density of less than 1.0 g / cm3, to facilitate recycling efforts.

Owner:DOW GLOBAL TECH LLC

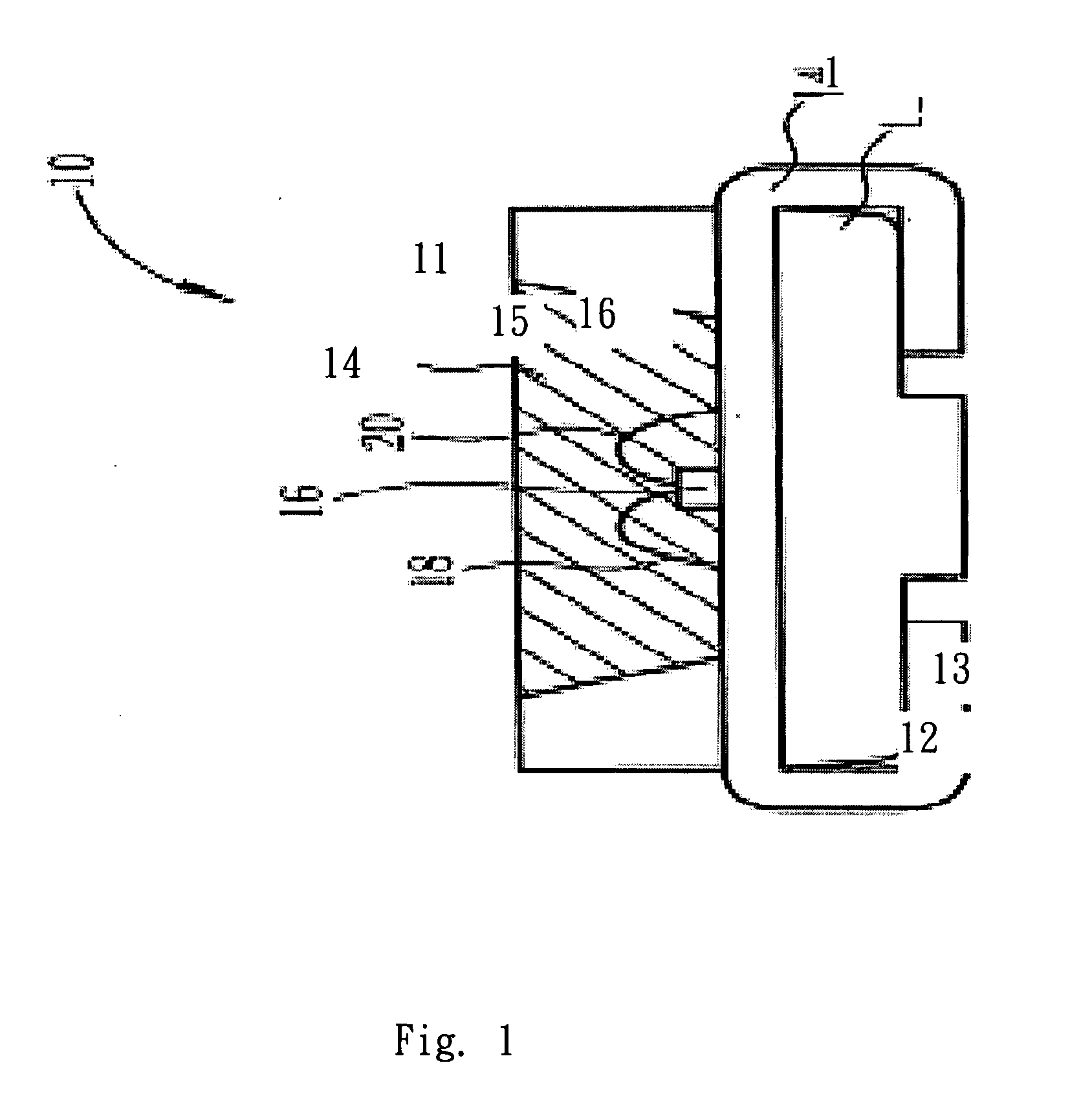

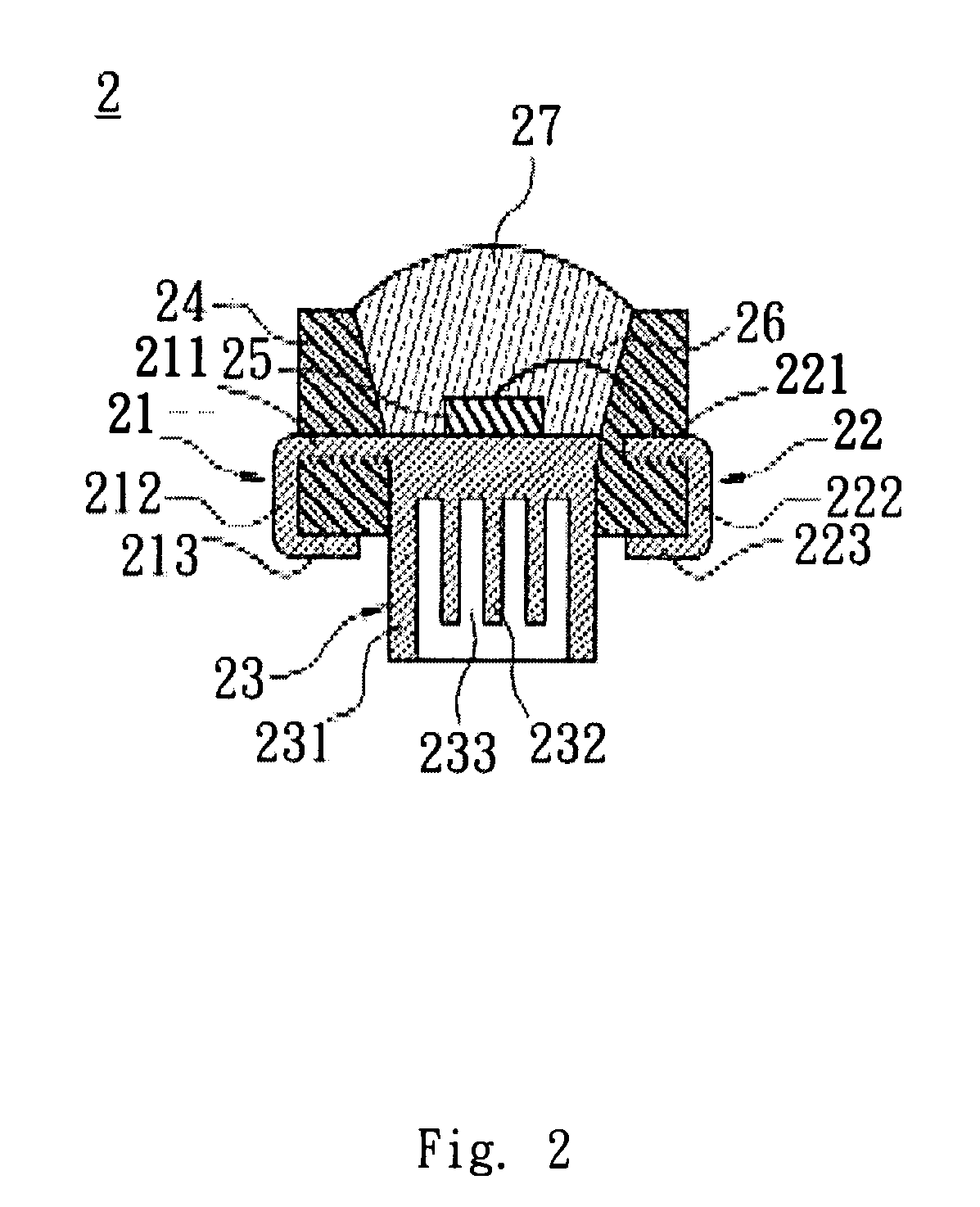

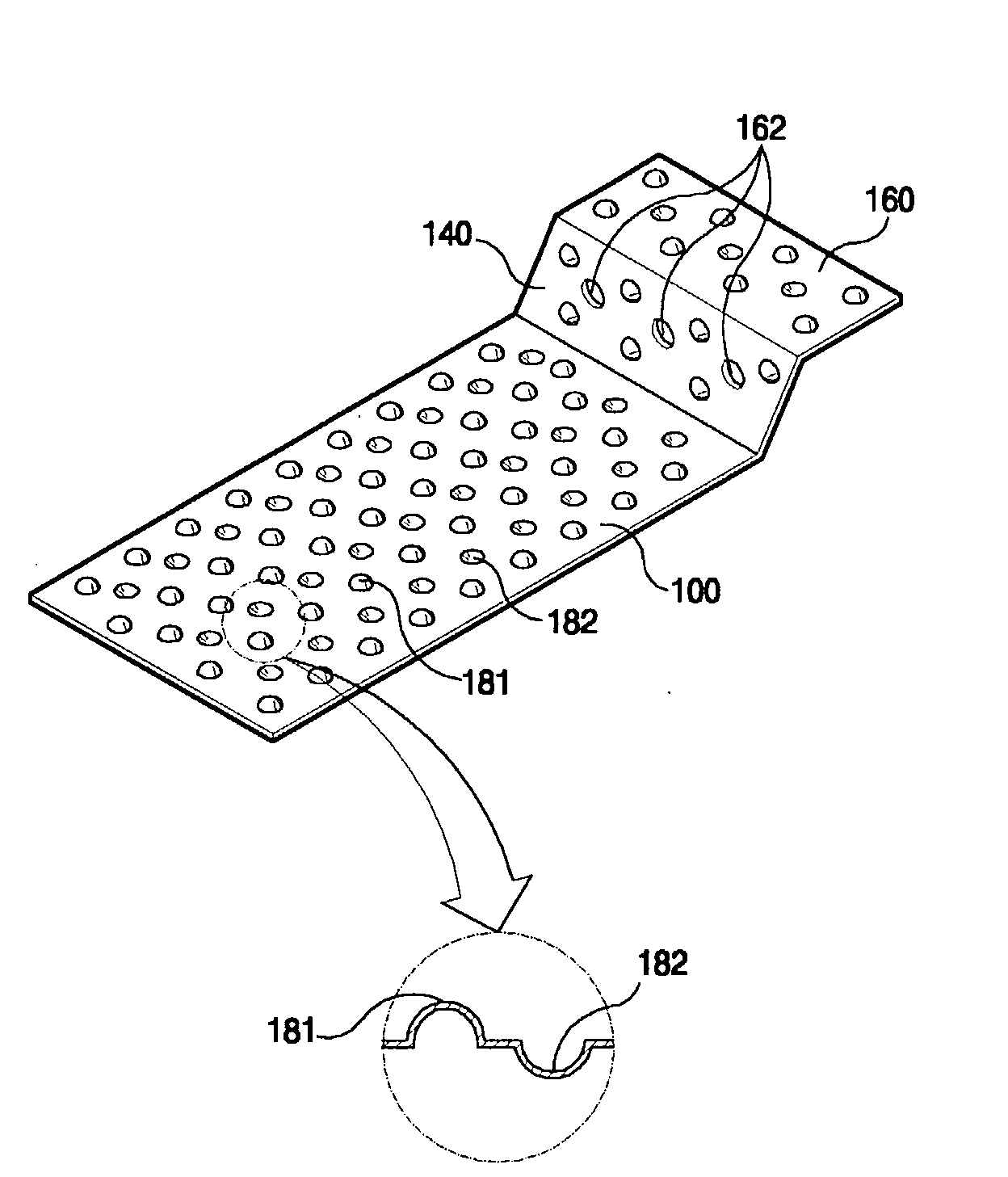

Light emitting diode and wafer level package method, wafer level bonding method thereof, and circuit structure for wafer level package

ActiveUS20080099771A1Stable supportManufacturing process is complicatedSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringLight-emitting diode

This invention discloses a light emitting diode, a wafer level package method, a wafer level bonding method, and a circuit structure for a wafer level package. The light emitting diode includes a package carrier, a conducting material, at least one light emitting diode structure and a package material. The package carrier has at least one package unit and two through holes on the package carrier and corresponding to the package unit. The conducting material is disposed in the through holes and formed at the bottom of the package unit. The light emitting diode structure is formed on a substrate. The substrate having a light emitting diode structure is flipped over in the package unit, and the electrodes of the light emitting diode structure are bonded with the conducting material. After the substrate is removed, a package material is stuffed in the package unit or on the light emitting diode structure.

Owner:EPILEDS TECH +1

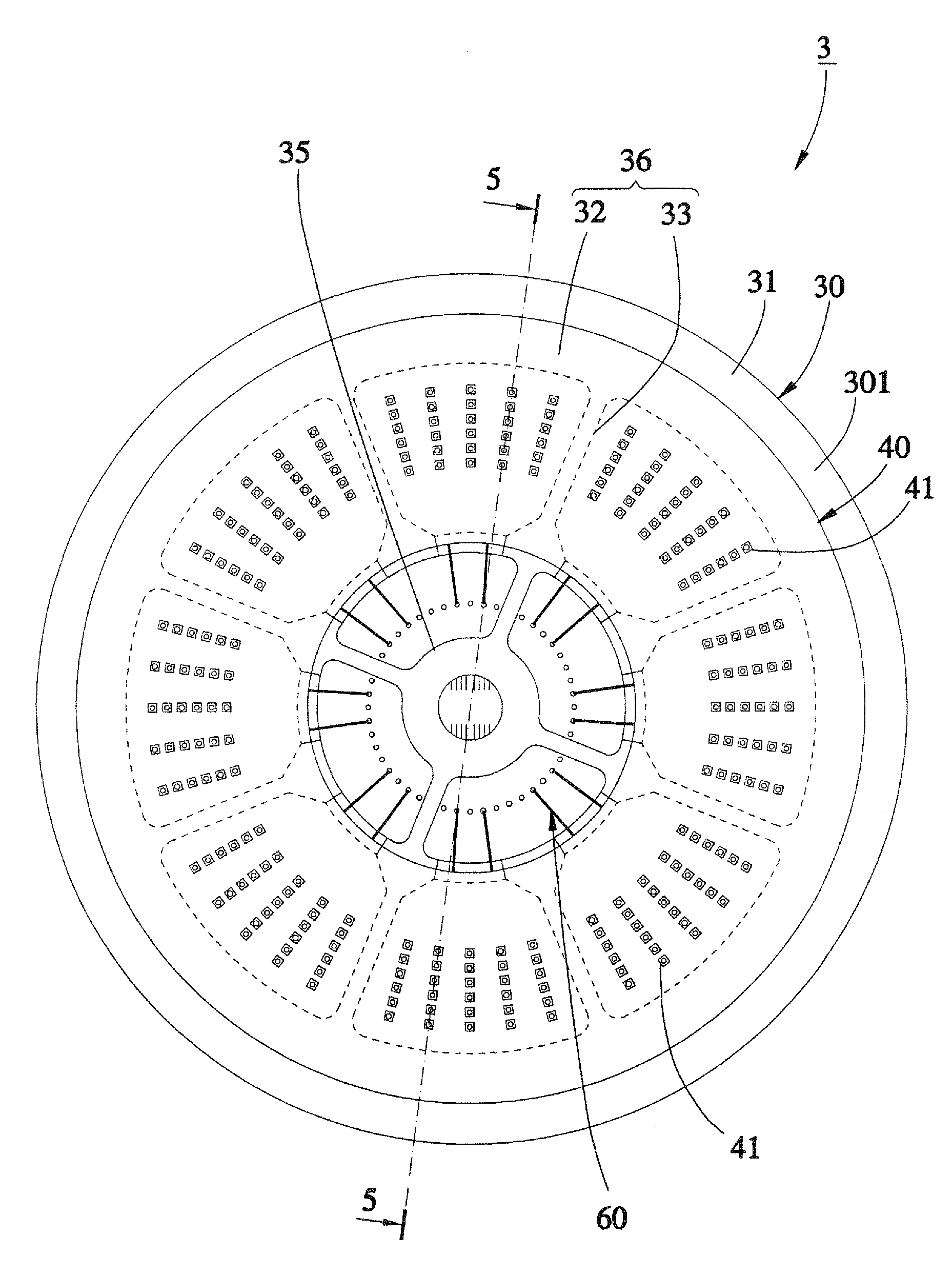

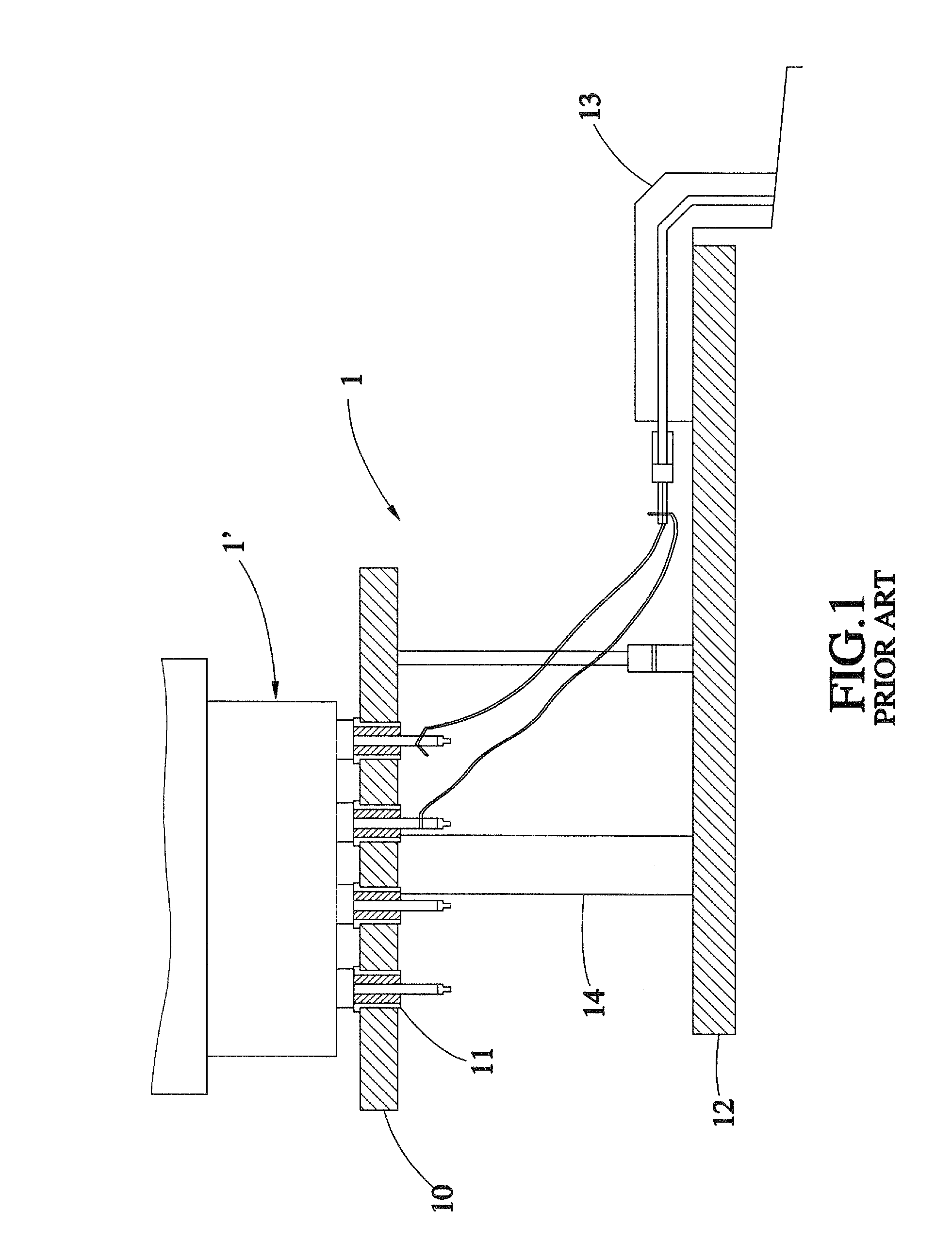

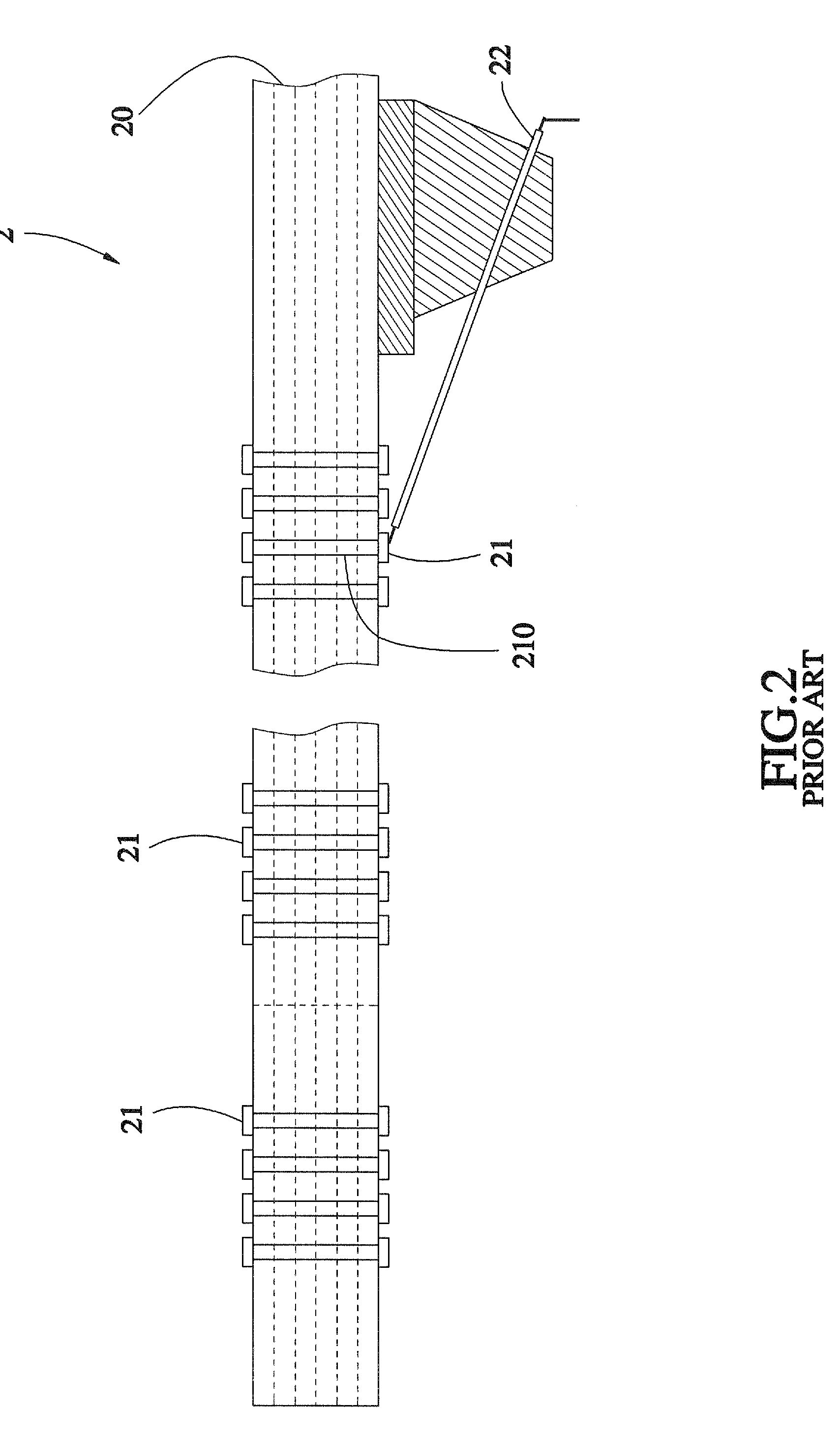

Probing device

InactiveUS20090009198A1Improve structural strengthQuality improvementSemiconductor/solid-state device testing/measurementElectrical measurement instrument detailsTester deviceEngineering

A probing device includes a rack that has an outer support member supporting a circuit layer and a center support member supporting a probe assembly. When the tester touching down the circuit layer of the probing device from the top side, the outer support member of the rack bears this touchdown stress. When the probes of the probe holder touching down the electronic components of an IC wafer under test, the center support member of the rack bears the reaction force from the IC wafer.

Owner:MICROELECTRONICS TECH INC

Micro piezoresistive pressure sensor and manufacturing method thereof

ActiveUS20100251826A1Manufacturing process is complicatedOvercome difficultiesPiezoelectric/electrostrictive device manufacture/assemblyFluid pressure measurement using ohmic-resistance variationPiezoresistive pressure sensorsSemiconductor

A micro semiconductor-type pressure sensor and a manufacturing method thereof are provided. The micro semi-conductor-type pressure sensor is implemented by etching a cavity-formation region of a substrate to form a plurality of trenches, oxidizing the plurality of trenches through a thermal oxidation process to form a cavity-formation oxide layer, forming a membrane-formation material layer on upper portions of the cavity-formation oxide layer and the substrate, forming a plurality of etching holes in the membrane-formation material layer, removing the cavity-formation oxide layer through the plurality of etching holes to form a cavity buried in the substrate, forming a membrane reinforcing layer on an upper portion of the membrane-formation material layer to form a membrane for closing the cavity, and forming sensitive films made of a piezoresisive material on an upper portion of the membrane.

Owner:ELECTRONICS & TELECOMM RES INST

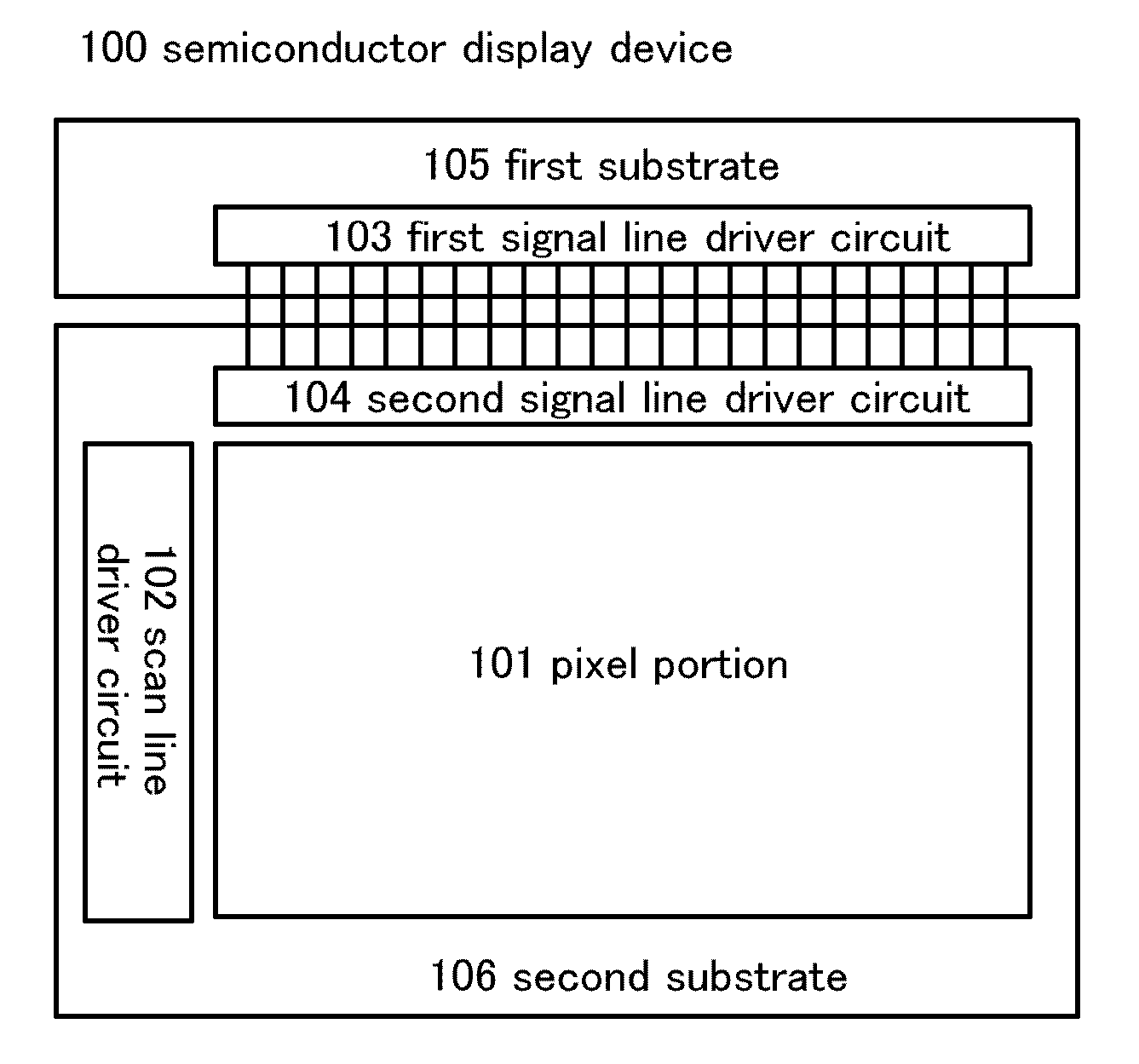

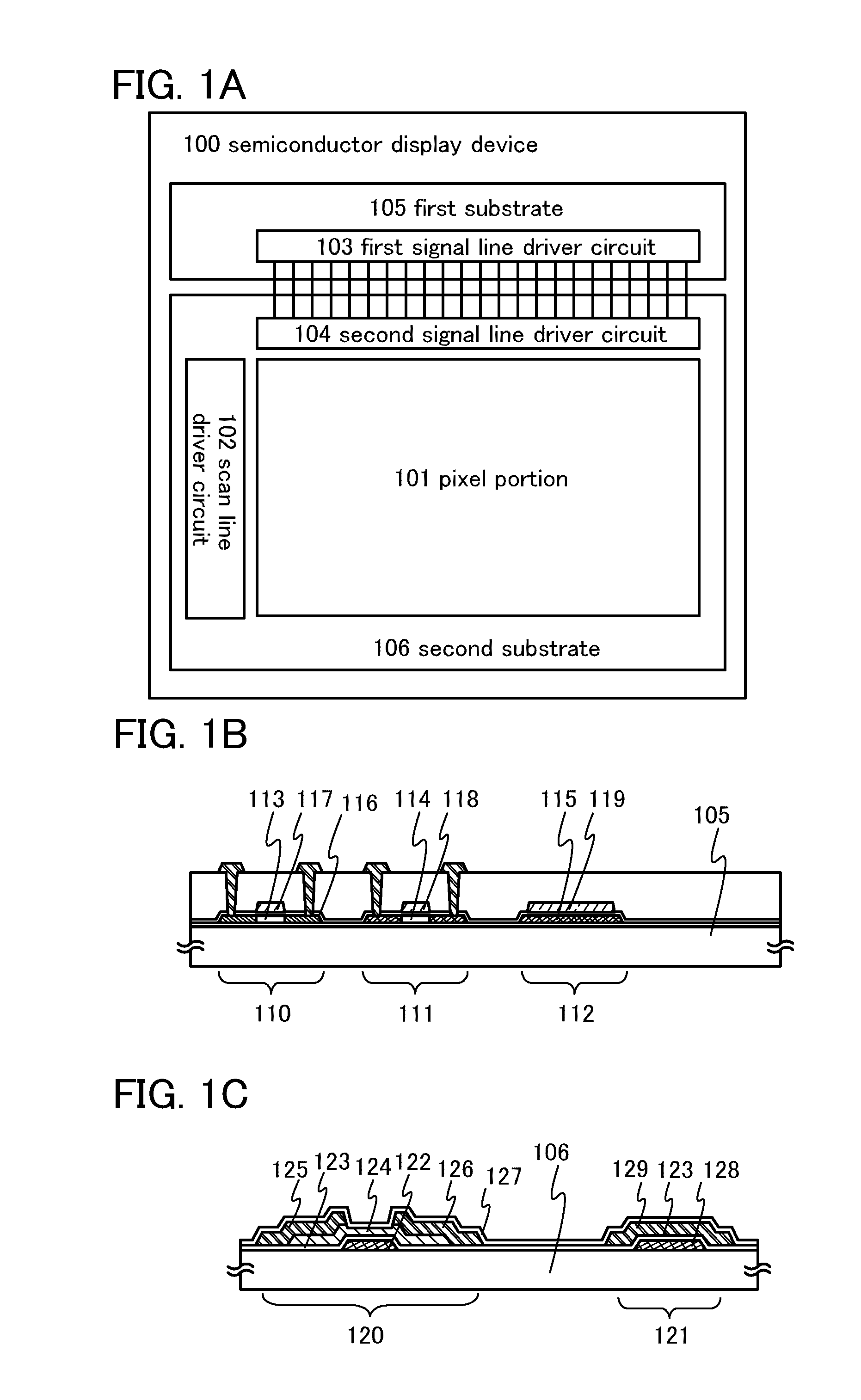

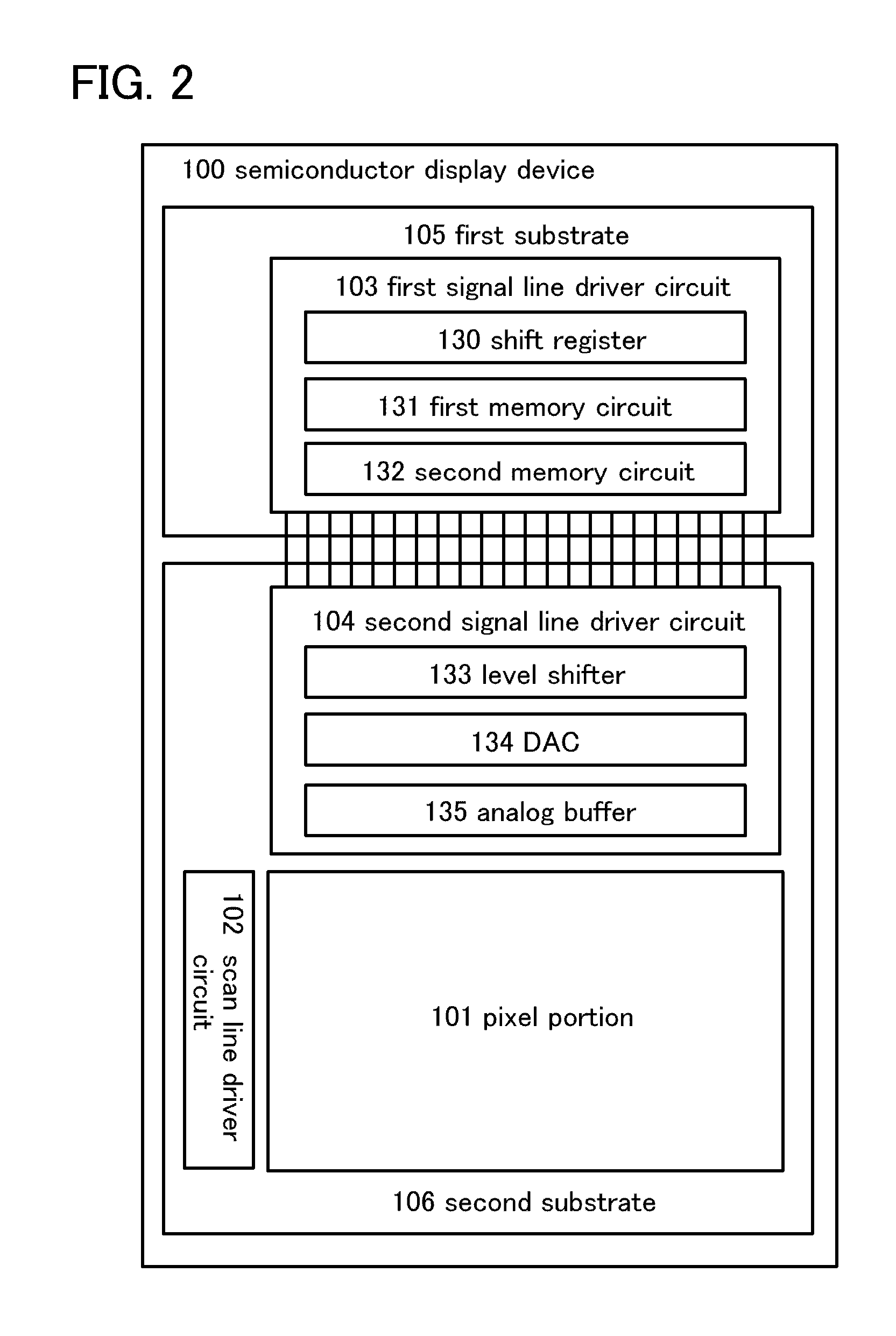

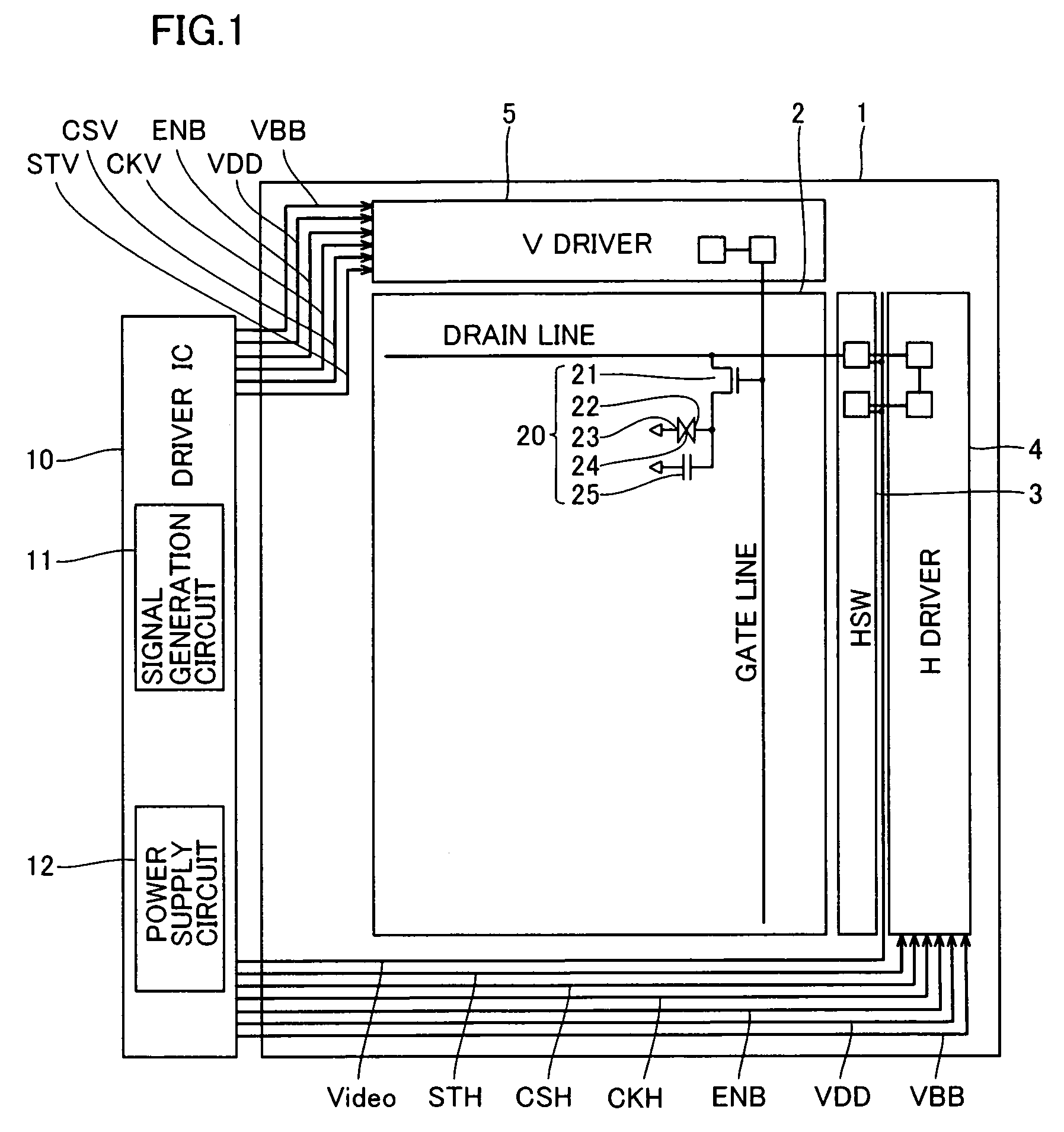

Semiconductor display device

ActiveUS20110242070A1Run at high speedImprove pressure resistanceTelevision system detailsTelevision system scanning detailsDriver circuitElectrical conductor

A semiconductor display device comprising a pixel portion and a signal line driver circuit comprising a first circuit, a second circuit configured to control timing of the sampled serial video signals by the first circuit, and a third circuit configured to perform signal processing on the parallel video signals, wherein the second circuit comprises a first semiconductor element formed over a first substrate, the first semiconductor element including a first semiconductor layer, wherein the third circuit comprises a second semiconductor element formed over a second substrate, the second semiconductor element including a second semiconductor layer, wherein the pixel portion comprises a third semiconductor element formed over the second substrate, the third semiconductor element including a third semiconductor layer, wherein the first semiconductor layer comprises silicon or germanium, and wherein each the second semiconductor layer and the third semiconductor layer has a wider bandgap than the first semiconductor layer.

Owner:SEMICON ENERGY LAB CO LTD

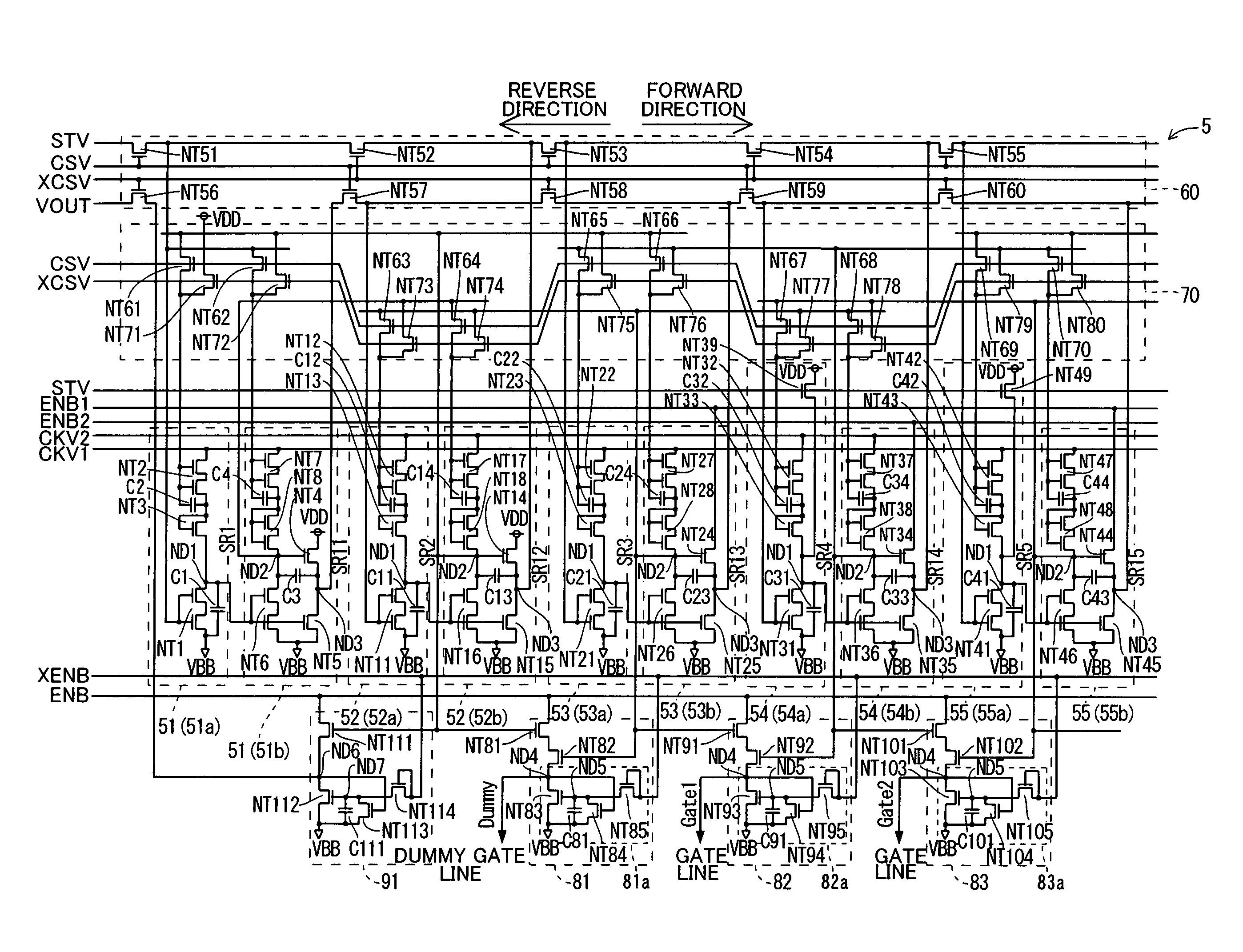

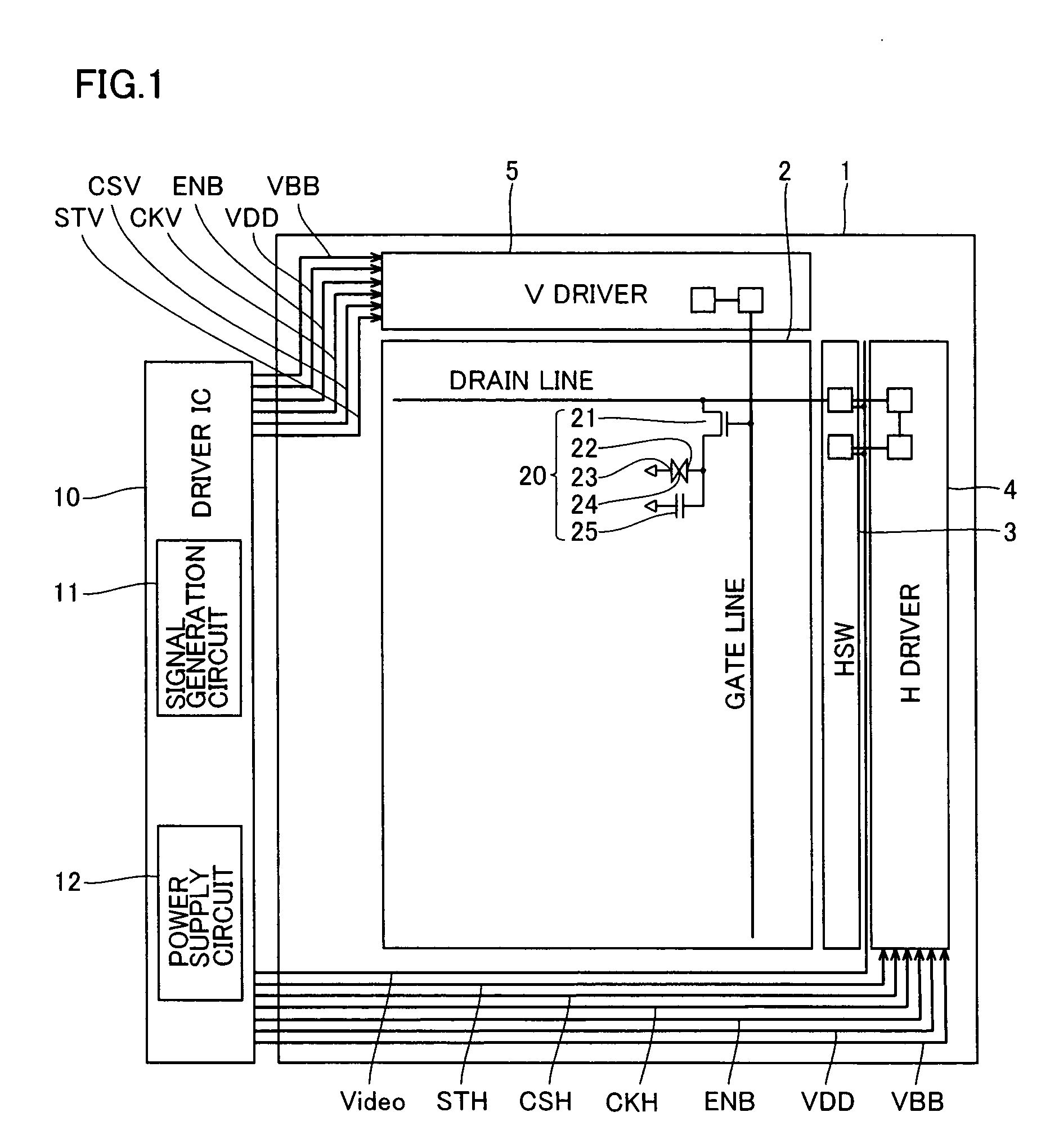

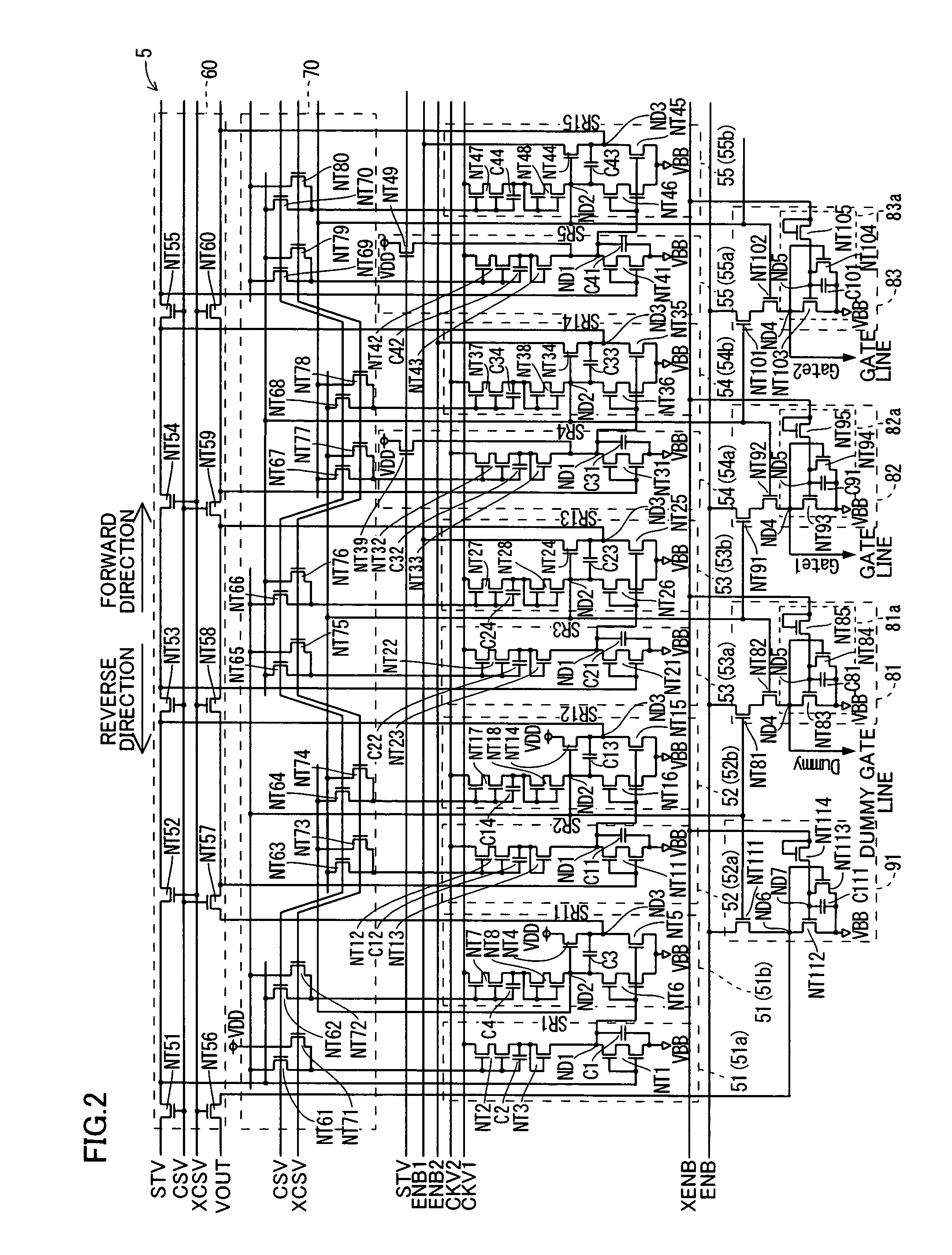

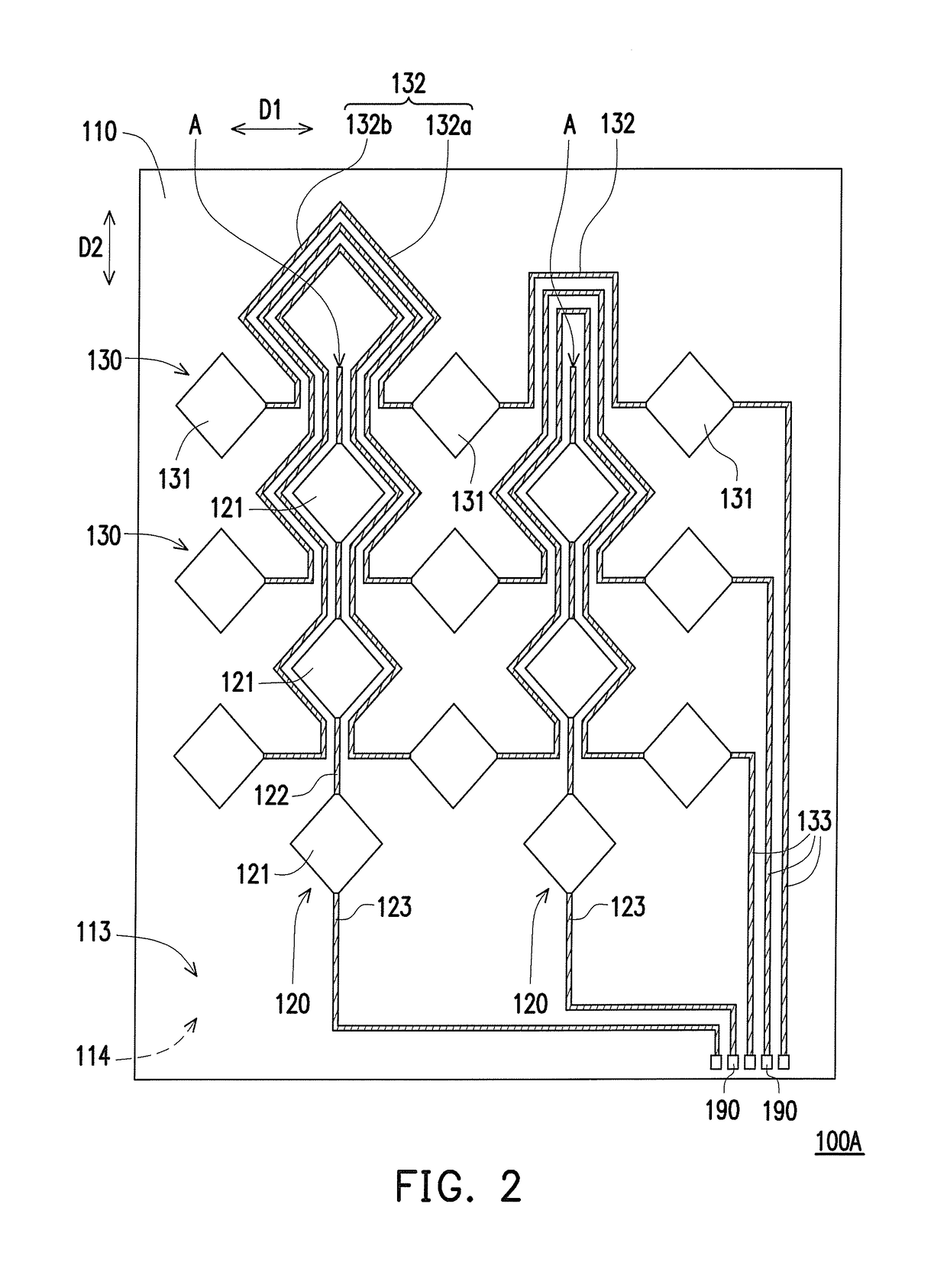

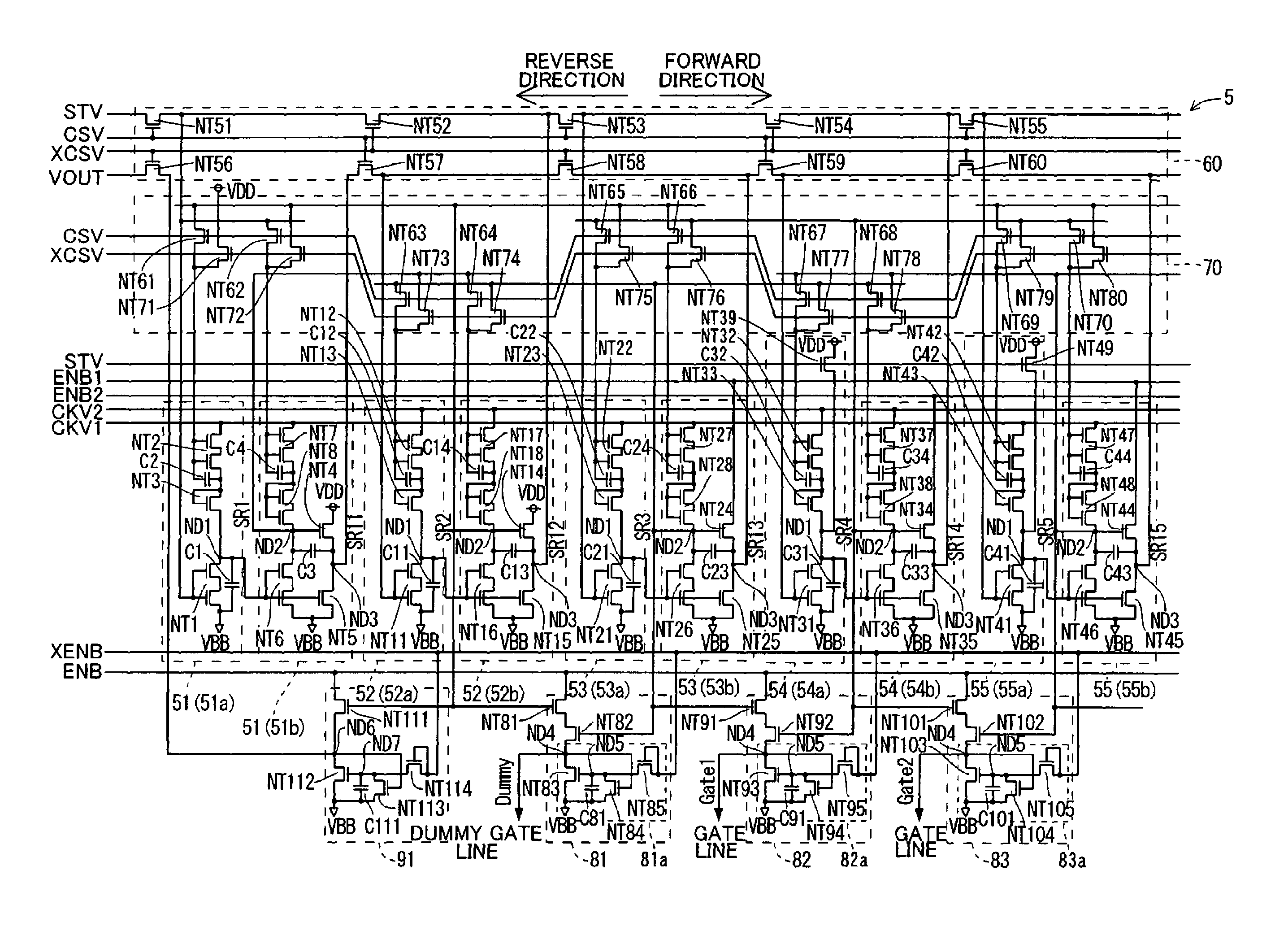

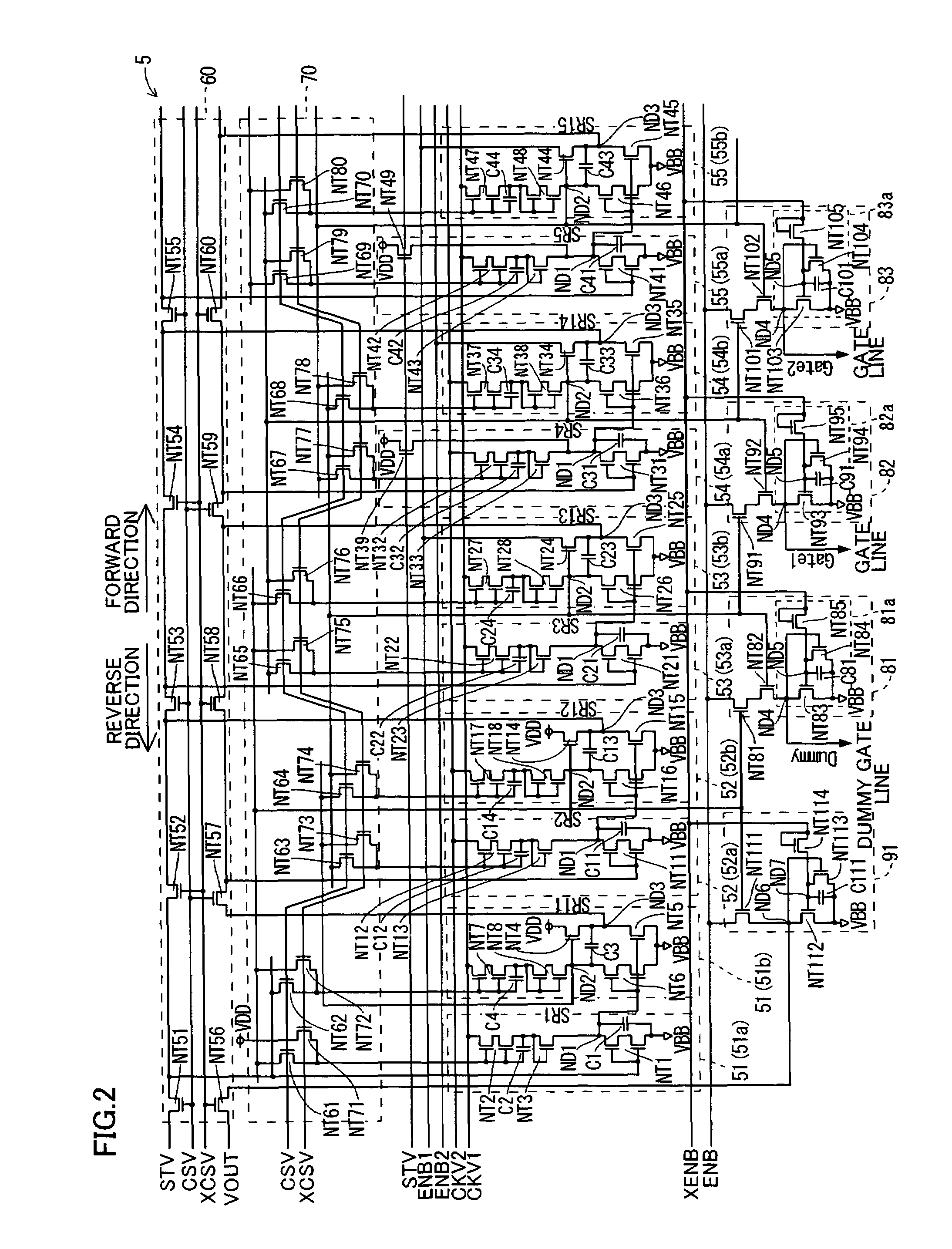

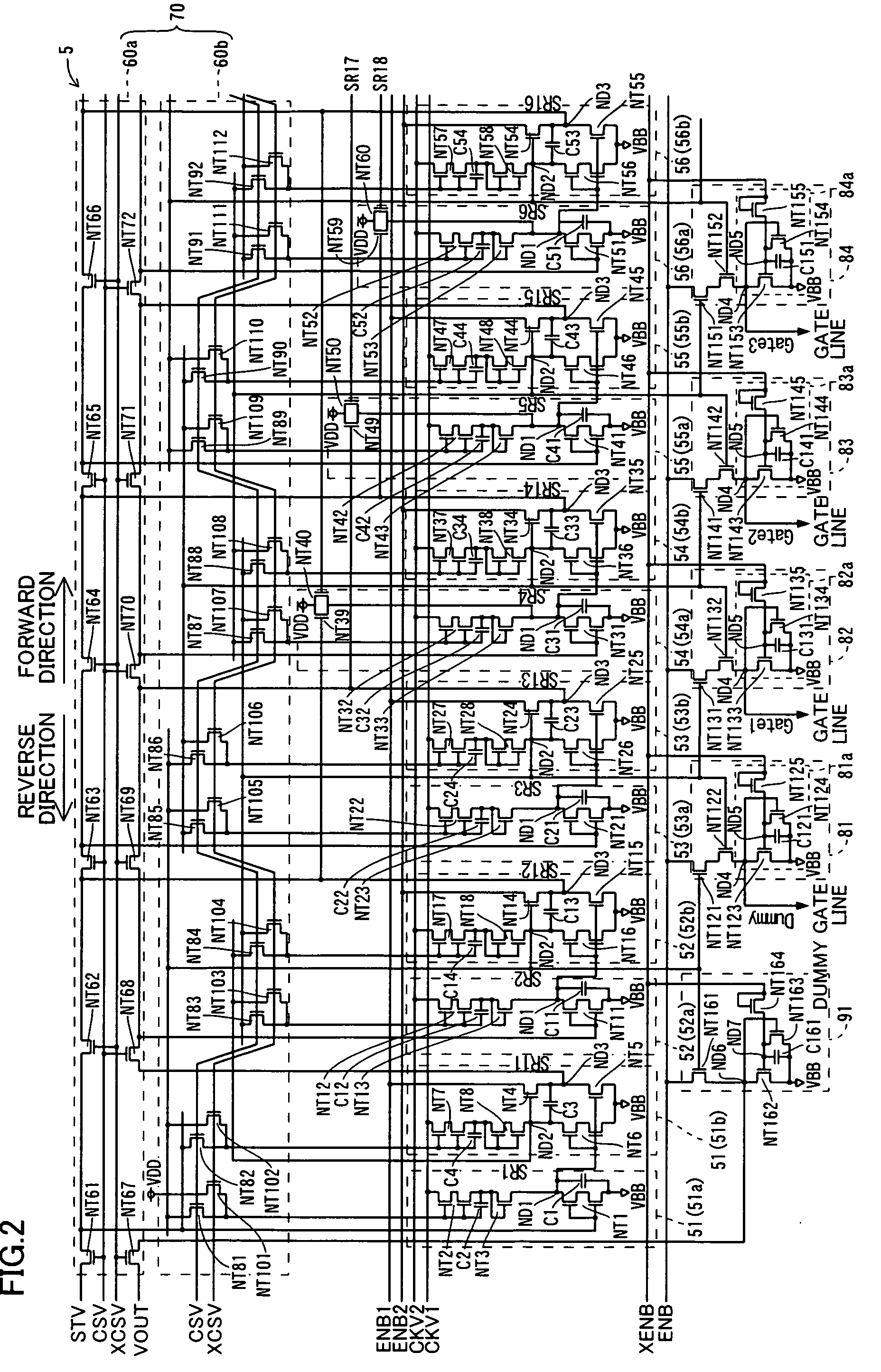

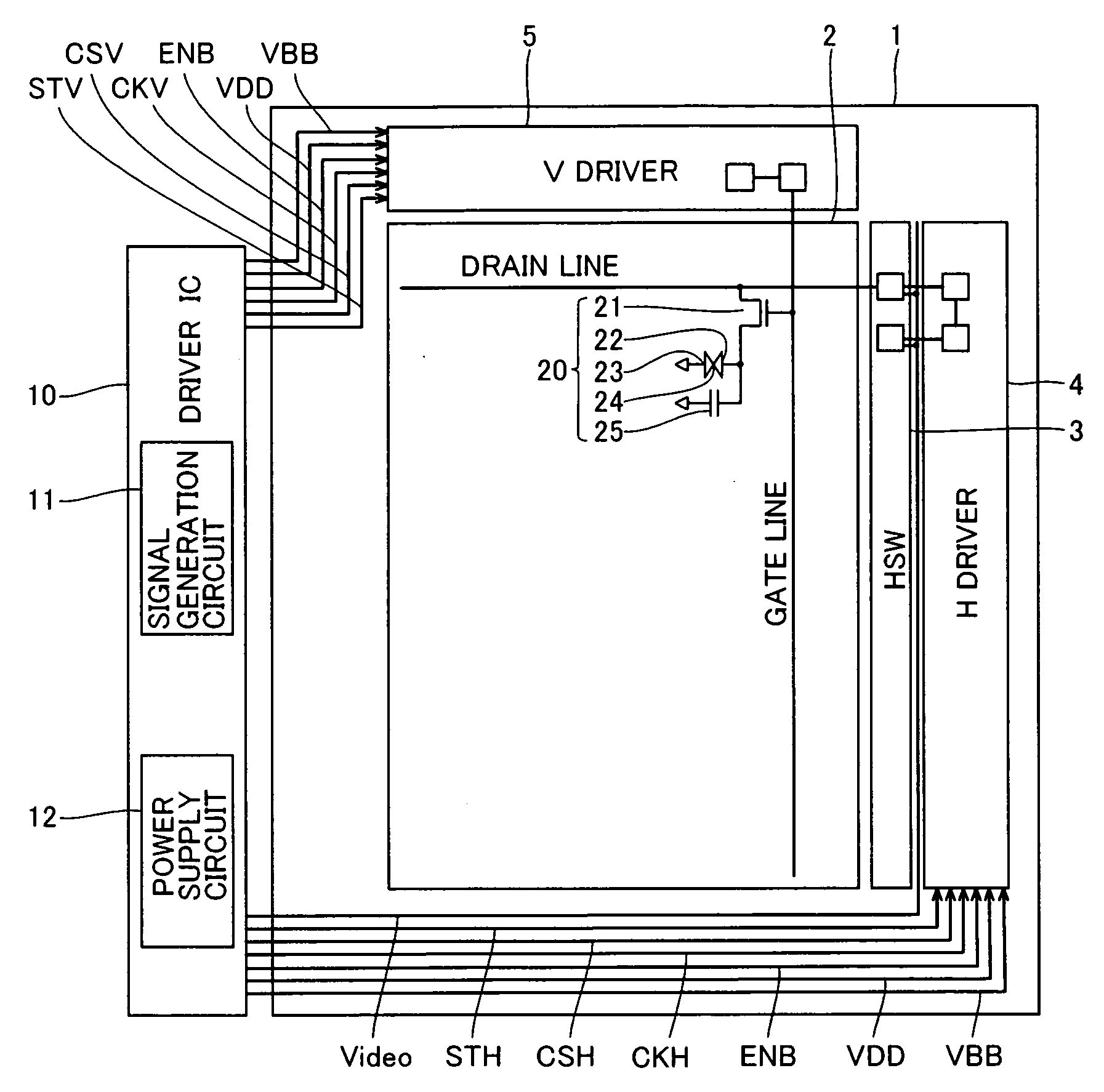

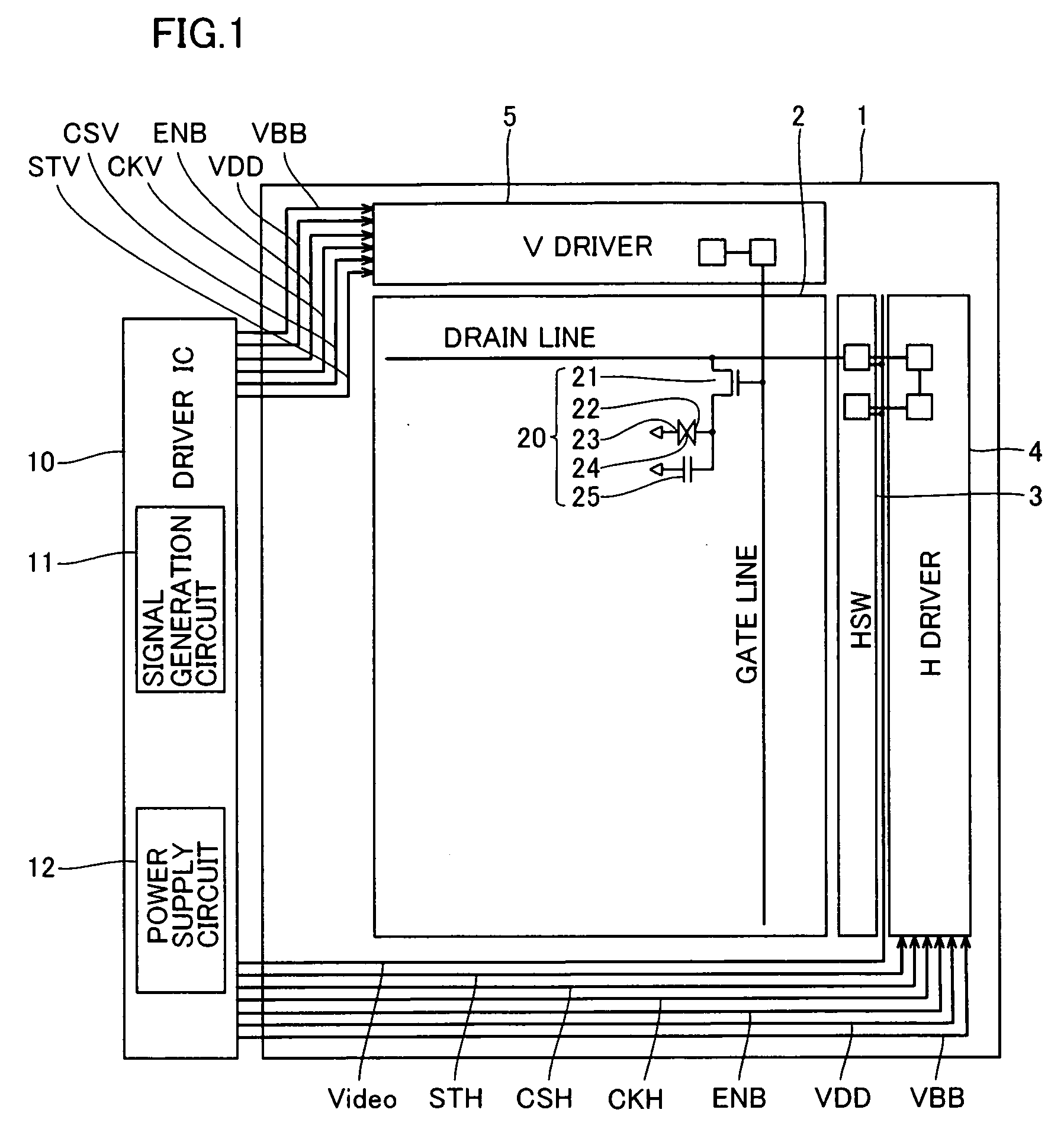

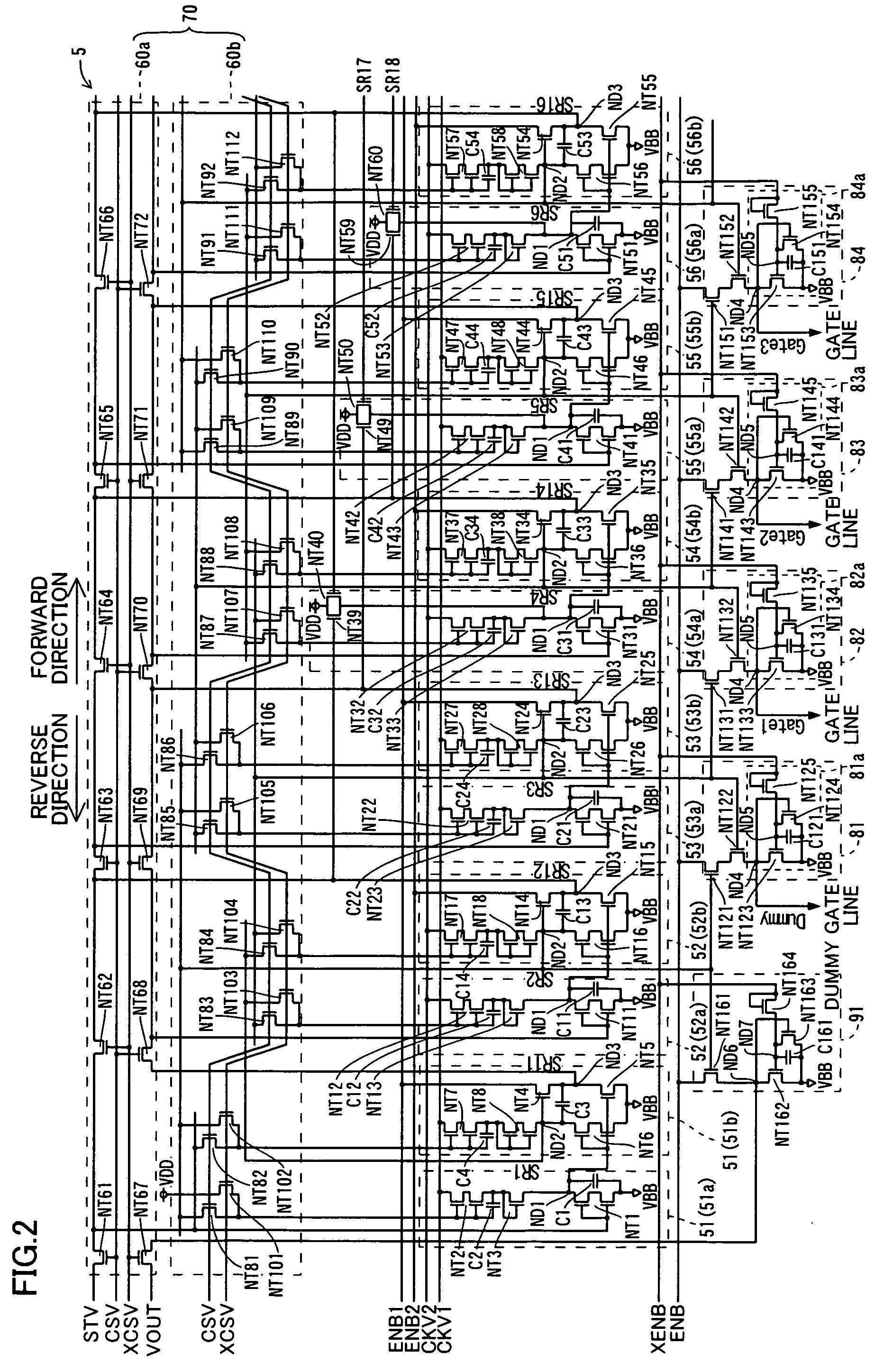

Display

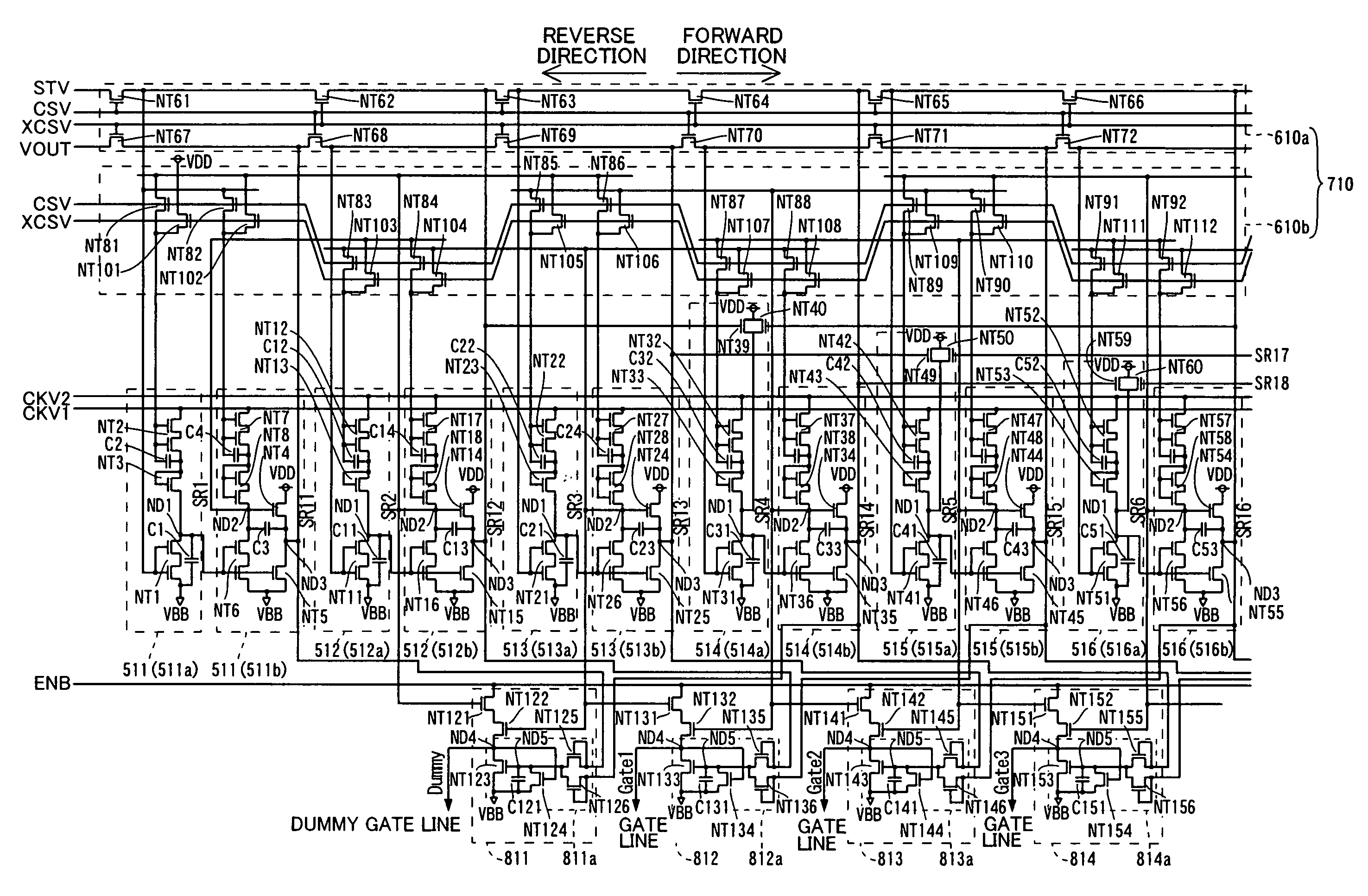

ActiveUS20060221043A1Reliably inhibit logic composition circuit portionReduce implantationTelevision system detailsCathode-ray tube indicatorsShift registerDisplay device

A display capable of inhibiting a logic composition circuit from outputting a signal to a gate line or a drain line at unintentional timing is obtained. This display comprises a shift register circuit including a logic composition circuit portion constituted of a plurality of first conductive type transistors turned on with a first voltage supply source for receiving a first shift signal and a second shift signal and outputting a shift output signal by logically compositing the first shift signal and the second shift signal with each other. At least either a first shift register circuit portion or a second shift register circuit portion includes a reset transistor for resetting the voltage supply source of a node outputting the first shift signal or the second shift signal to a second voltage supply source not turning on the transistors of the logic composition circuit portion in response to a prescribed drive signal.

Owner:JAPAN DISPLAY WEST

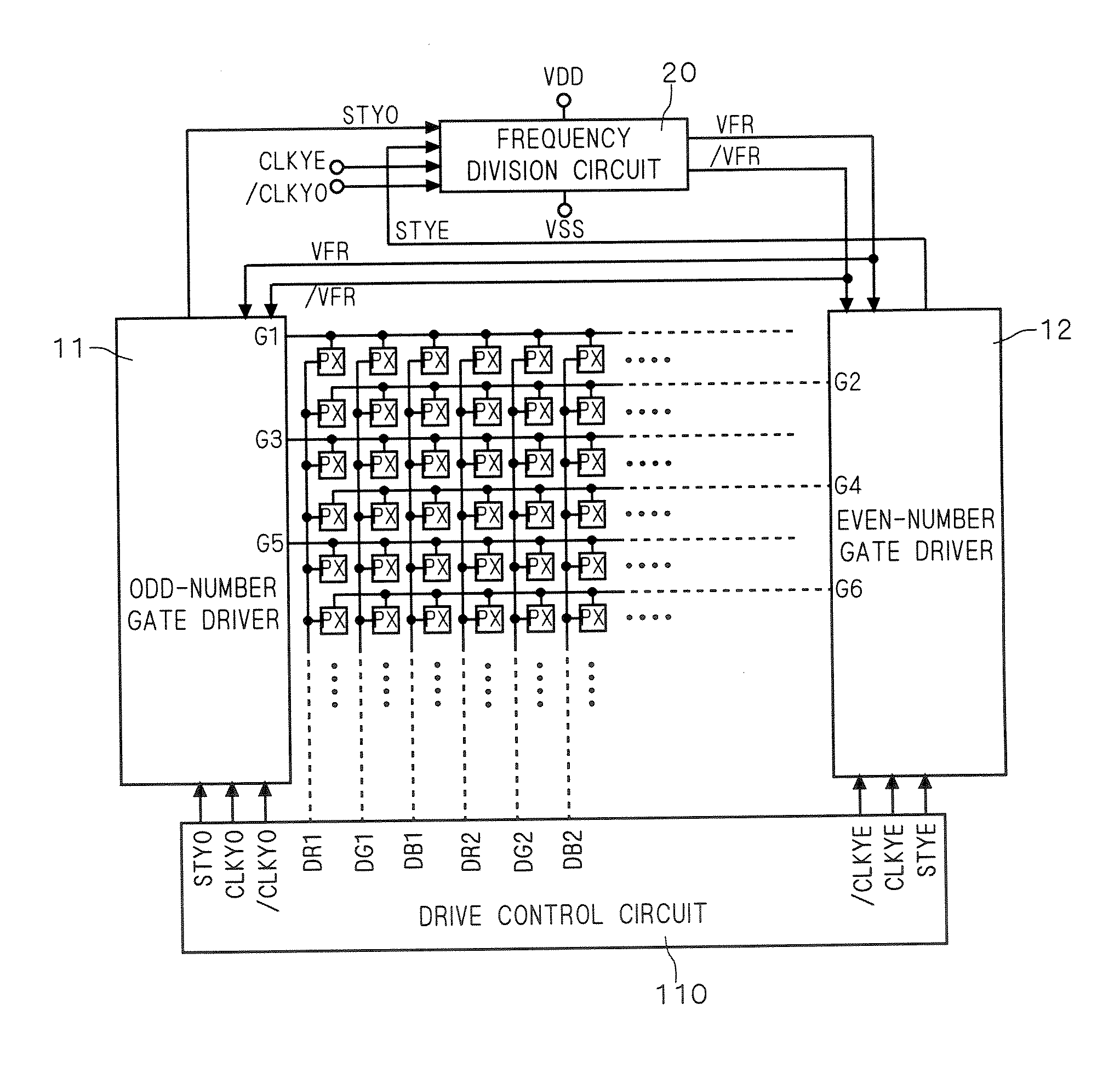

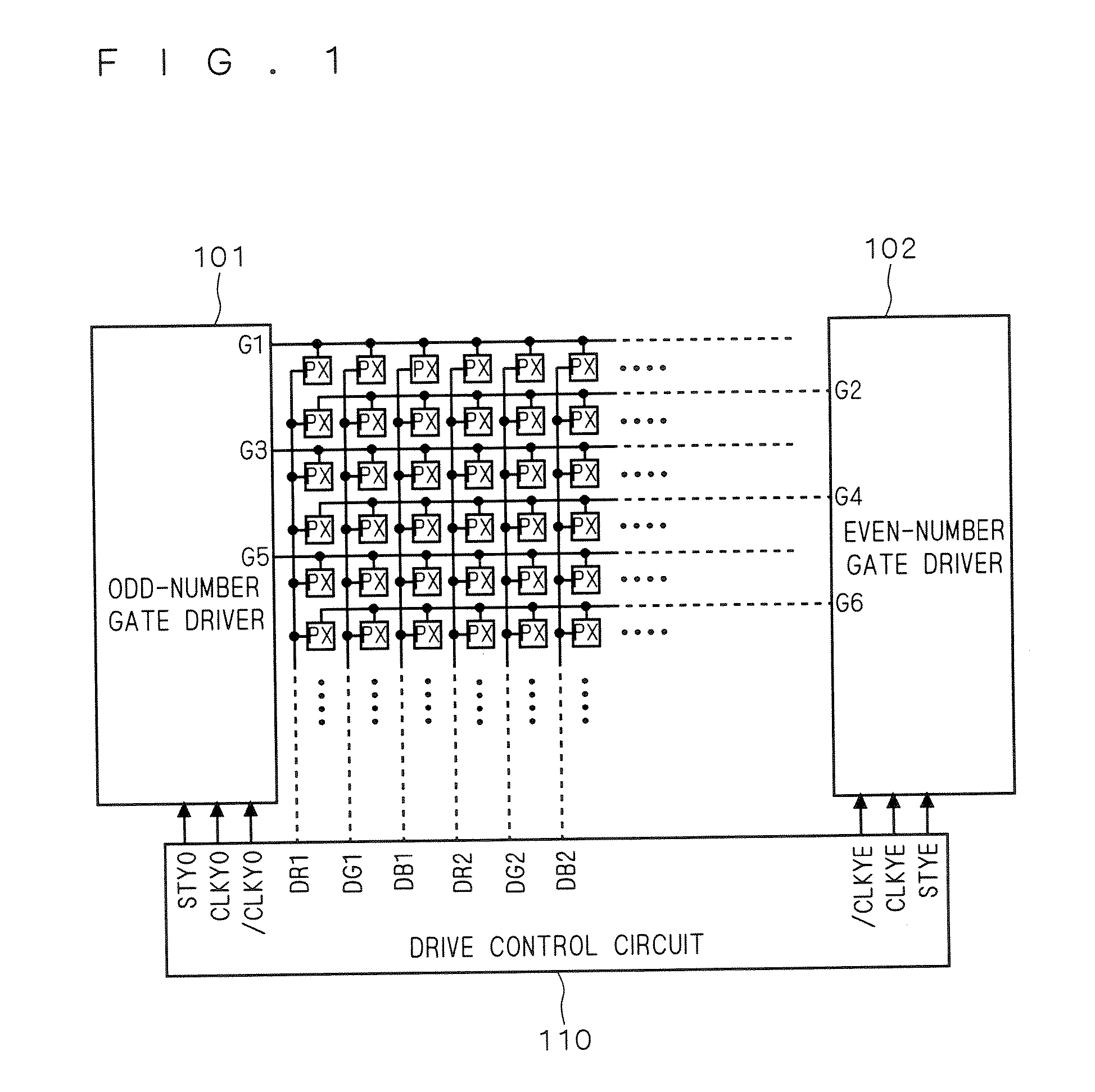

Display device

InactiveUS20070075959A1Suppress mutationAvoid failureStatic indicating devicesDigital storageControl signalDisplay device

A display device includes a gate driver for driving pixels (PX), a drive control circuit for outputting a predetermined control signal to the gate driver, and a frequency division circuit. The pixels, the gate driver, and the frequency division circuit are formed using amorphous silicon thin film transistors (a-Si TFTs) formed on an insulating substrate. The control signal output from the drive control circuit includes a start signal for a start of a frame period of an image signal, and the frequency division circuit generates a frequency division signal whose period corresponds to a frequency which is obtained by dividing a frequency of the start signal.

Owner:MITSUBISHI ELECTRIC CORP

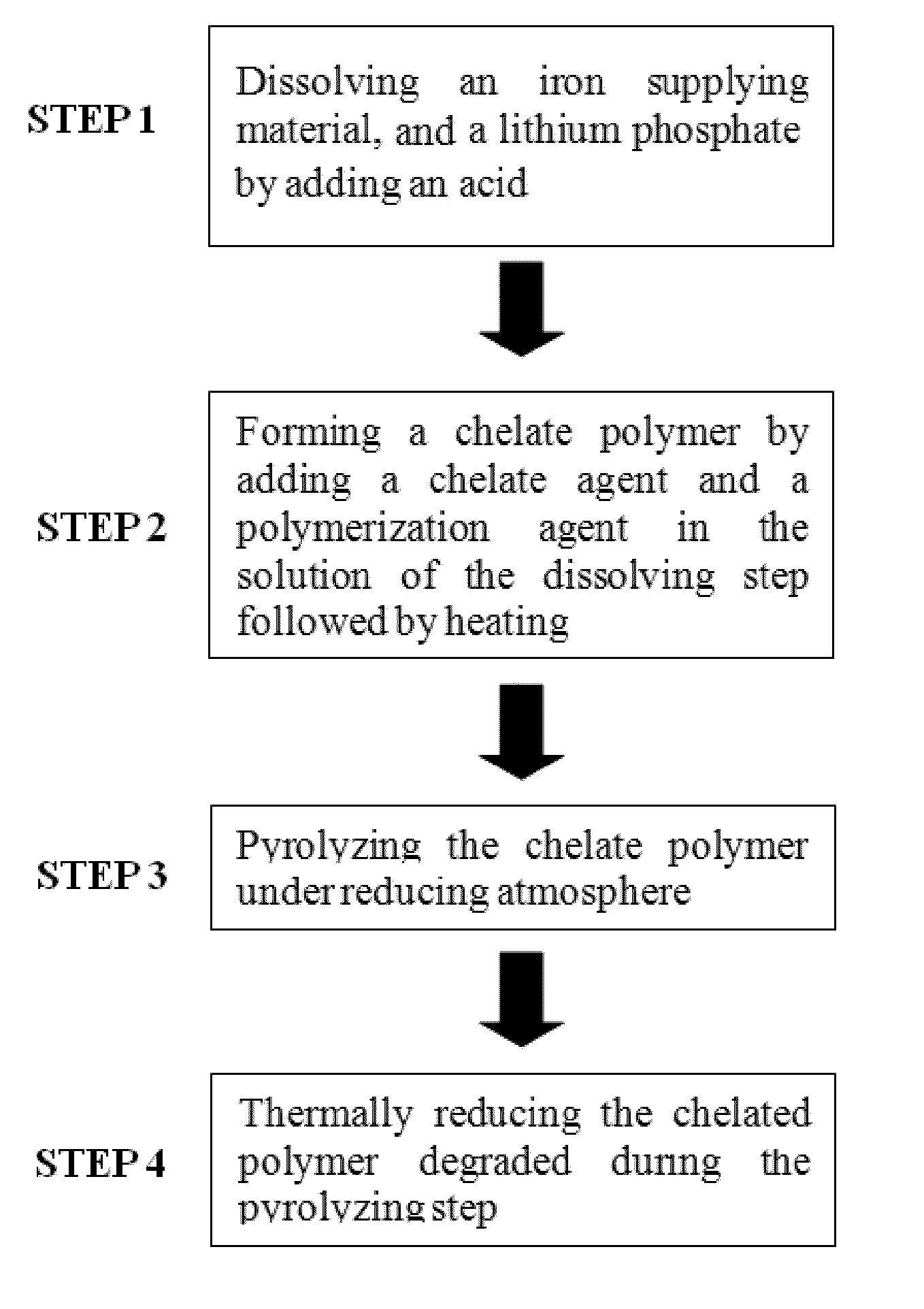

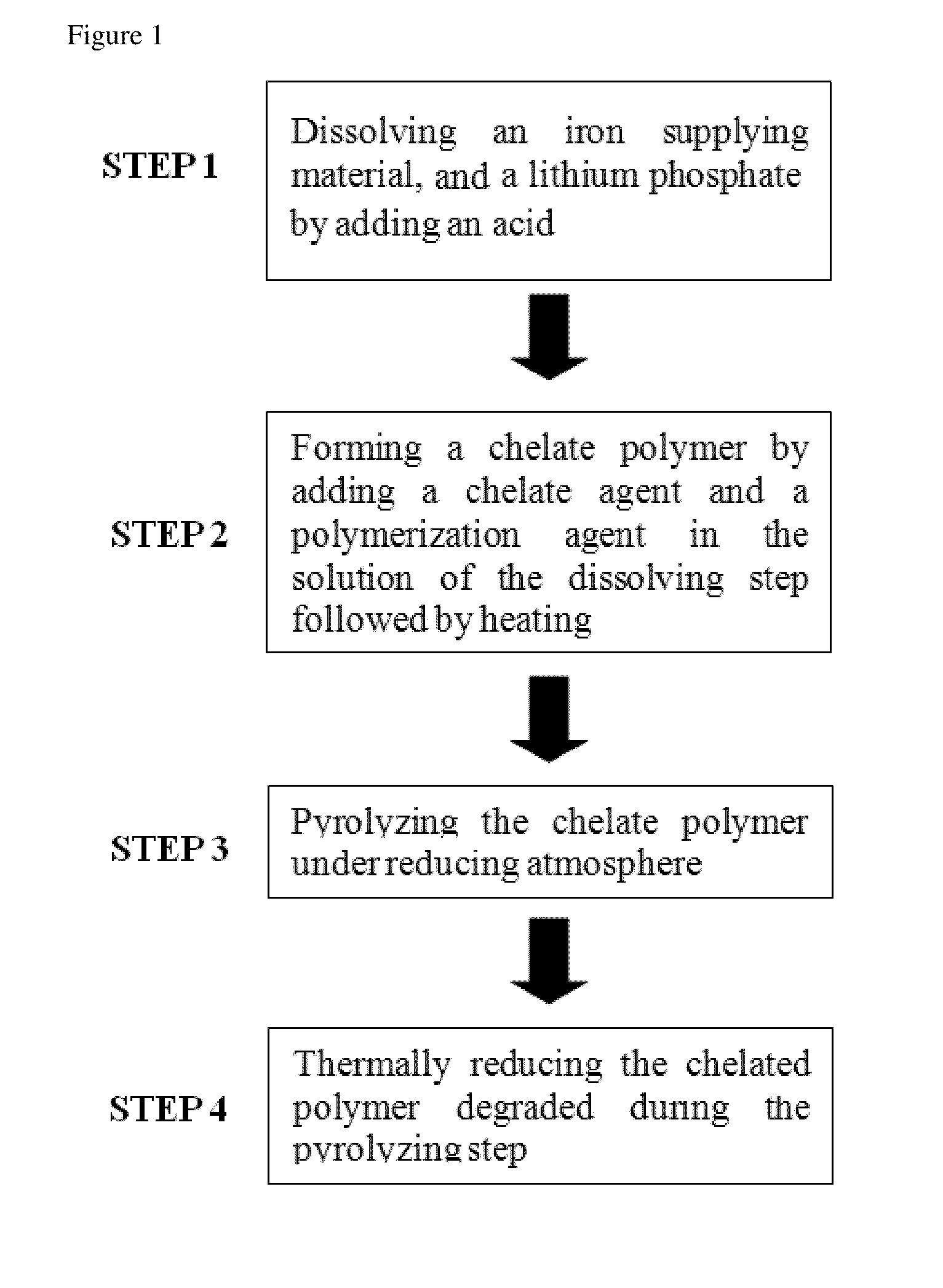

Method of preparing olivine cathod material for lithium secondary battery

InactiveUS20130149227A1Excellent battery characteristicsLarge specific surface areaPhosphatesCell electrodesPolymer scienceElectrical battery

The present invention relates to a method of preparing olivine cathode materials for lithium secondary battery. More specifically, a method of preparing an olivine-based cathode material for secondary battery comprising the steps of: dissolving an iron supplying material, and a lithium phosphate by adding an acid; forming a chelate polymer by adding a chelate agent and a polymerization agent in the solution of the dissolving step followed by heating; pyrolyzing the chelate polymer under reducing atmosphere; and thermally reducing the chelated polymer degraded during the pyrolysis is provided.

Owner:RES INST OF IND SCI & TECH

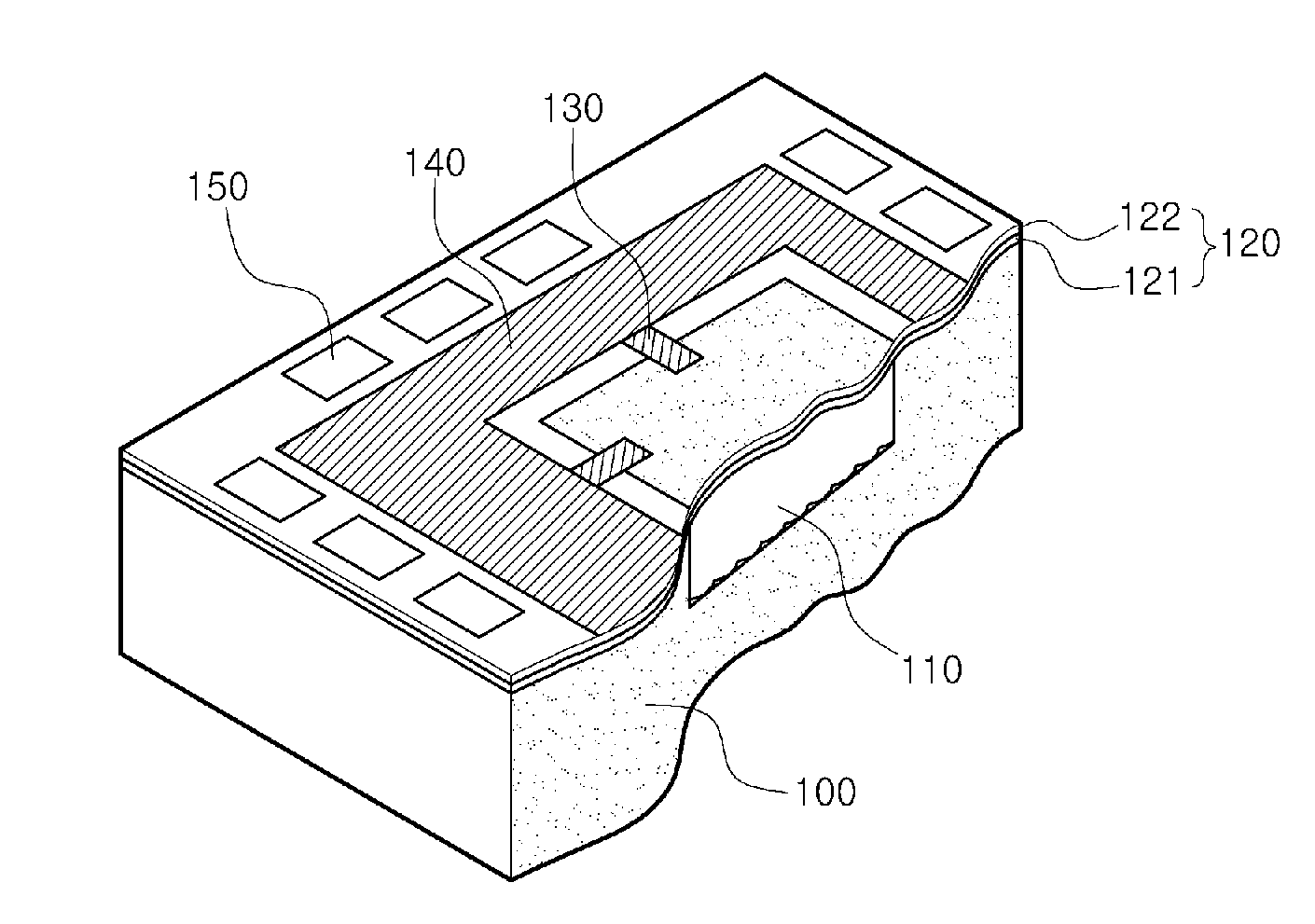

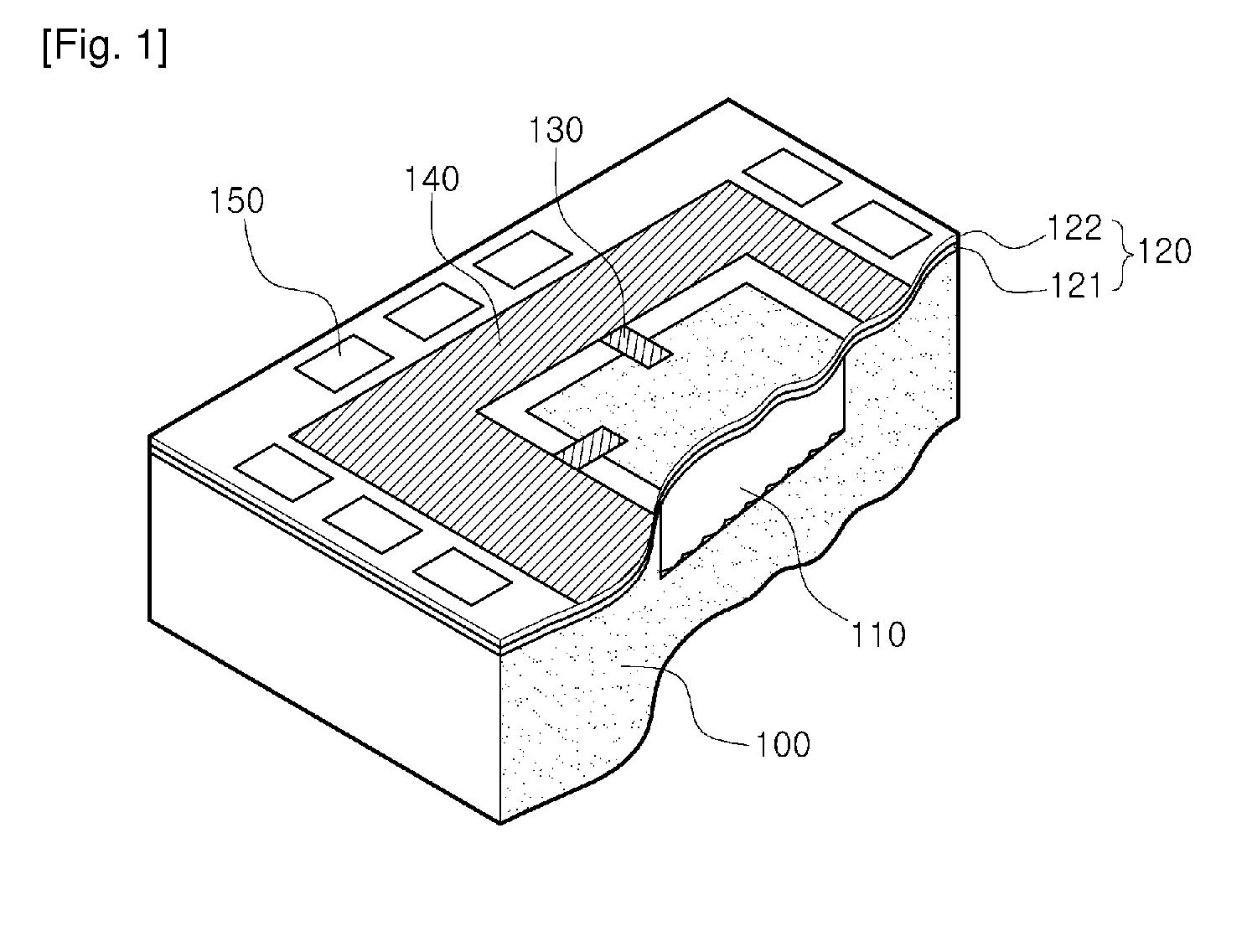

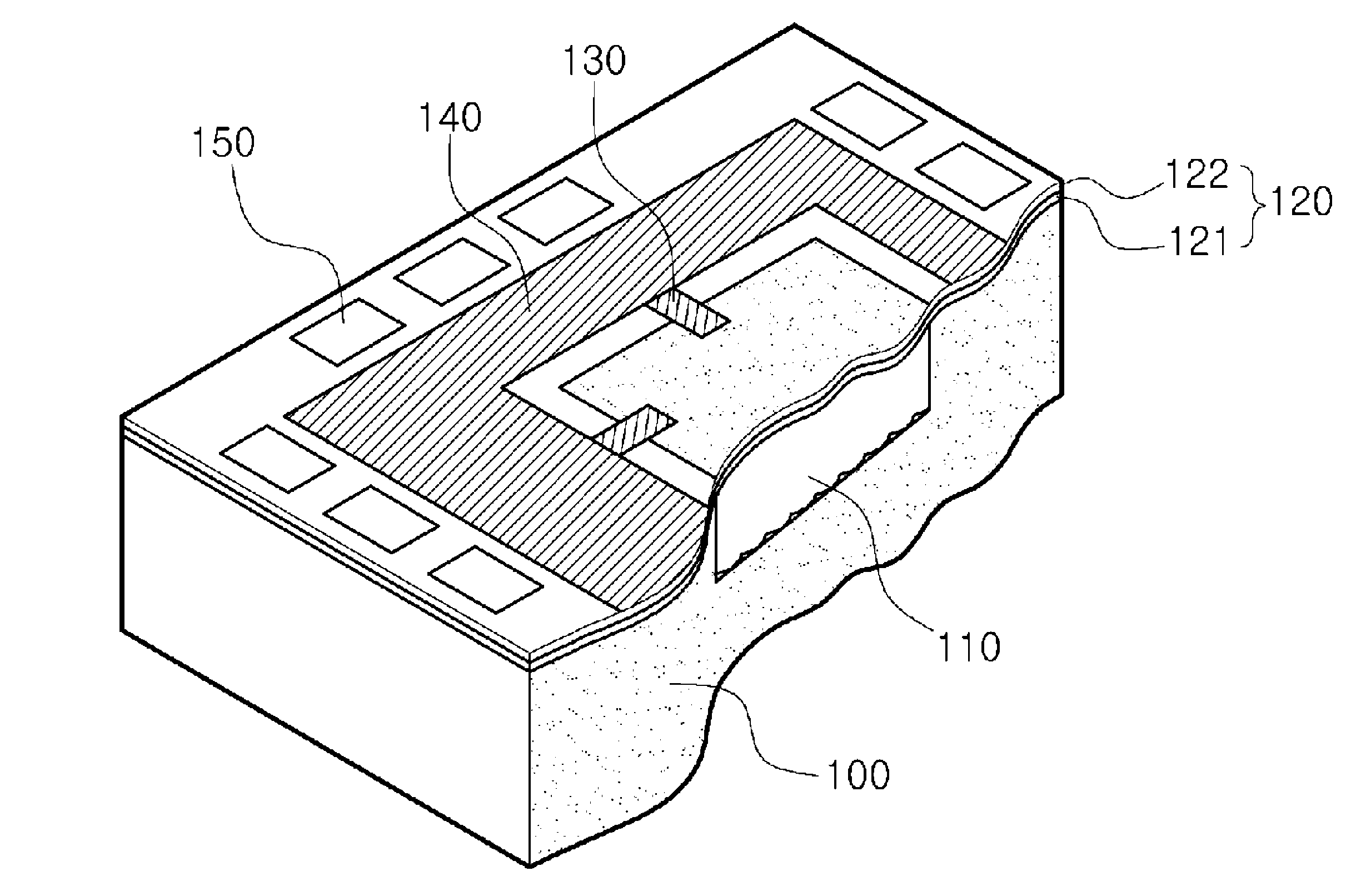

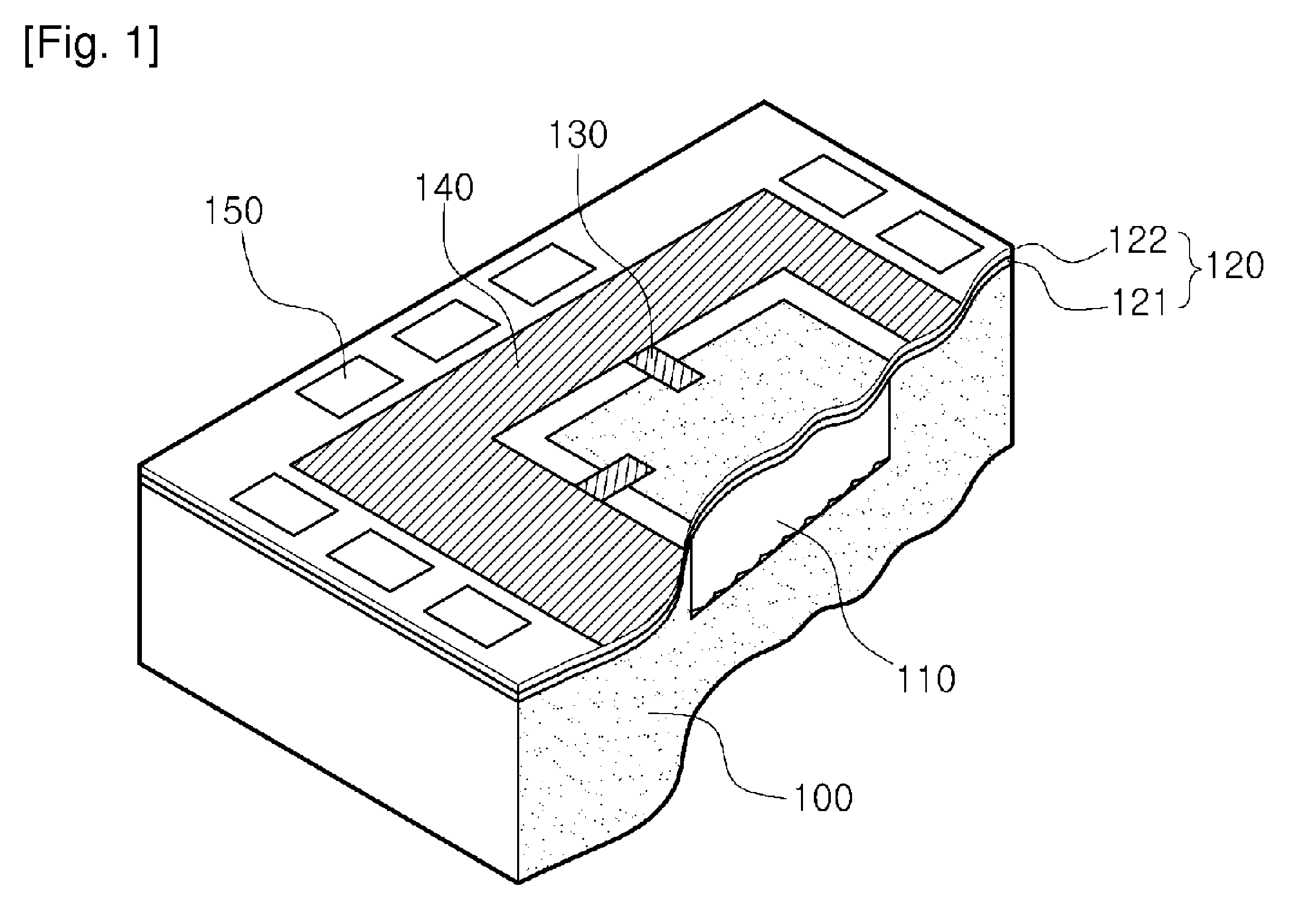

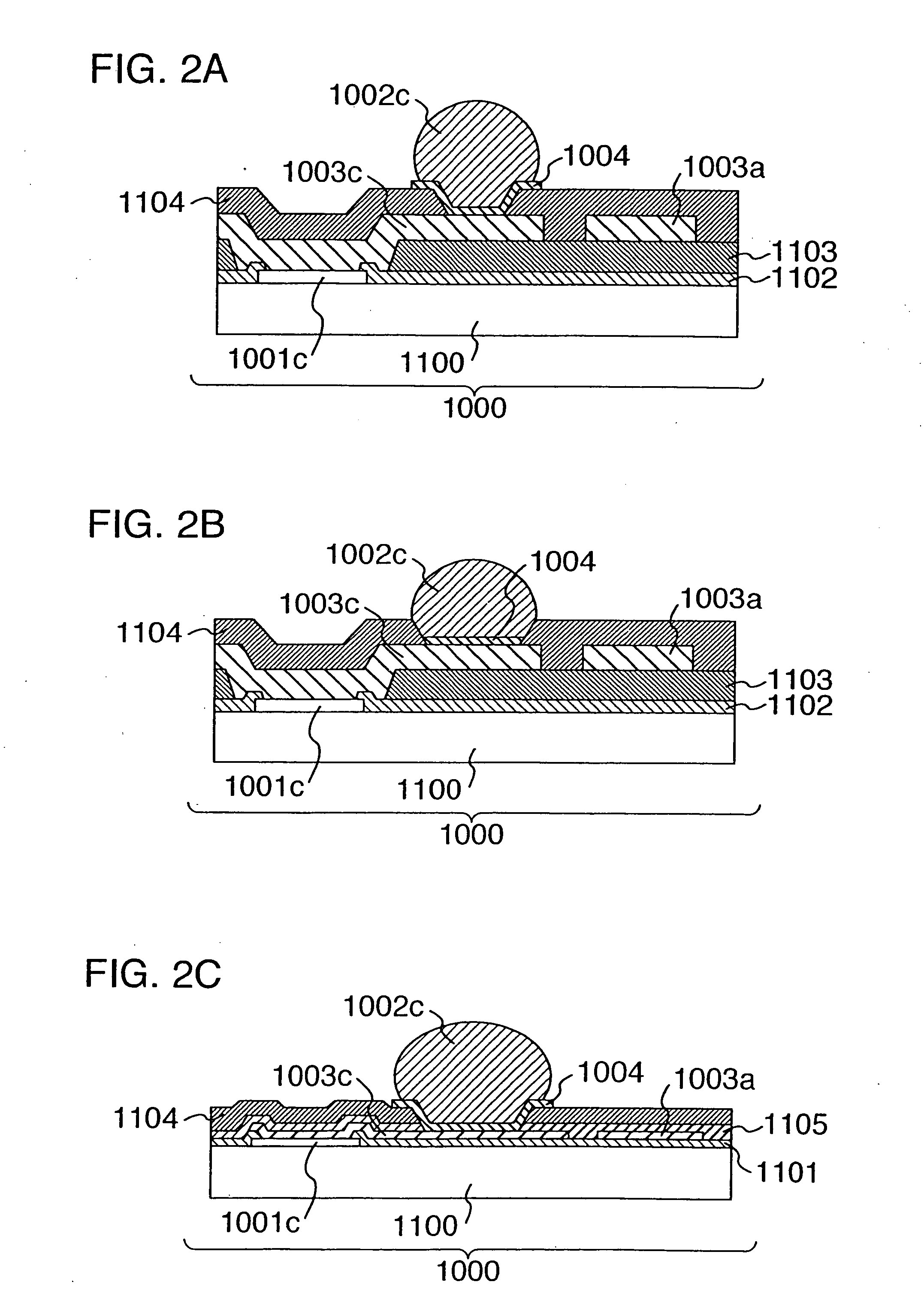

Semiconductor device and manufacturing method thereof

ActiveUS20100102460A1Reduce in quantityManufacturing process is complicatedSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

A semiconductor device and its manufacturing method are offered to increase the number of semiconductor devices obtained from a semiconductor wafer while simplifying a manufacturing process. After forming a plurality of pad electrodes in a predetermined region on a top surface of a semiconductor substrate, a supporter is bonded to the top surface of the semiconductor substrate through an adhesive layer. Next, an opening is formed in the semiconductor substrate in a region overlapping the predetermined region. A wiring layer electrically connected with each of the pad electrodes is formed in the opening. After that, a stacked layer structure including the semiconductor substrate and the supporter is cut by dicing along a dicing line that is outside the opening.

Owner:SEMICON COMPONENTS IND LLC

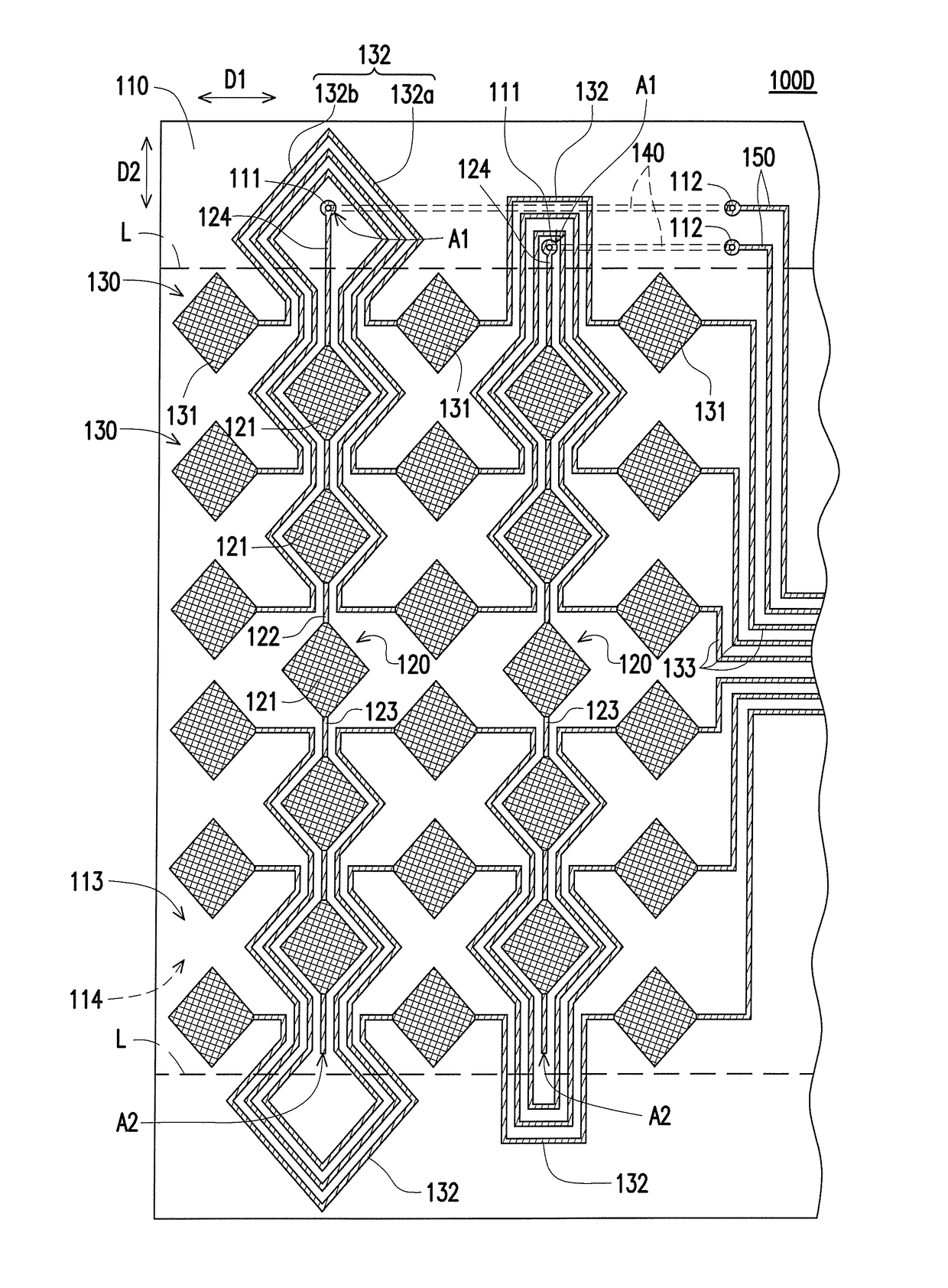

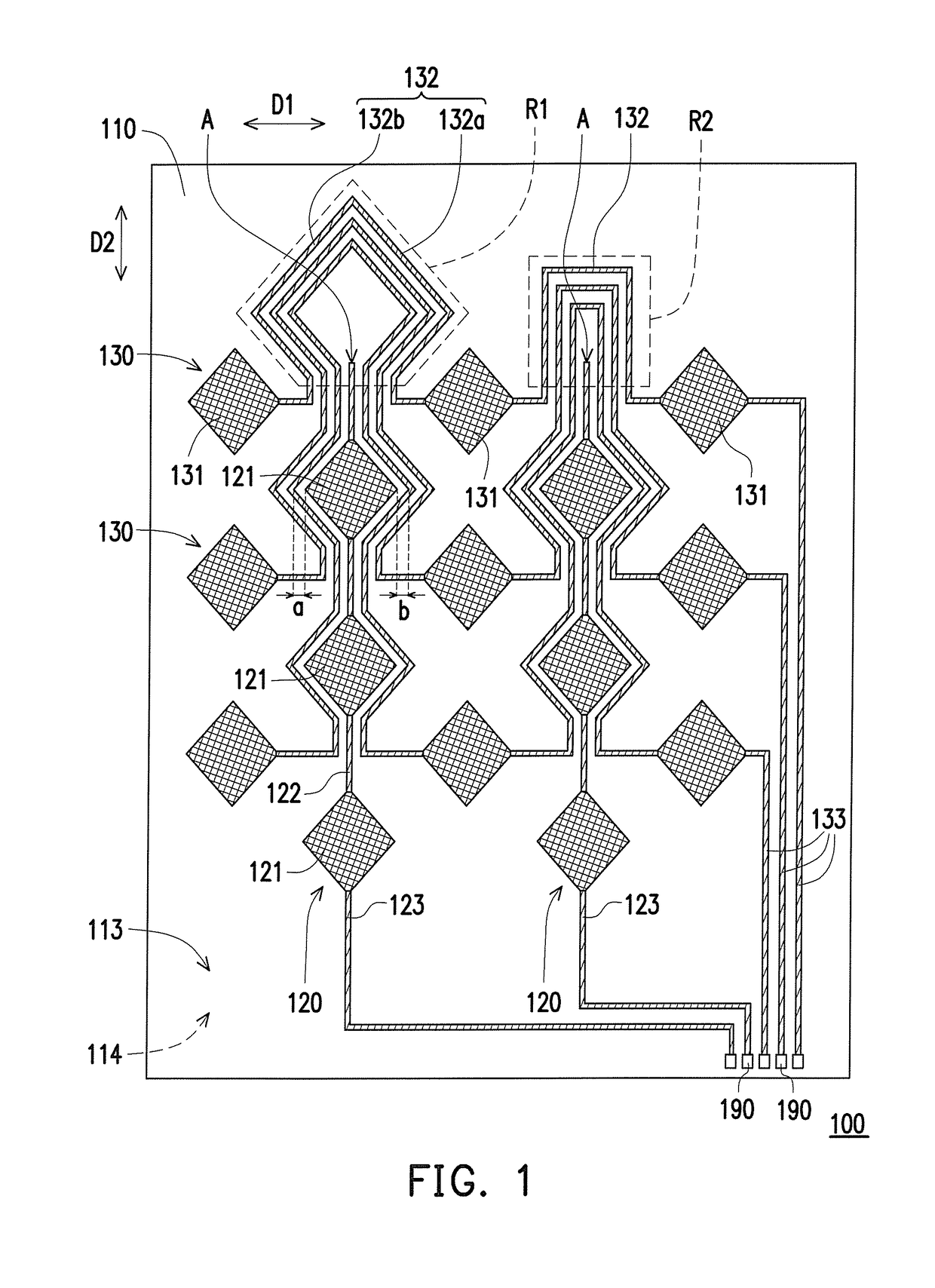

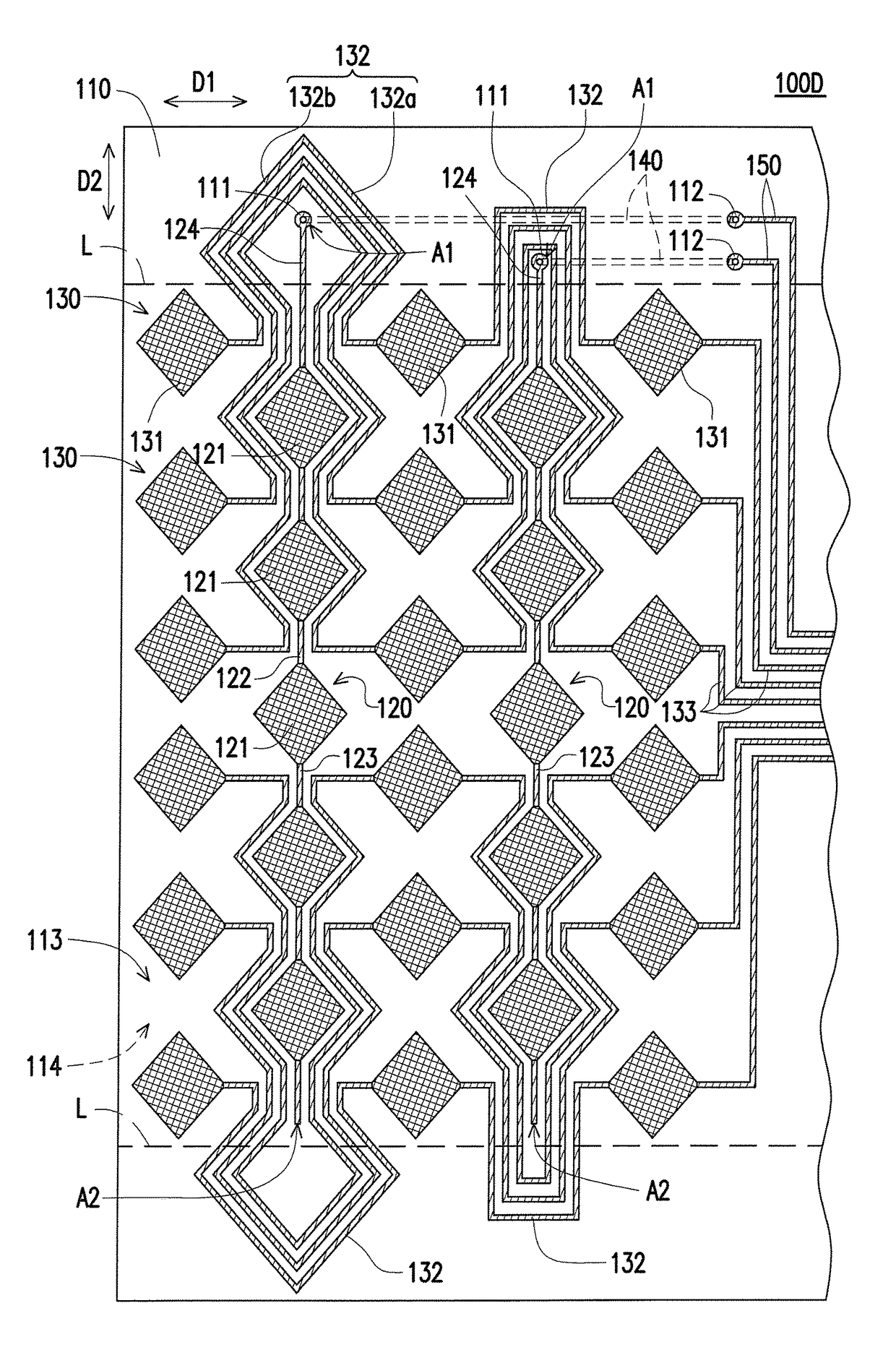

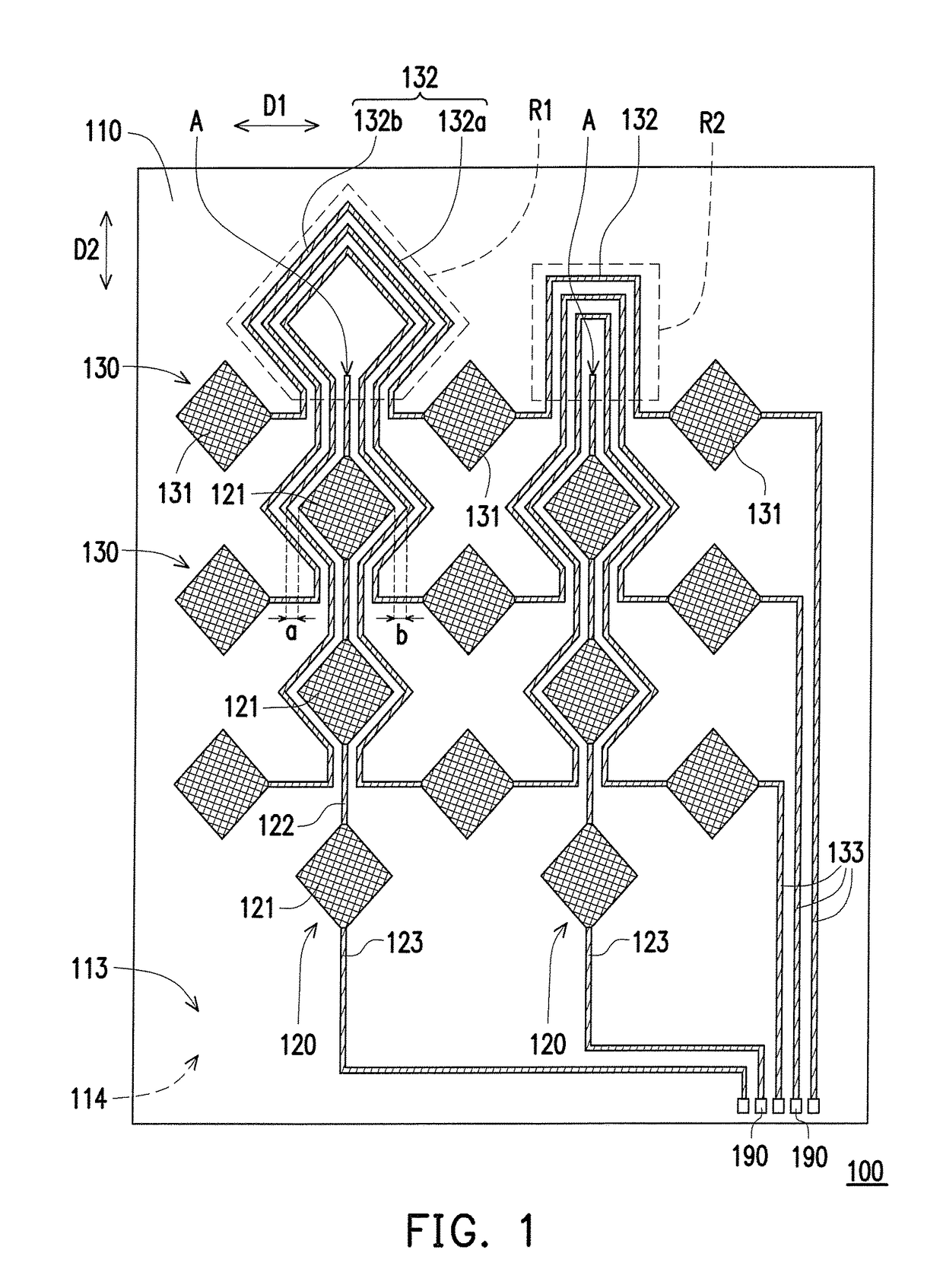

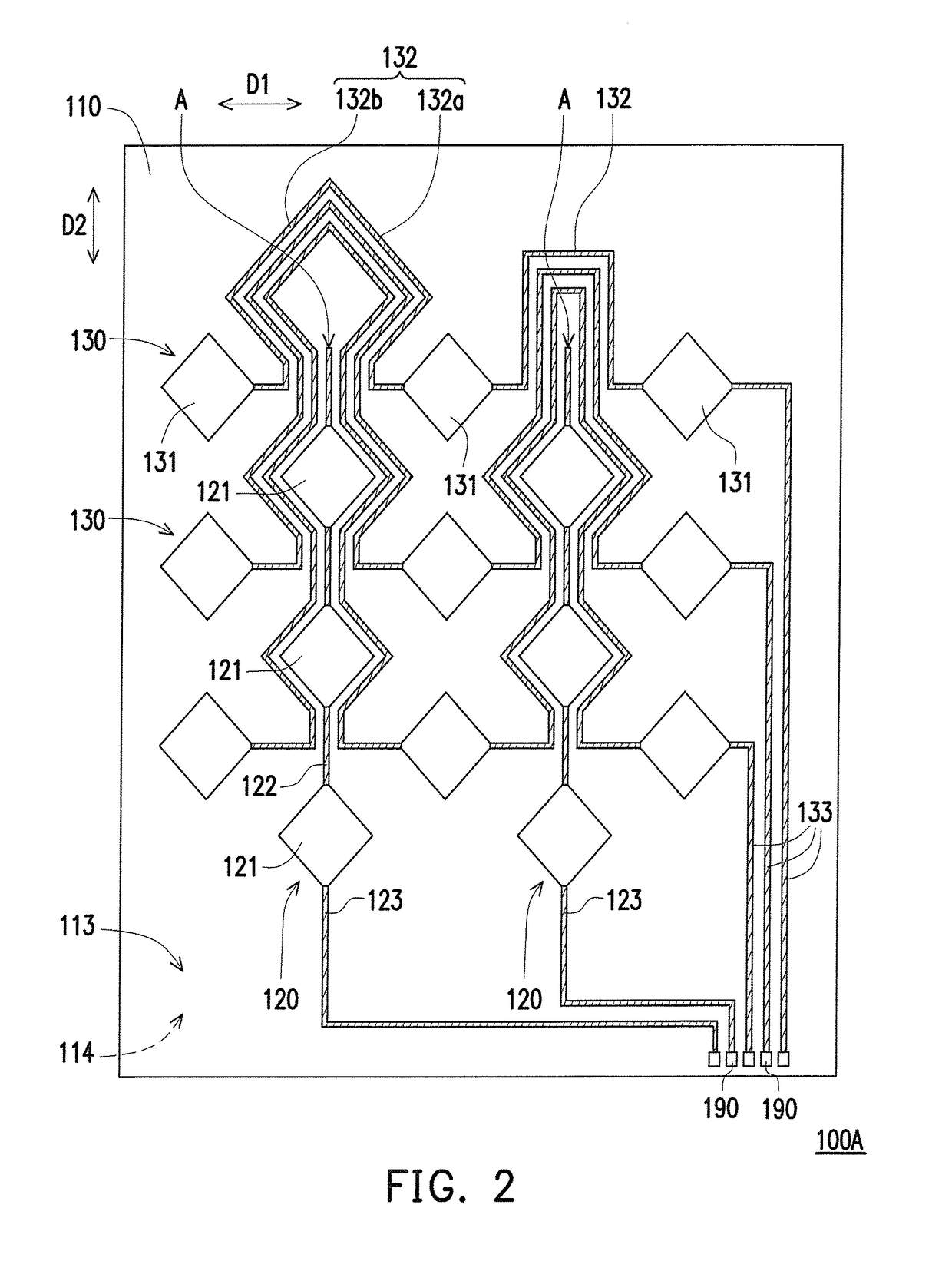

Touch element and touch display module

ActiveUS20170068363A1Lost manufacturing costManufacturing process is complicatedInput/output processes for data processingTouch SensesComputer module

Owner:HANNSTOUCH SOLUTION

Display

ActiveUS7692620B2Reliably inhibit logic composition circuit portionReduce implantationTelevision system detailsColor television detailsShift registerProcessor register

A display capable of inhibiting a logic composition circuit from outputting a signal to a gate line or a drain line at unintentional timing is obtained. This display comprises a shift register circuit including a logic composition circuit portion constituted of a plurality of first conductive type transistors turned on with a first voltage supply source for receiving a first shift signal and a second shift signal and outputting a shift output signal by logically compositing the first shift signal and the second shift signal with each other. At least either a first shift register circuit portion or a second shift register circuit portion includes a reset transistor for resetting the voltage supply source of a node outputting the first shift signal or the second shift signal to a second voltage supply source not turning on the transistors of the logic composition circuit portion in response to a prescribed drive signal.

Owner:JAPAN DISPLAY WEST

Micro piezoresistive pressure sensor and manufacturing method thereof

ActiveUS8261617B2Manufacturing process is complicatedOvercome difficultiesFluid pressure measurement using ohmic-resistance variationMicrostructural device manufactureEngineeringPiezoresistive pressure sensors

A micro semiconductor-type pressure sensor and a manufacturing method thereof are provided. The micro semi-conductor-type pressure sensor is implemented by etching a cavity-formation region of a substrate to form a plurality of trenches, oxidizing the plurality of trenches through a thermal oxidation process to form a cavity-formation oxide layer, forming a membrane-formation material layer on upper portions of the cavity-formation oxide layer and the substrate, forming a plurality of etching holes in the membrane-formation material layer, removing the cavity-formation oxide layer through the plurality of etching holes to form a cavity buried in the substrate, forming a membrane reinforcing layer on an upper portion of the membrane-formation material layer to form a membrane for closing the cavity, and forming sensitive films made of a piezoresisive material on an upper portion of the membrane.

Owner:ELECTRONICS & TELECOMM RES INST

Semiconductor device and manufacturing method thereof

ActiveUS8598720B2Reduce in quantityManufacturing process is complicatedSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

A semiconductor device and its manufacturing method are offered to increase the number of semiconductor devices obtained from a semiconductor wafer while simplifying a manufacturing process. After forming a plurality of pad electrodes in a predetermined region on a top surface of a semiconductor substrate, a supporter is bonded to the top surface of the semiconductor substrate through an adhesive layer. Next, an opening is formed in the semiconductor substrate in a region overlapping the predetermined region. A wiring layer electrically connected with each of the pad electrodes is formed in the opening. After that, a stacked layer structure including the semiconductor substrate and the supporter is cut by dicing along a dicing line that is outside the opening.

Owner:SEMICON COMPONENTS IND LLC

Display

InactiveUS7777711B2Reliably inhibit logic composition circuit portionReduce implantationColor signal processing circuitsCathode-ray tube indicatorsShift registerDisplay device

A display capable of inhibiting a logic composition circuit from outputting a signal to a gate line or a drain line at unintentional timing is obtained. In this display, at least either a first shift register circuit portion or a second shift register circuit portion includes a reset transistor for resetting the voltage supply source of a node outputting a first shift signal or a second shift signal to a second voltage supply source not turning on transistors of a logic composition circuit portion in response to an output signal received from a shift register circuit portion precedent thereto by at least two stages with respect to a scanning direction.

Owner:JAPAN DISPLAY WEST

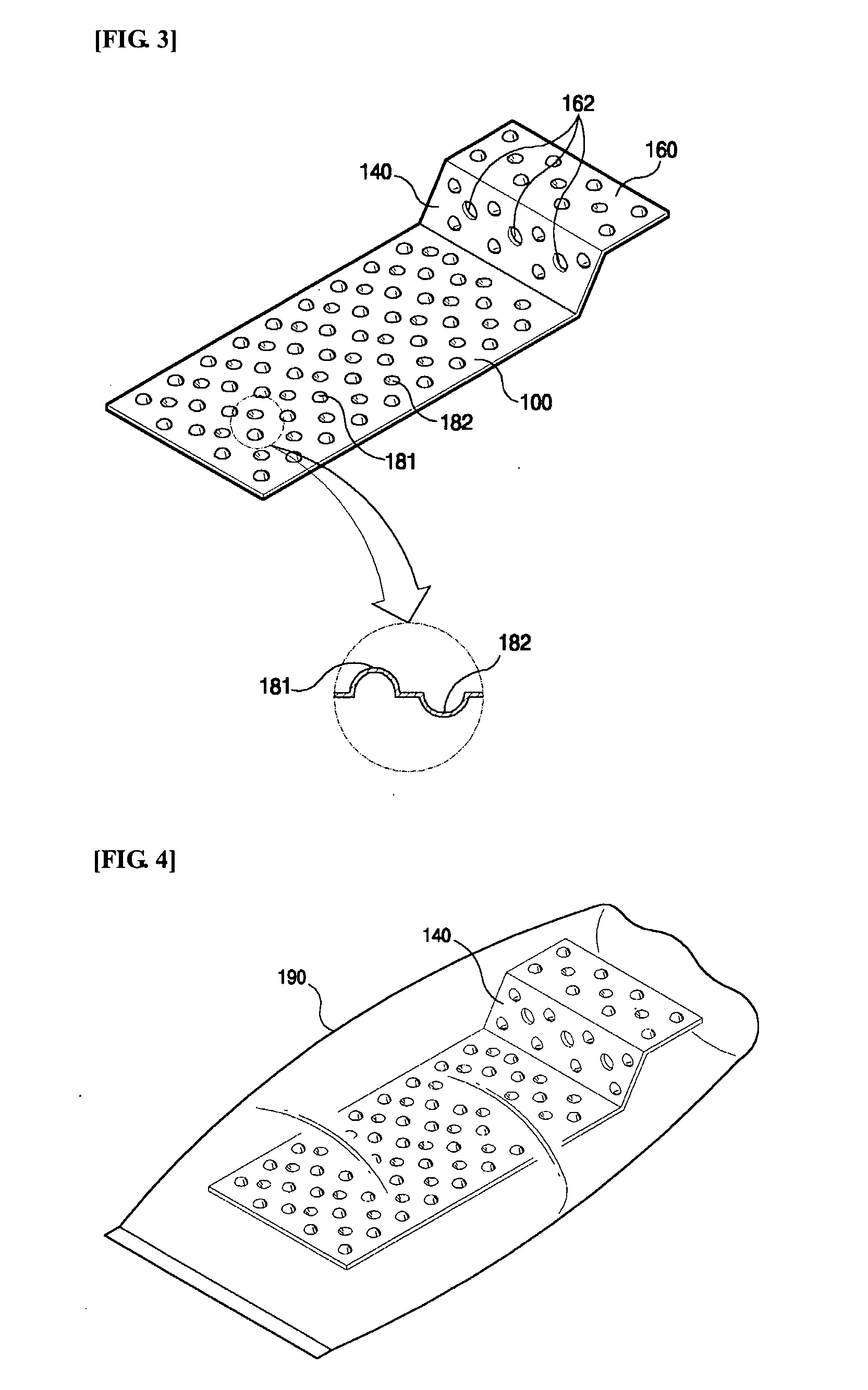

Vacuum tray for vacuum packing

The present invention relates to a vacuum tray which is inserted into a vacuum bag and makes it possible for the vacuum bag to be easily vacuumized even if the vacuum bag has no embossments. Particularly, the vacuum tray is characterize in that an airflow defining part (200), which can be thermally bonded to a vacuum bag, is provided at a front end of the vacuum tray so that air in the vacuum bag is easily discharged to the outside through an opening of the vacuum bag. Furthermore, the present invention is characterized in that a cover (400) may be coupled to the vacuum tray, thus preventing appearance of a food from being deformed.

Owner:AHN JOON YOUNG

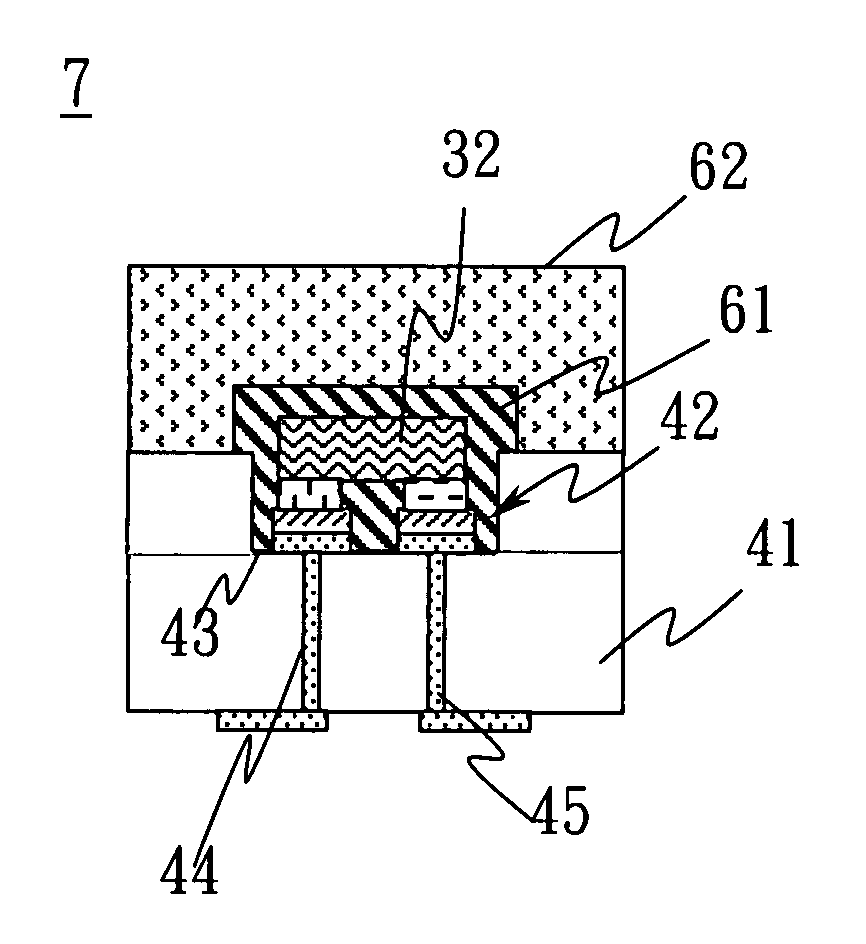

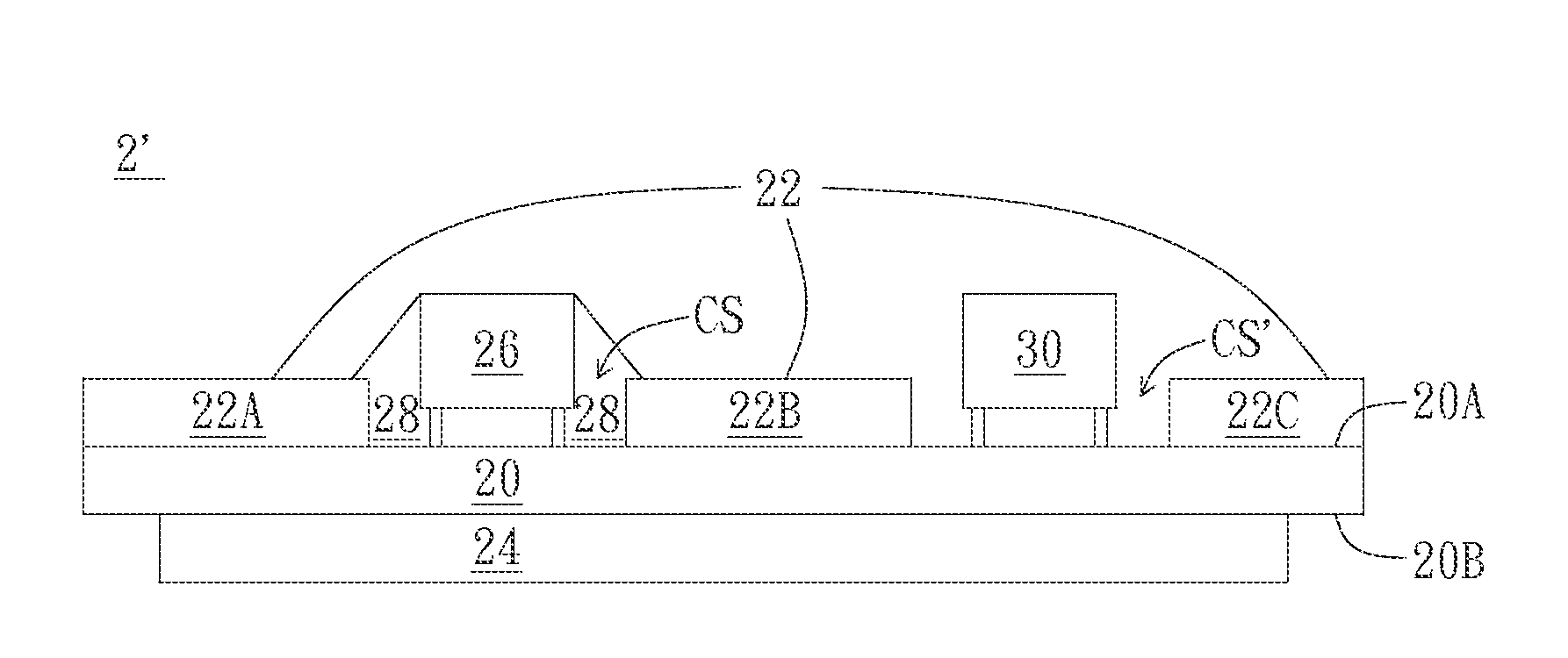

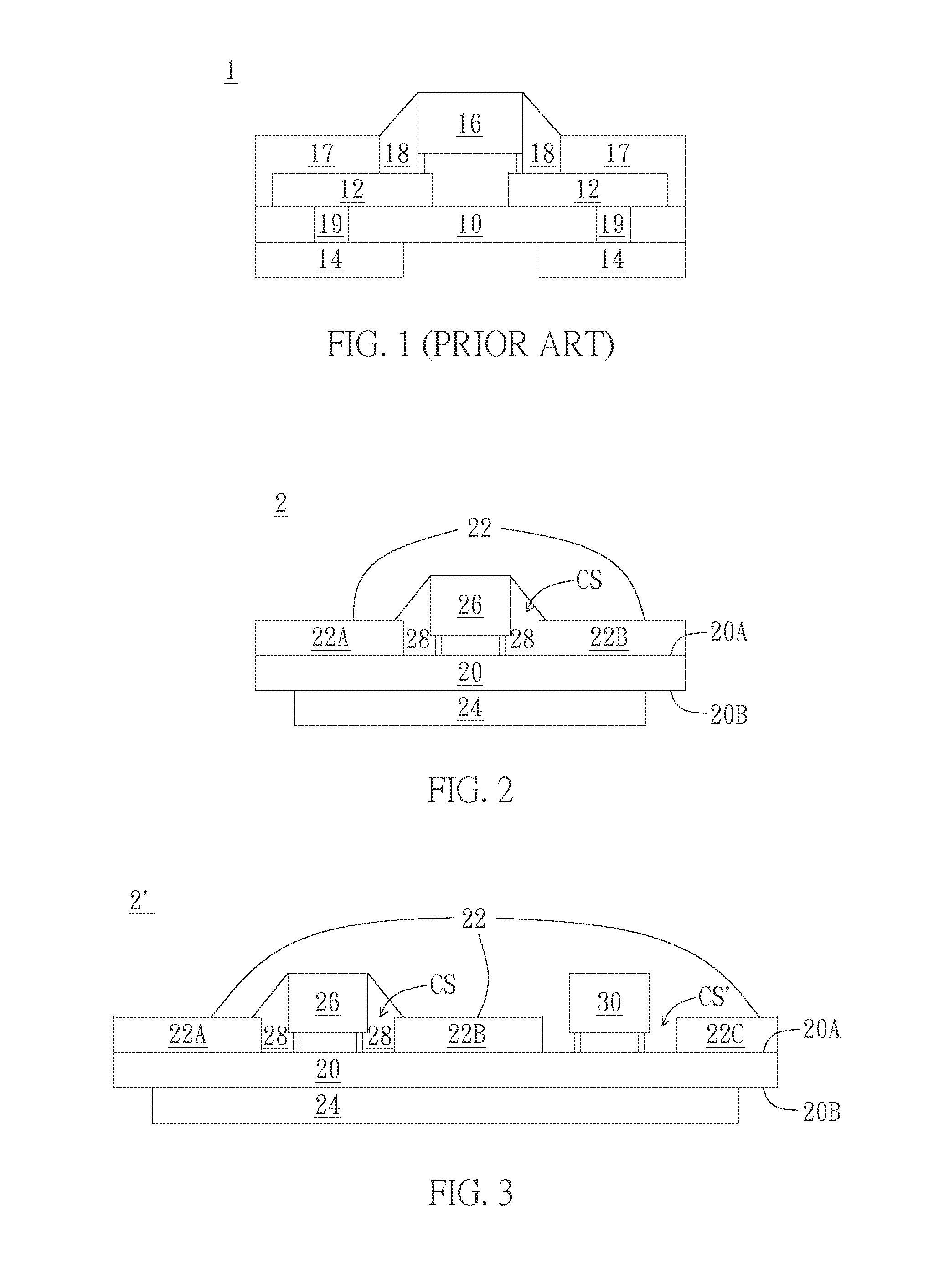

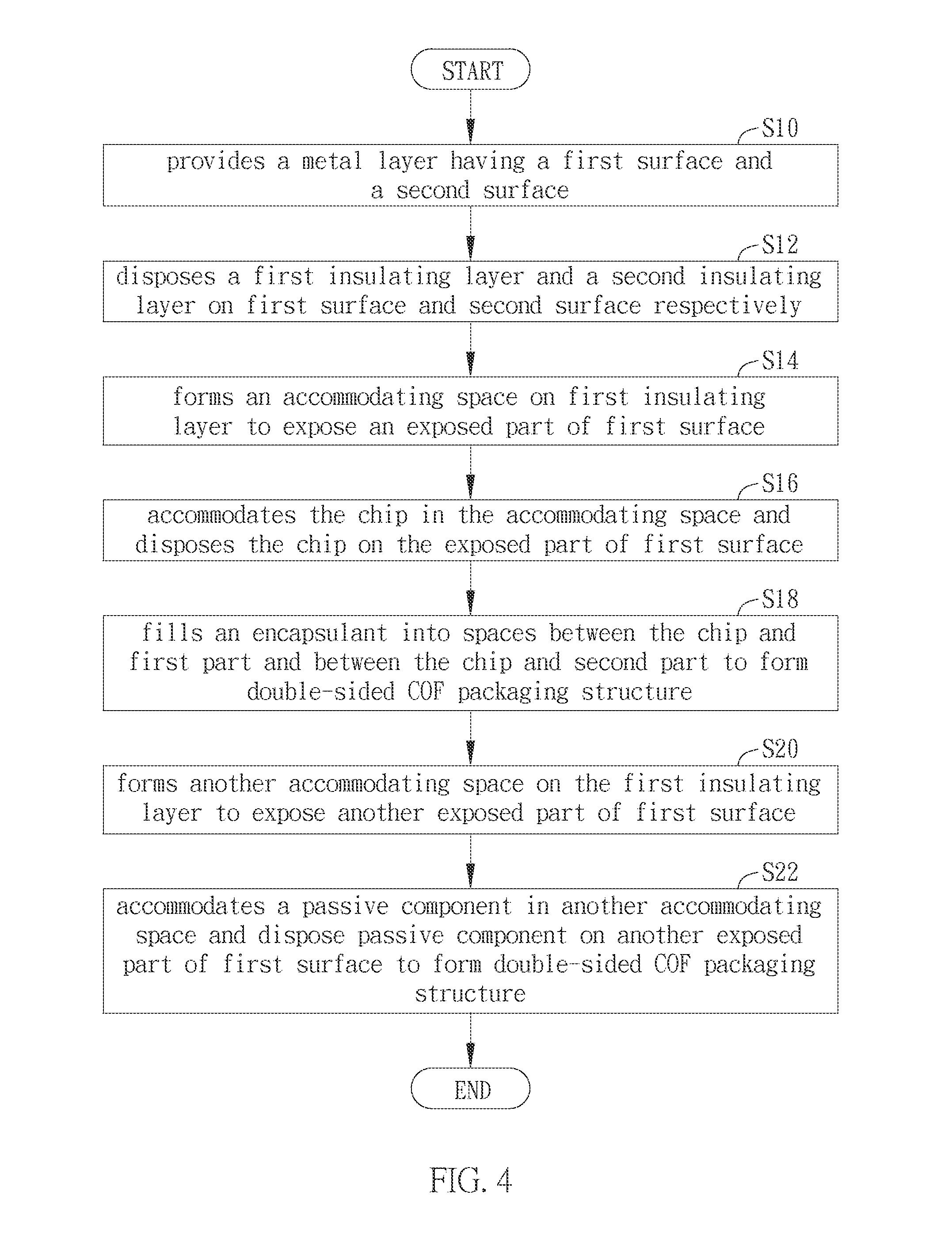

Double-sided chip on film packaging structure and manufacturing method thereof

InactiveUS20160133550A1Manufacturing process be complicateEnhance production yieldSemiconductor/solid-state device detailsSolid-state devicesChip on filmElectrical and Electronics engineering

A double-sided chip on film (COF) packaging structure and a manufacturing method thereof are disclosed. The double-sided COF structure includes a metal layer, a first insulating layer, a second insulating layer, a chip, and an encapsulant. The first insulating layer and second insulating layer are disposed on a first surface and a second surface of metal layer respectively. The first surface and second surface are opposite. The first insulating layer includes a first part and a second part separated from each other. An accommodating space is existed between the first part and the second part and a part of the first surface is exposed. The chip is accommodated in the accommodating space and disposed on the exposed part of the first surface. The encapsulant fills the spaces between the chip and the first part and between the chip and the second part to form the double-sided COF packaging structure.

Owner:RAYDIUM SEMICON

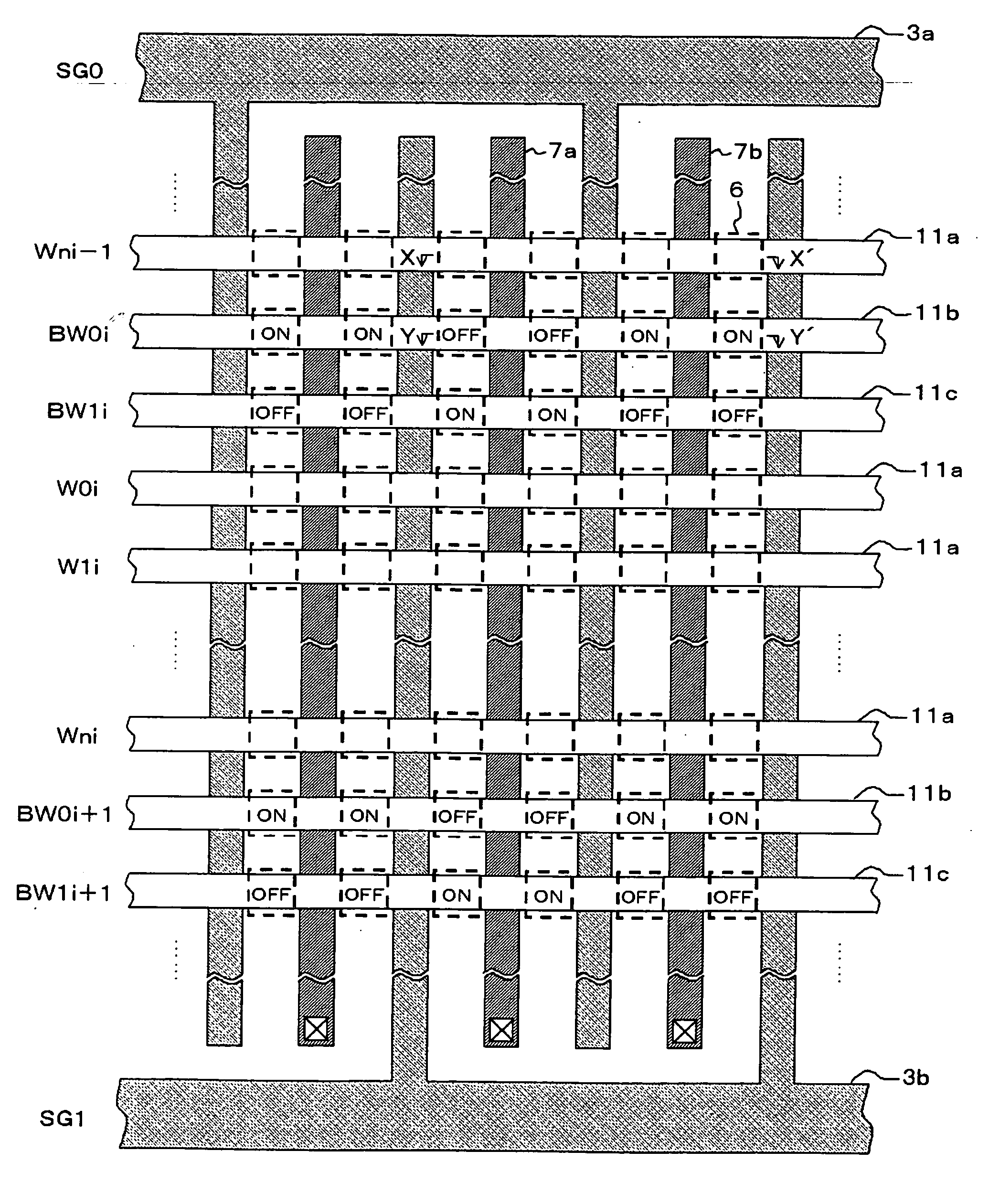

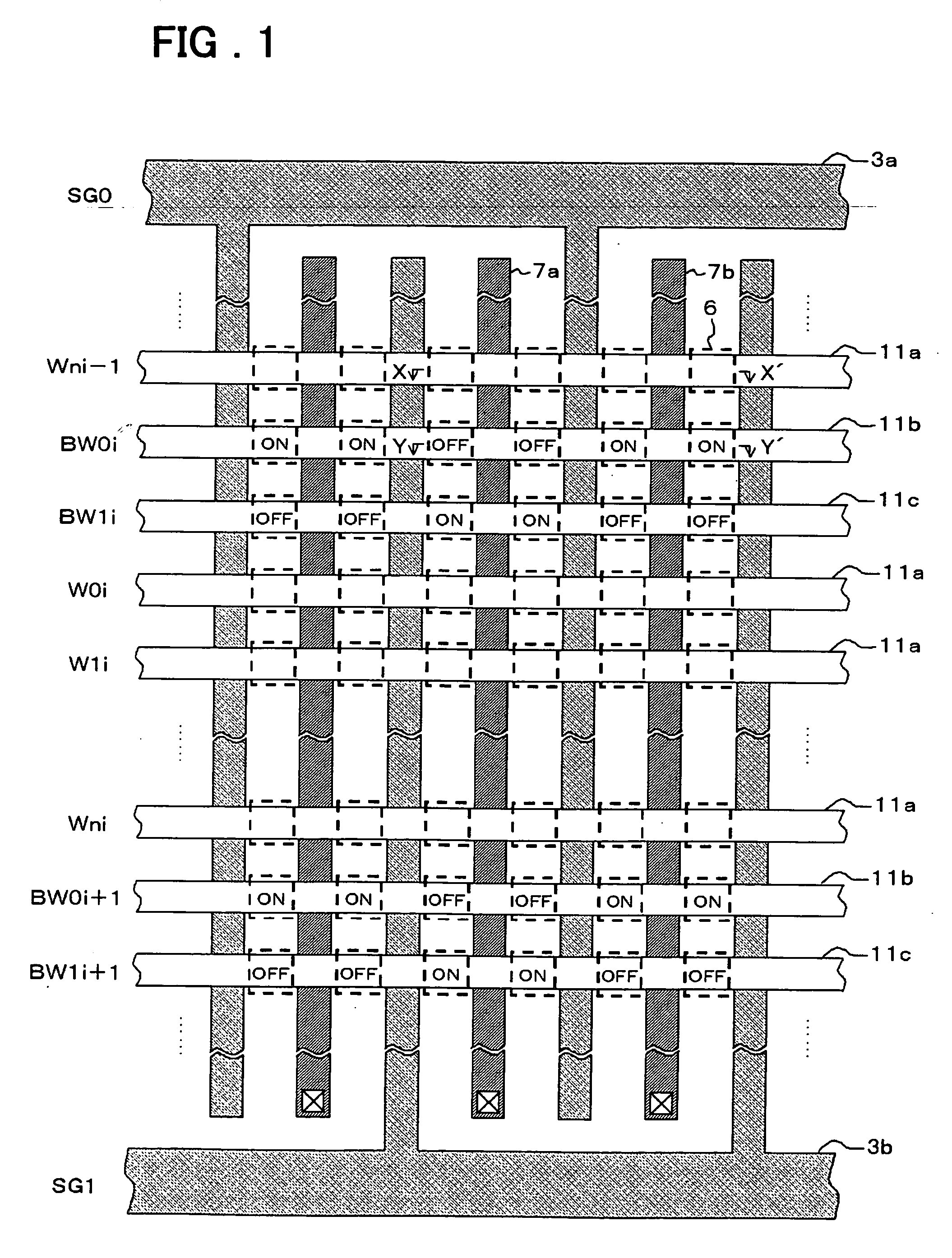

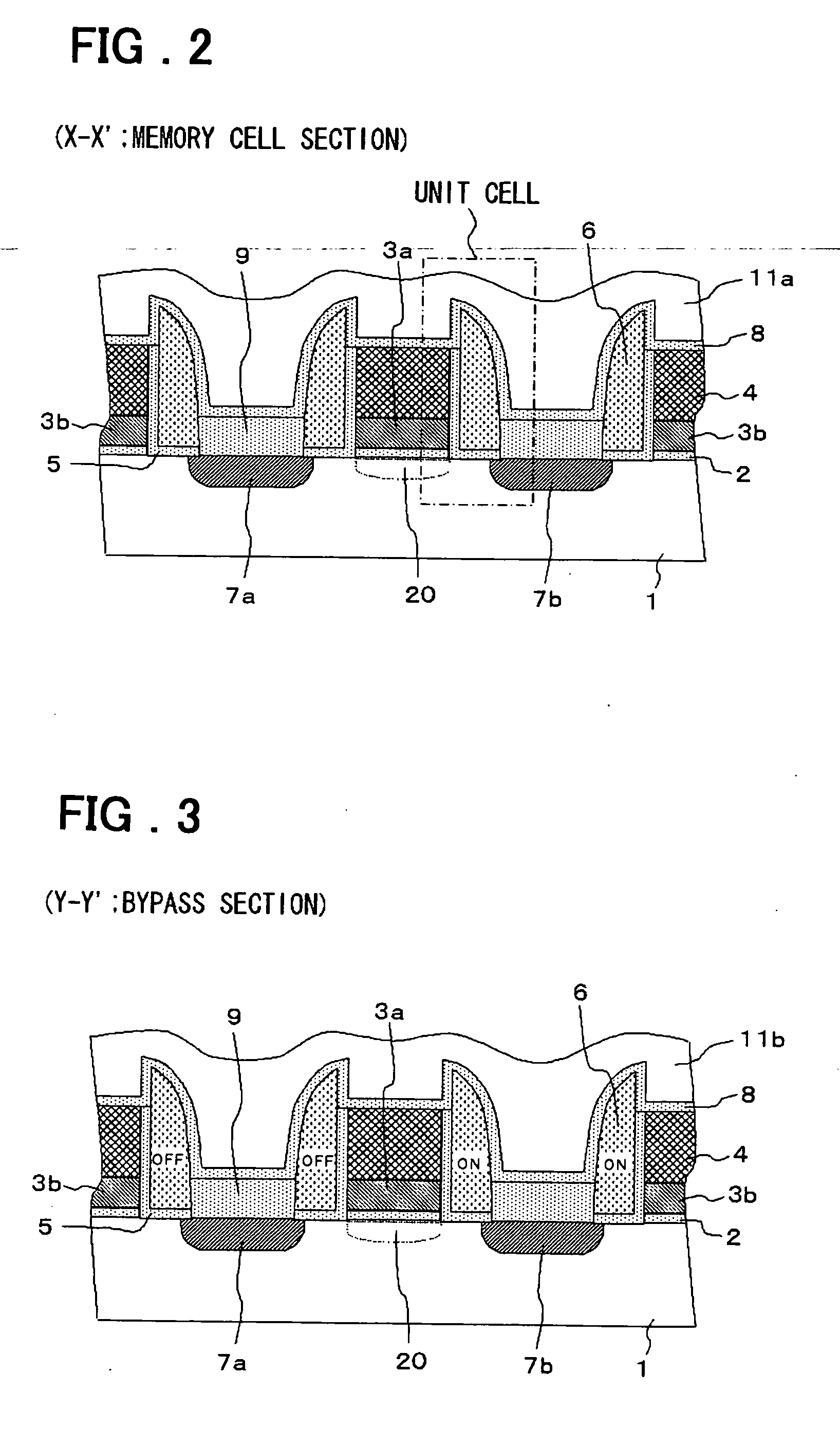

Semiconductor storage device

ActiveUS20070045715A1Manufacturing process is complicatedIncrease production costTransistorSolid-state devicesSemiconductor storage devicesEngineering

A semiconductor storage device in which product cost is reduced includes a memory cell section (cells belonging to word lines) and a bypass section (cells belonging to bypass word lines). The memory cell section has a select gate, floating gates, a first diffusion region, a second diffusion region and a first control gate. The bypass section has the first select gate, the first diffusion region, the second diffusion region and a second control gate. The second control gate controls a channel in an area between the select gate and the first diffusion region or between the select gate and the second diffusion region. The channel of the bypass section becomes a current supply path when a cell of the memory cell section is read out.

Owner:RENESAS ELECTRONICS CORP

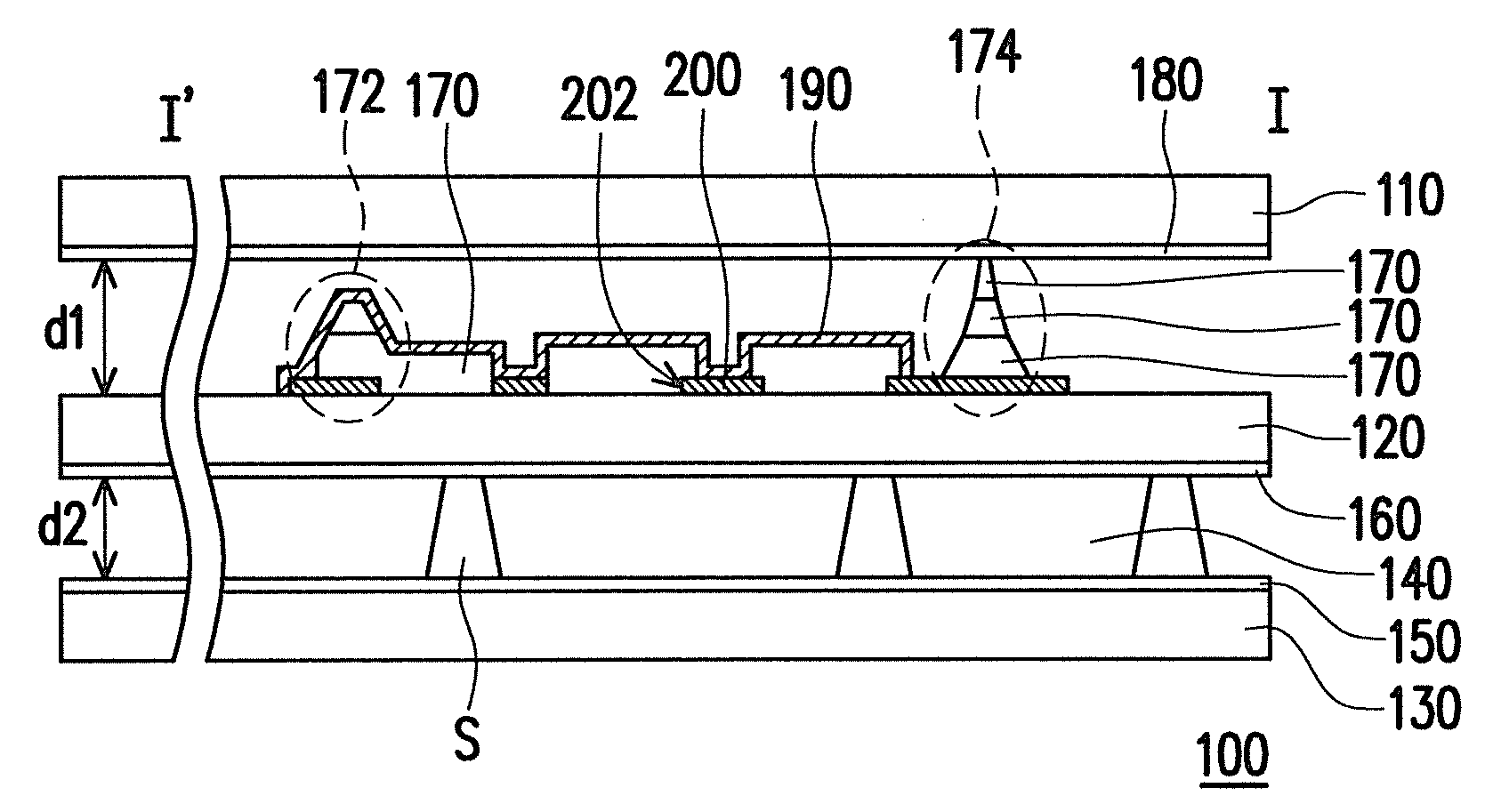

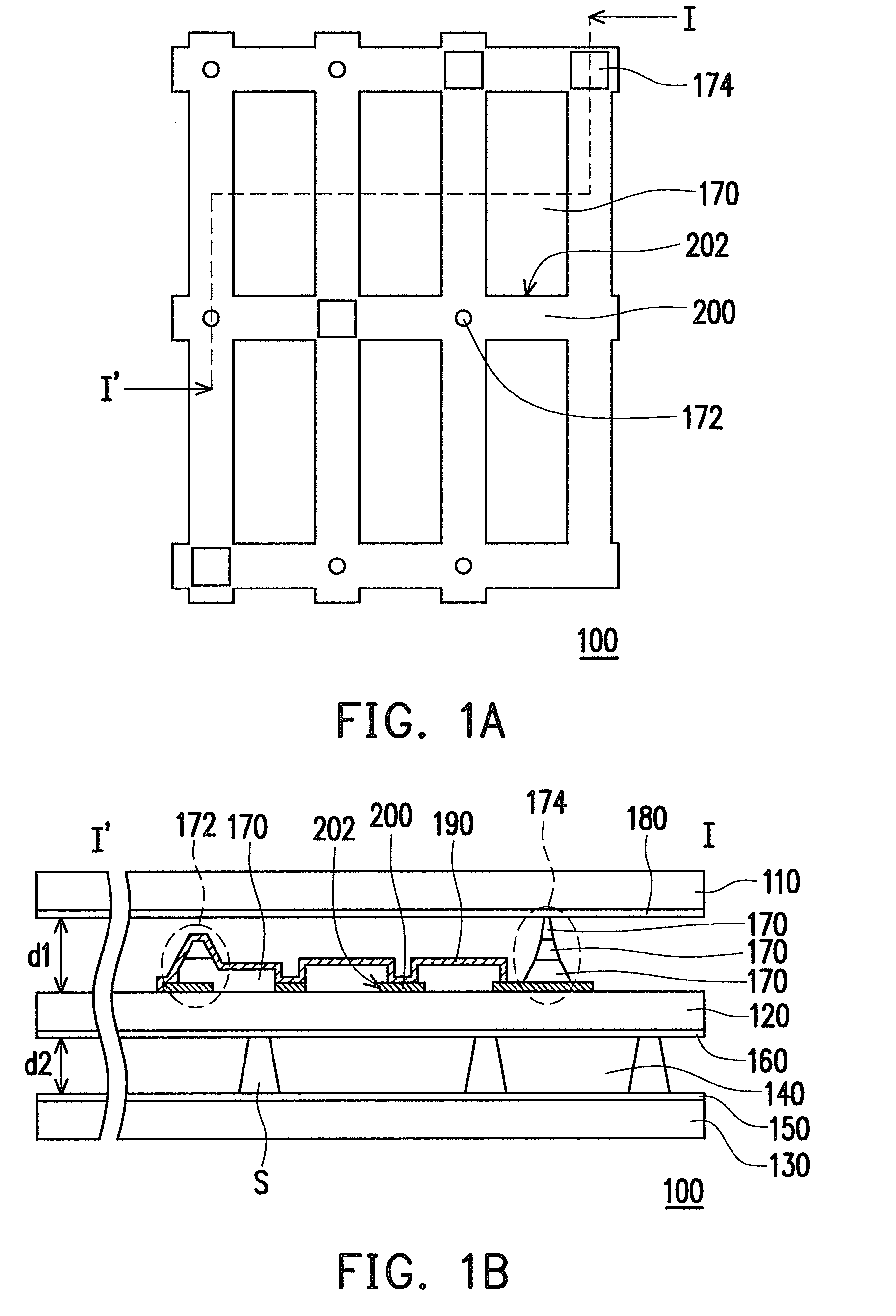

Touch display panel

ActiveUS8054297B2Manufacturing process is complicatedSimple manufacturing processInput/output processes for data processingColor gelPixel array

A touch display panel includes a first substrate, a second substrate, a third substrate, a liquid crystal layer disposed between the second and the third substrates, a pixel array disposed between the liquid crystal layer and the third substrate, an opposite electrode, color filter patterns, a first sensing electrode, and a second sensing electrode. The first, the second, and the third substrates are disposed in parallel. The color filter patterns and the opposite electrode that are disposed between the liquid crystal layer and the second substrate are respectively disposed on opposite sides of the second substrate. Some color filter patterns are piled to form touch points. The first sensing electrode on the first substrate faces the second substrate. The second sensing electrode covers the touch points and some color filter patterns. A height of the touch points is less than a gap between the first and the second substrates.

Owner:CHUNGHWA PICTURE TUBES LTD

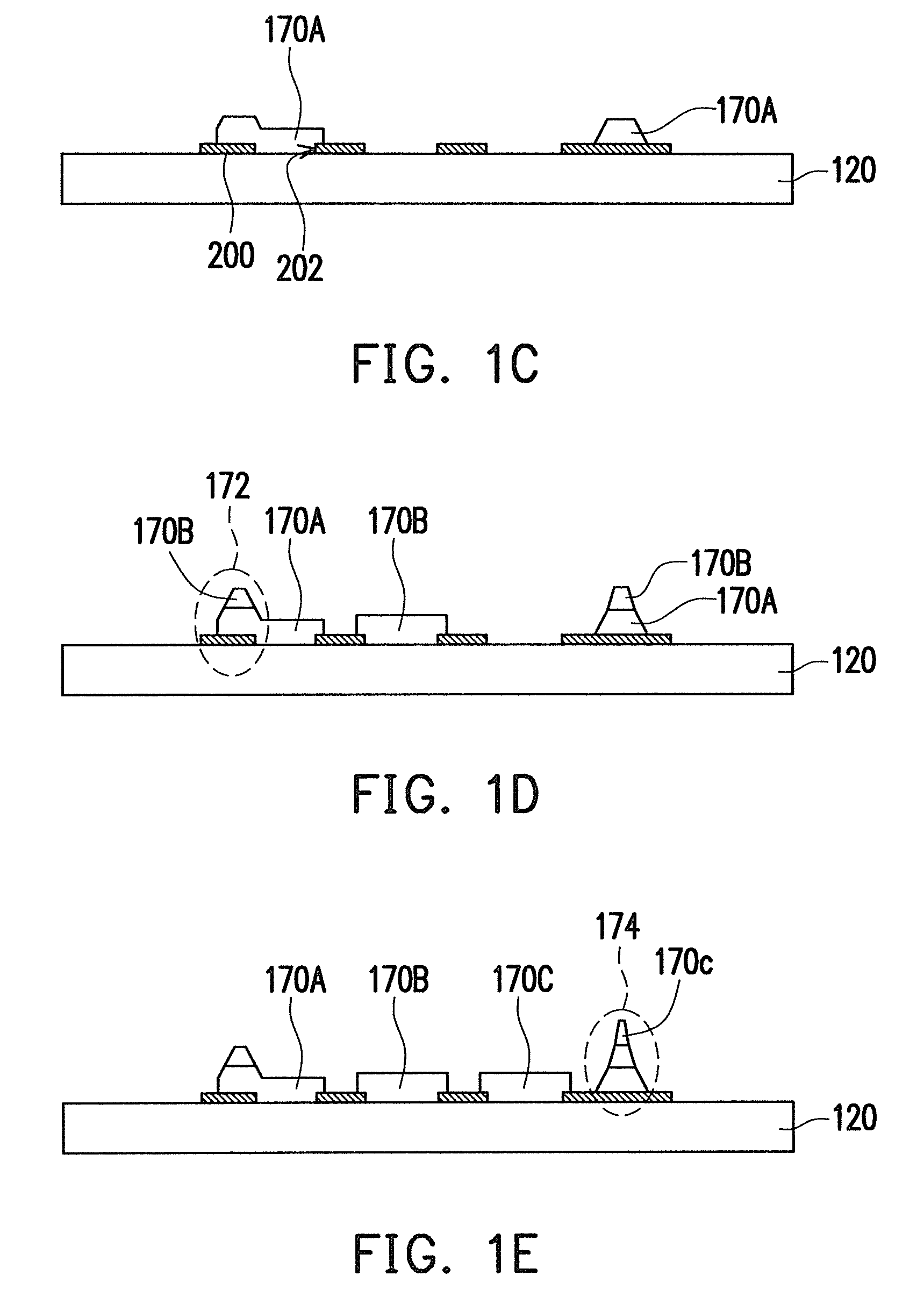

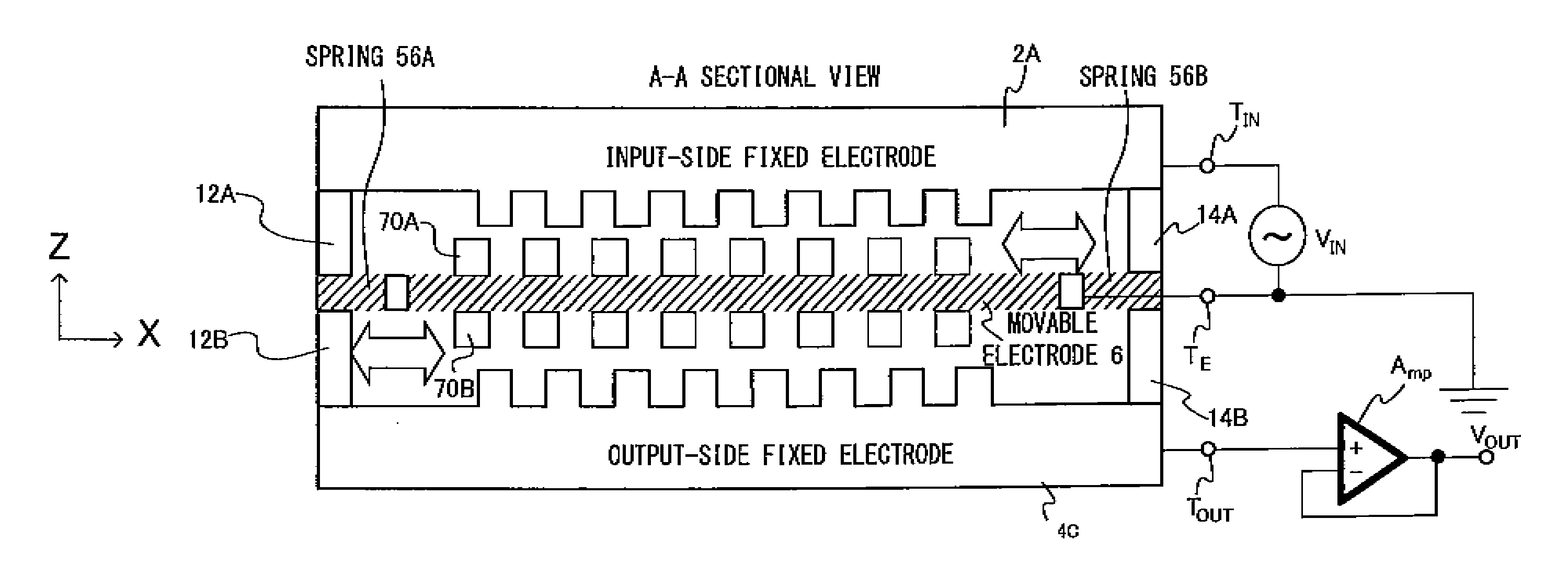

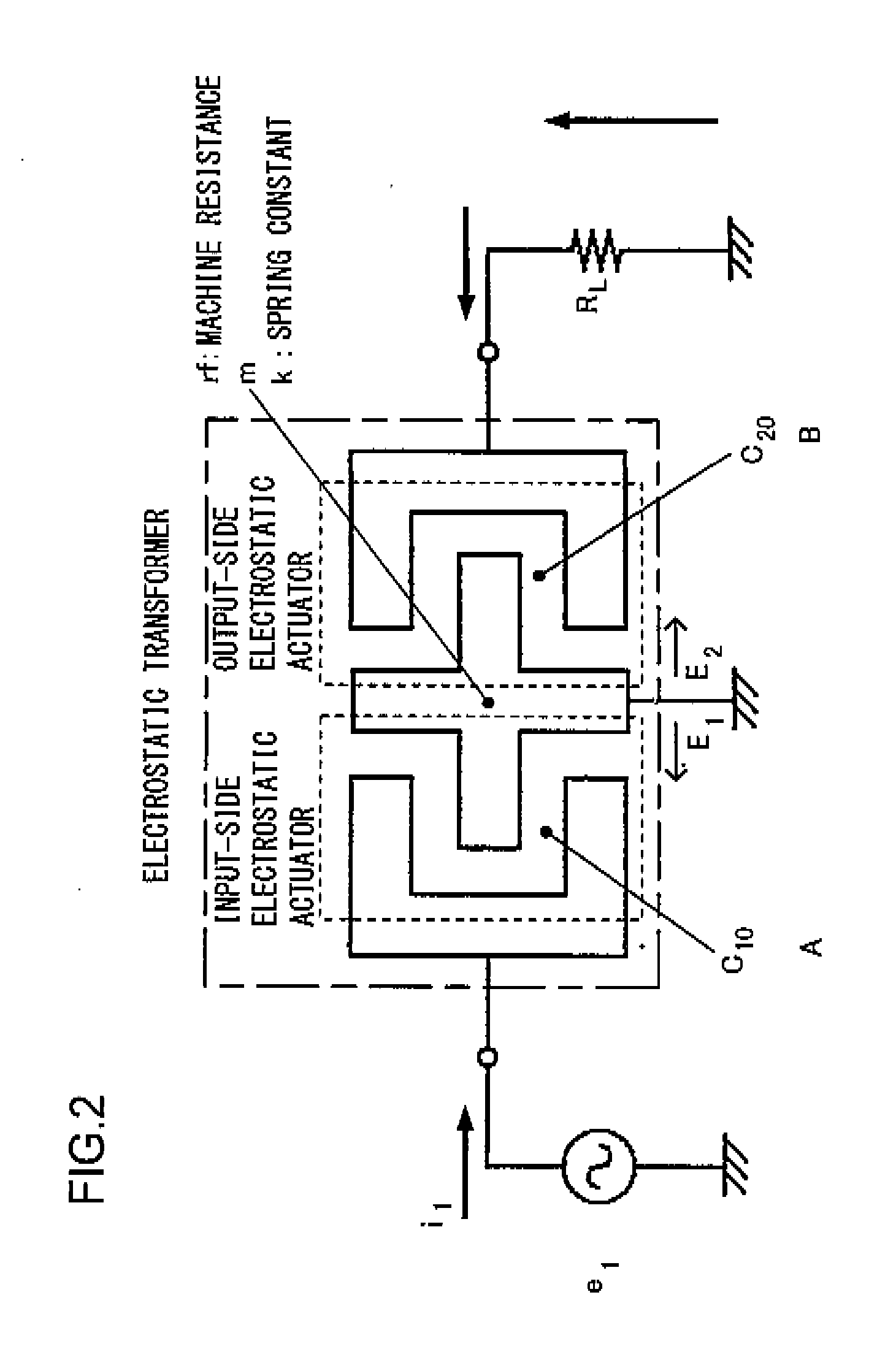

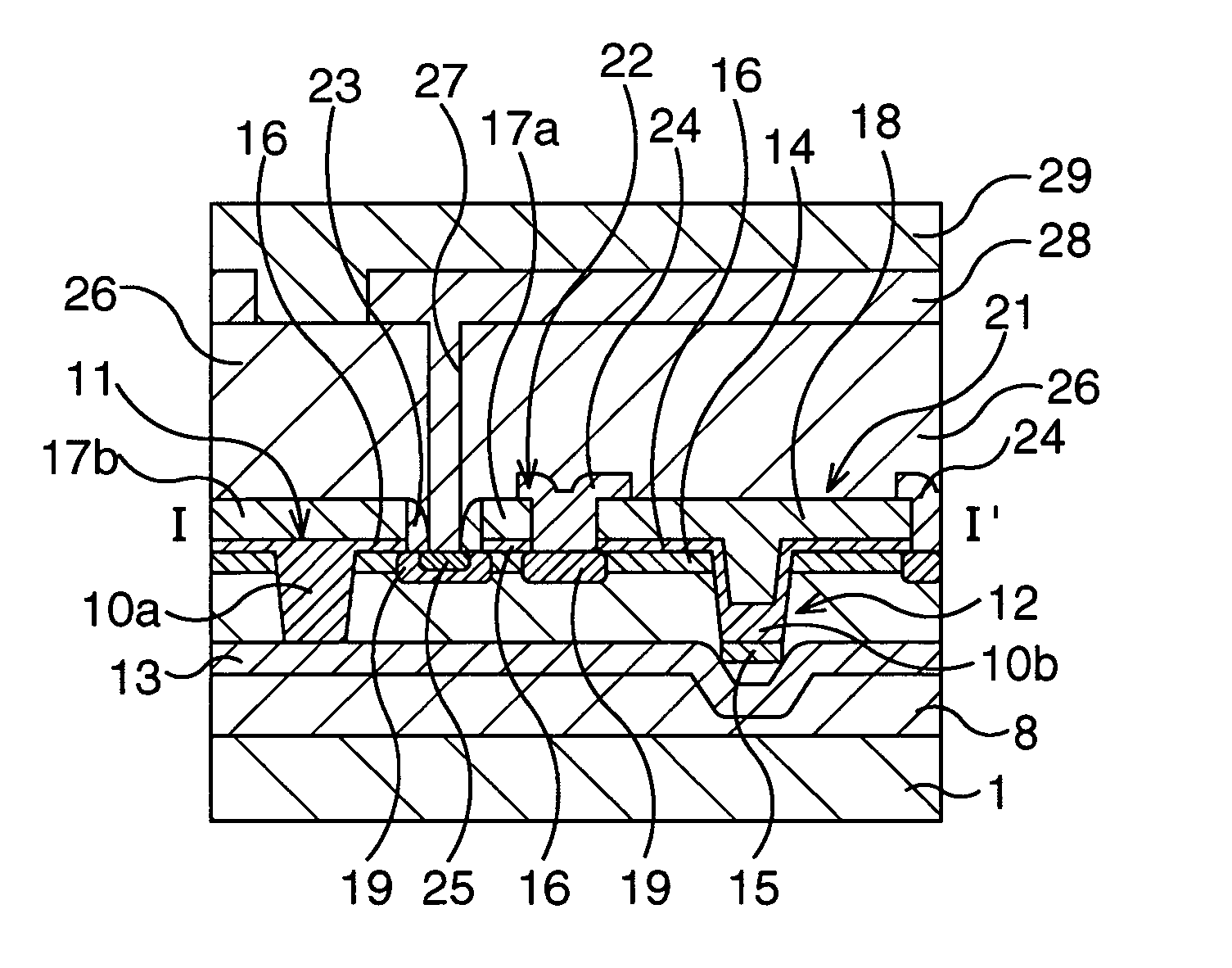

Electrostatic Transformer

InactiveUS20140346923A1Manufacturing process is complicatedIncrease manufacturing costConversion without intermediate conversion to dcInfluence generatorsEngineeringElectrostatic actuator

An electrostatic transformer includes: a first fixed electrode; a second fixed electrode; a movable electrode displaceably supported by a flexible member within a space between the first fixed electrode and the second fixed electrode; and permanently charged films disposed on electrode surfaces of the movable electrode. And: an AC output voltage corresponding to a change in an electric charge induced at the second fixed electrode by displacing the movable electrode in response to an AC input voltage applied between the first fixed electrode and the movable electrode is extracted; and a ratio of the AC input voltage and the AC output voltage is determined based upon a ratio of an electromechanical coupling factor at an input-side electrostatic actuator, configured with the first fixed electrode and the movable electrode, and an electromechanical coupling factor at an output-side electrostatic actuator, configured with the second fixed electrode and the movable electrode.

Owner:AOI ELECTRONICS CO LTD

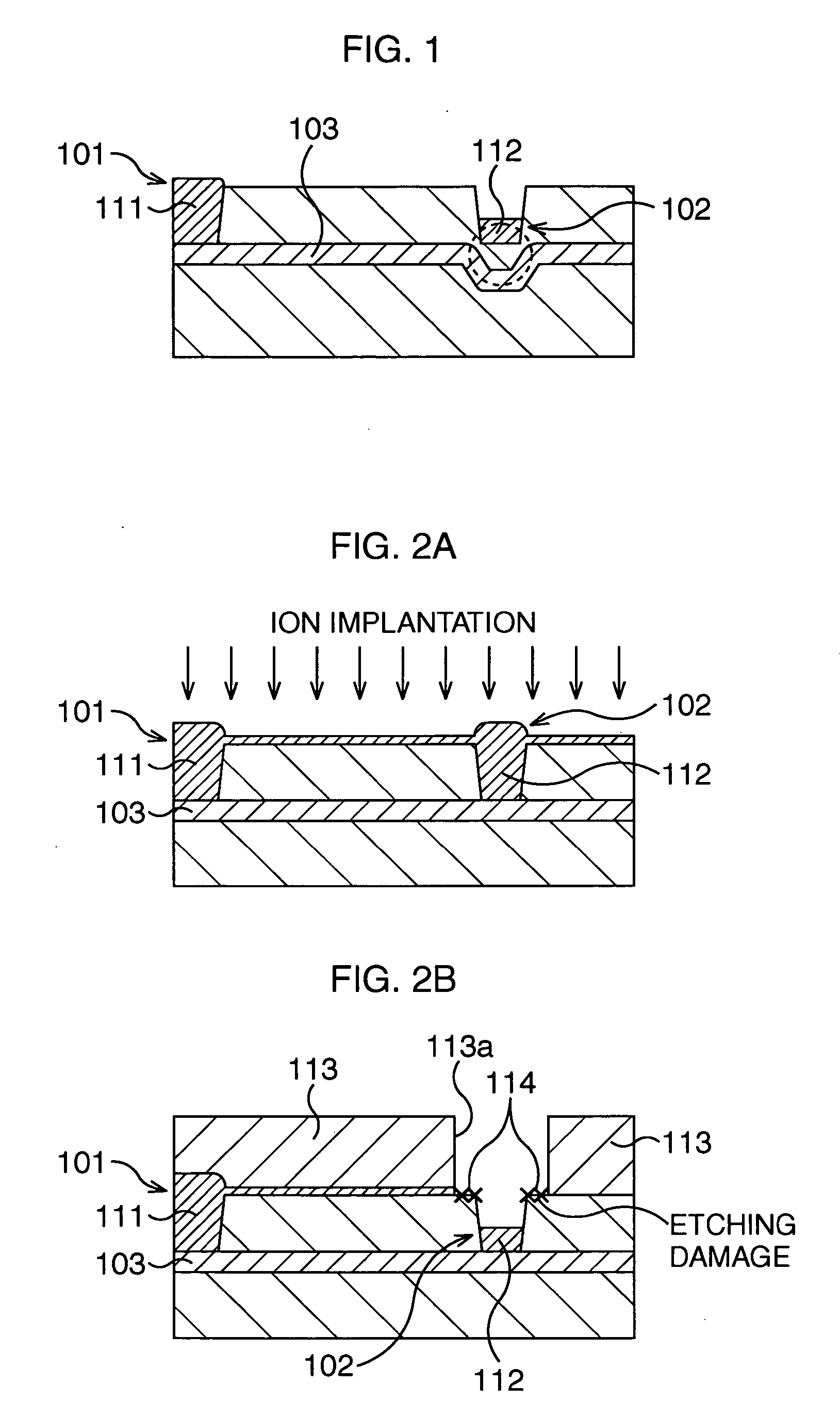

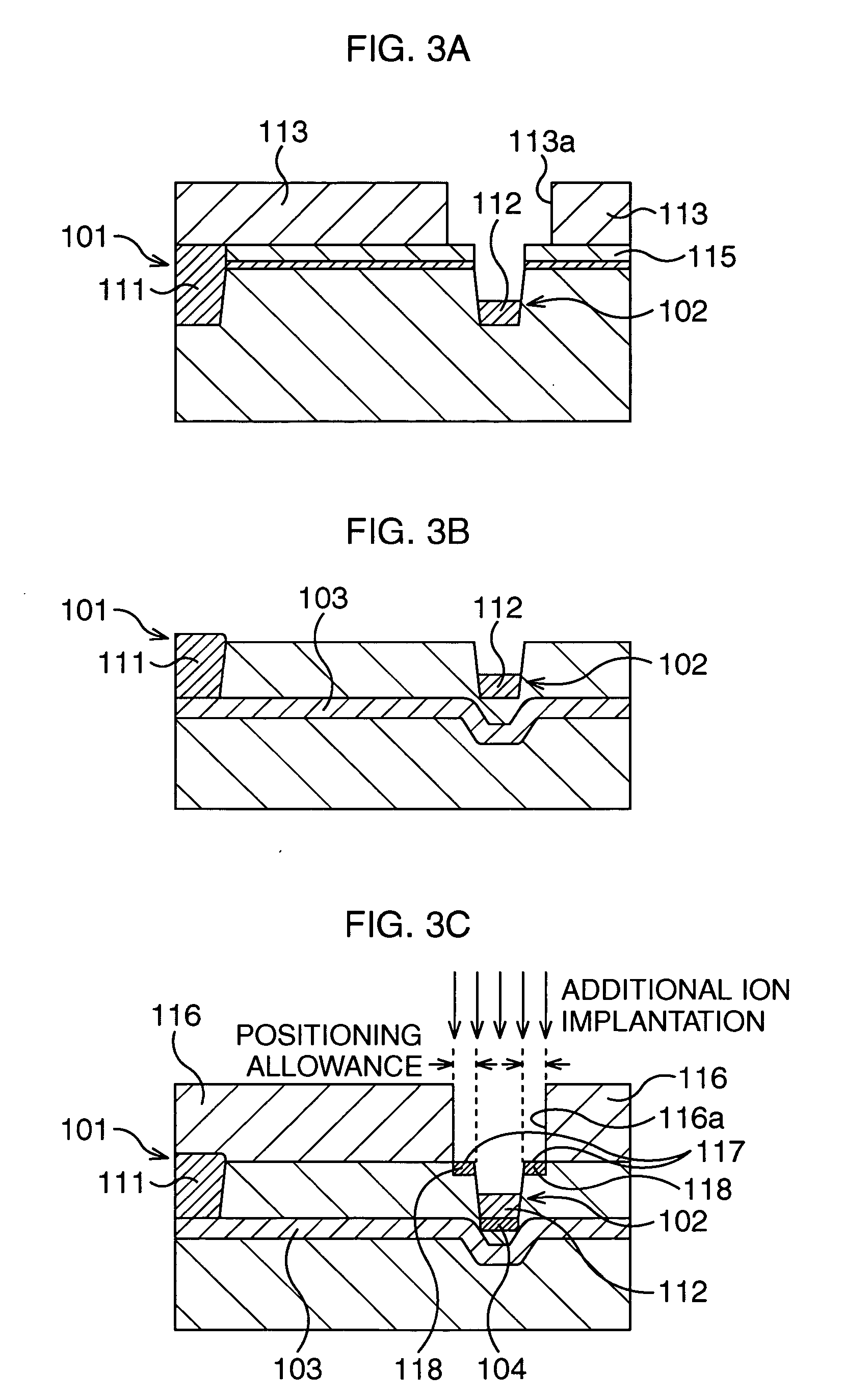

Semiconductor device and manufacturing method thereof

InactiveUS20070164339A1Highly integratedAdditional processing stepsTransistorSolid-state devicesDevice materialIon implantation

A channel stop region is formed immediately under an STI, and thereafter, an ion implantation is performed with conditions in which an impurity is doped into an upper layer portion of an active region, and at the same time, the impurity is also doped into immediately under another STI, and a channel dose region is formed at the upper layer portion of the active region, and another channel stop region is formed immediately under the STI.

Owner:FUJITSU SEMICON LTD +1

Touch element and touch display module

ActiveUS9798406B2Manufacturing process is complicatedLow costInput/output processes for data processingTouch SensesEngineering

Owner:HANNSTOUCH SOLUTION

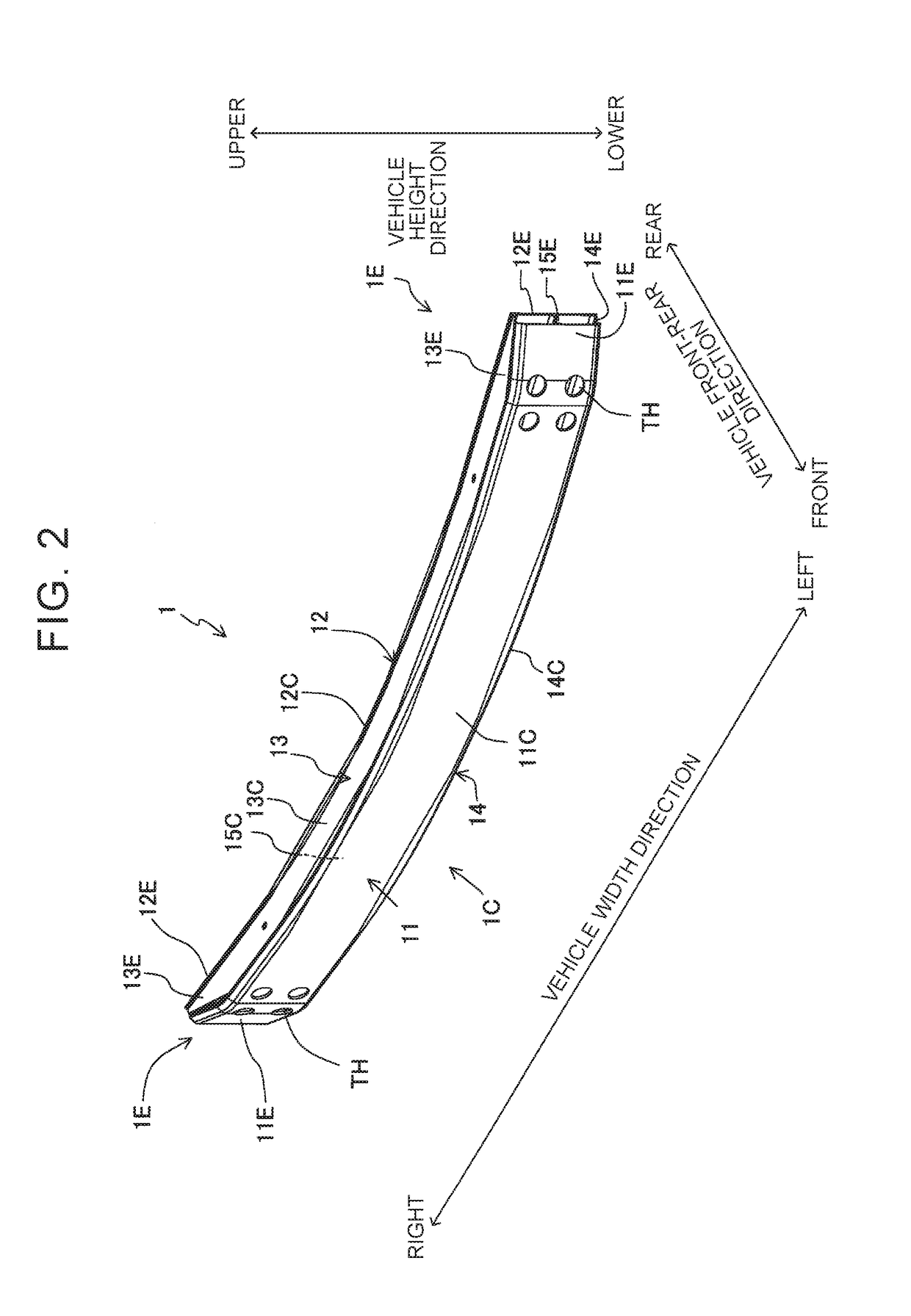

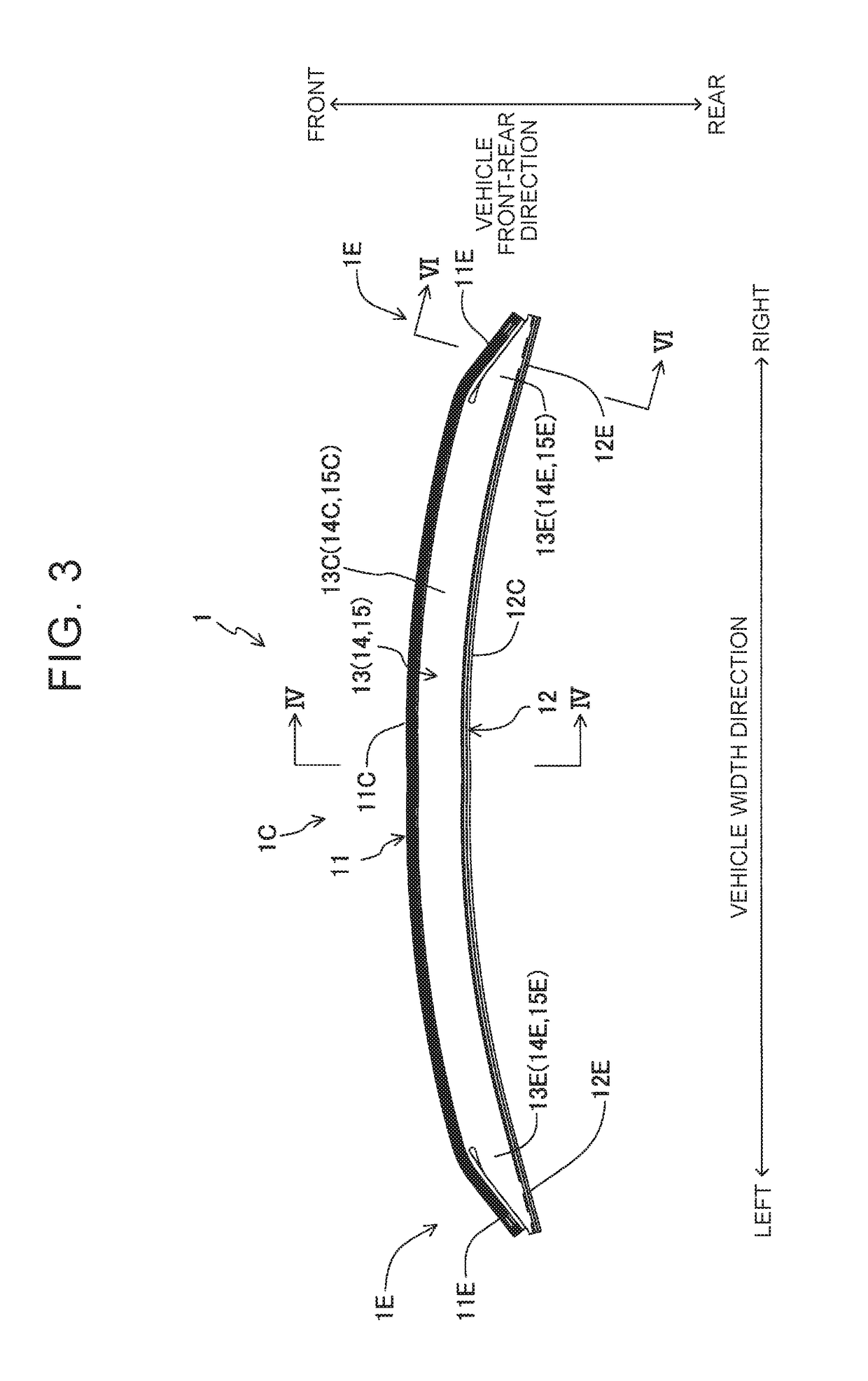

Bumper reinforcement and method of manufacturing bumper reinforcement

ActiveUS20180370469A1Easily brought into surface contact with each otherManufacturing process is complicatedBumpersEngineeringMechanical engineering

Owner:AISIN SEIKI KK +2

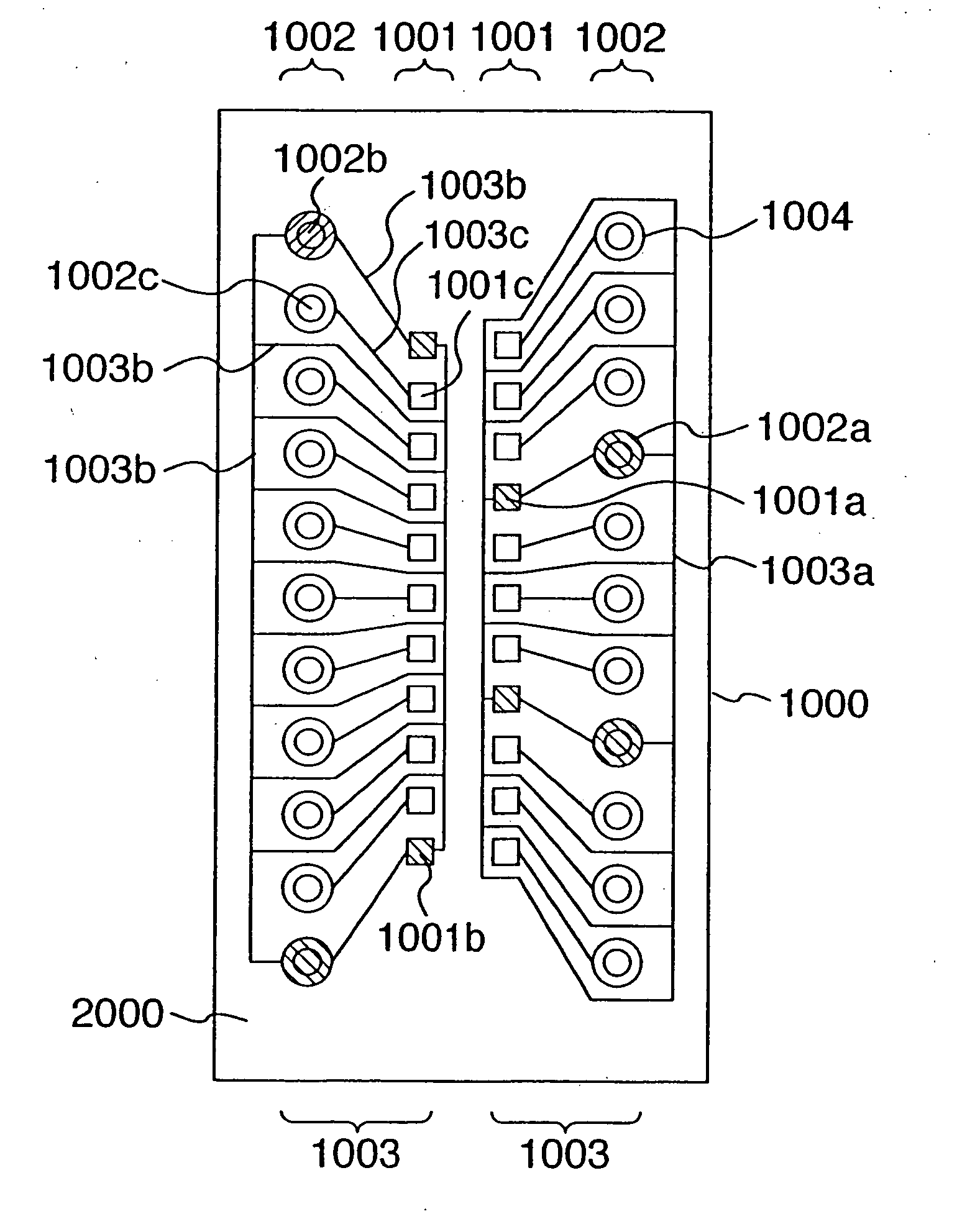

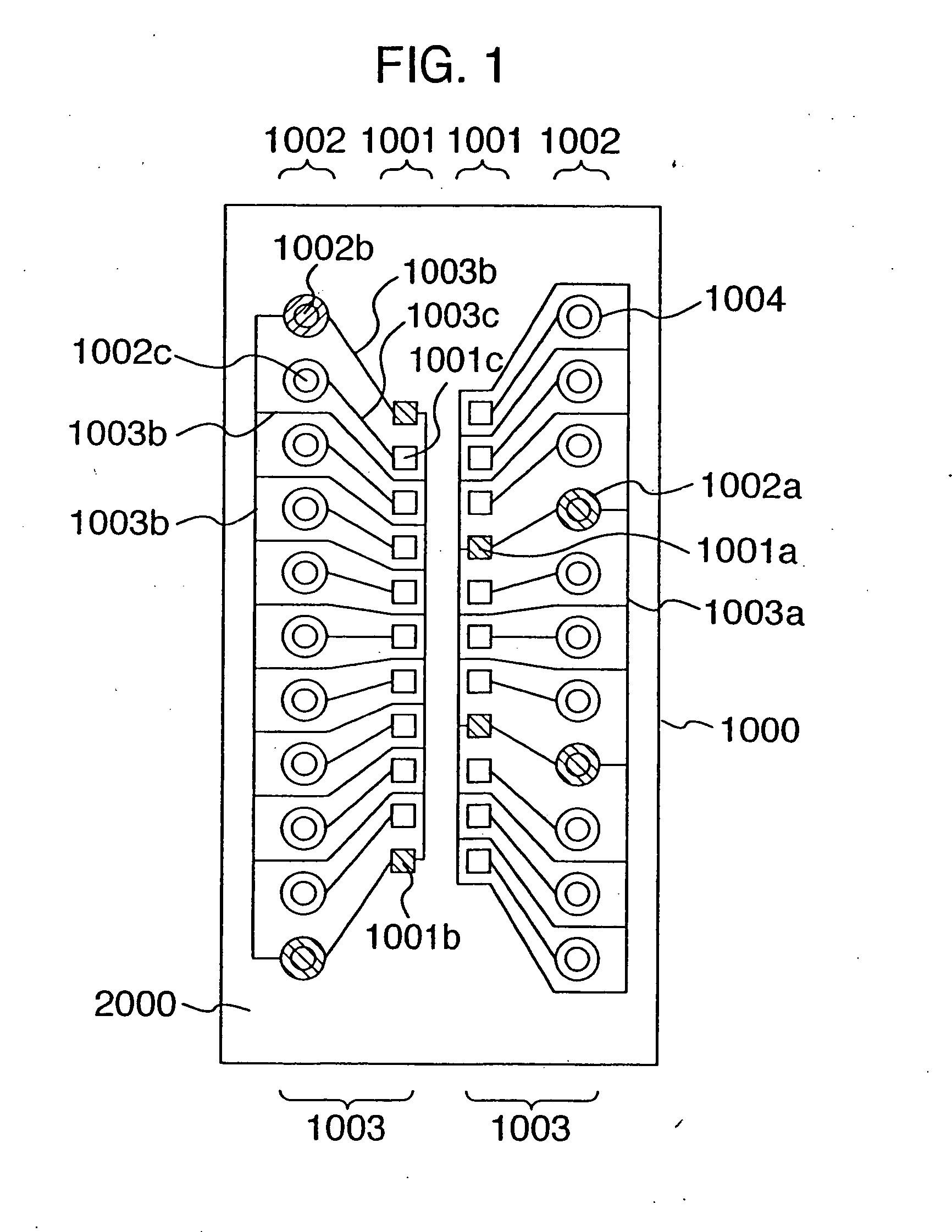

Semiconductor device

InactiveUS20050006751A1High densityHighly integratedSemiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

A semiconductor device including a semiconductor element having external terminals at a first level and external electrodes at a second level, higher than the first level. The external terminals include power terminals, ground terminals and signal terminals formed on a main surface of the semiconductor element. The external electrodes include power electrodes connected to the power terminals via power connecting sections, ground electrodes connected to the ground terminals via ground connecting sections and signal electrodes connected to the signal terminals via signal connecting sections. One of the signal terminals, signal electrodes and corresponding signal connecting sections are surrounded by either the power connecting sections connecting the power terminals and power electrodes or by the ground connection sections connecting the ground terminals and ground electrodes.

Owner:RENESAS ELECTRONICS CORP

Display

InactiveUS20060233007A1Easy to set upIncrease supplyColor signal processing circuitsCathode-ray tube indicatorsShift registerDisplay device

A display capable of inhibiting a logic composition circuit from outputting a signal to a gate line or a drain line at unintentional timing is obtained. In this display, at least either a first shift register circuit portion or a second shift register circuit portion includes a reset transistor for resetting the voltage supply source of a node outputting a first shift signal or a second shift signal to a second voltage supply source not turning on transistors of a logic composition circuit portion in response to an output signal received from a shift register circuit portion precedent thereto by at least two stages with respect to a scanning direction.

Owner:JAPAN DISPLAY WEST

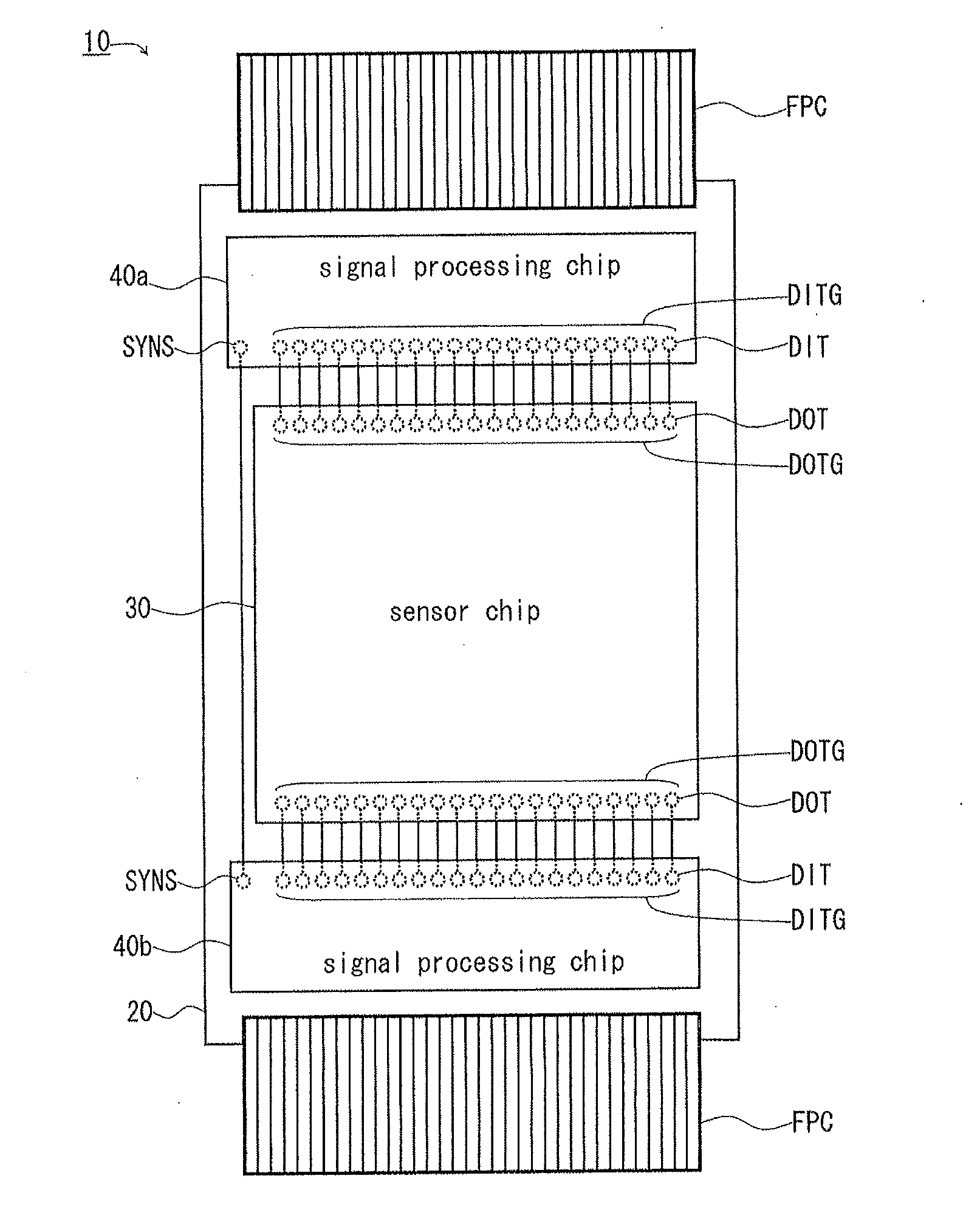

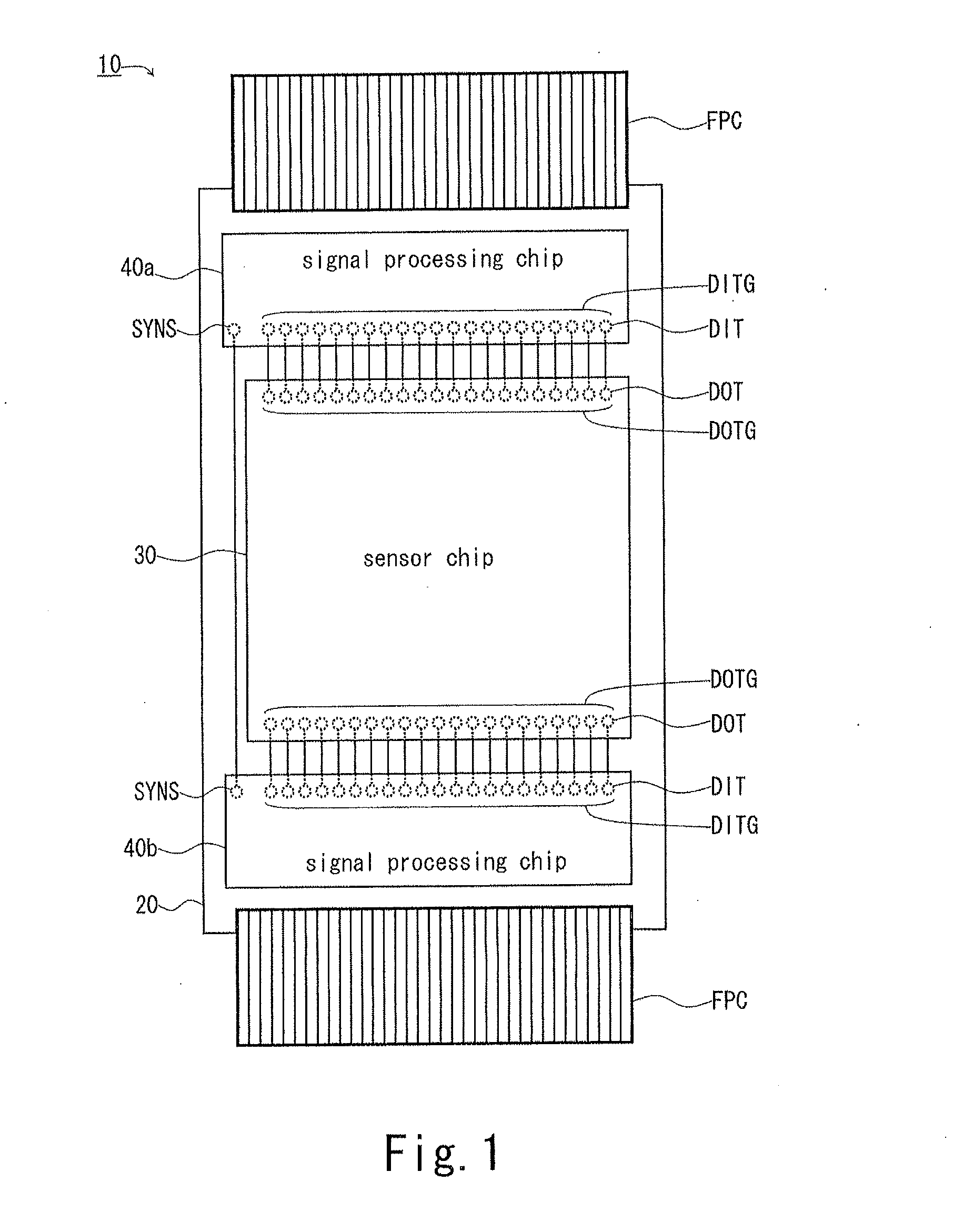

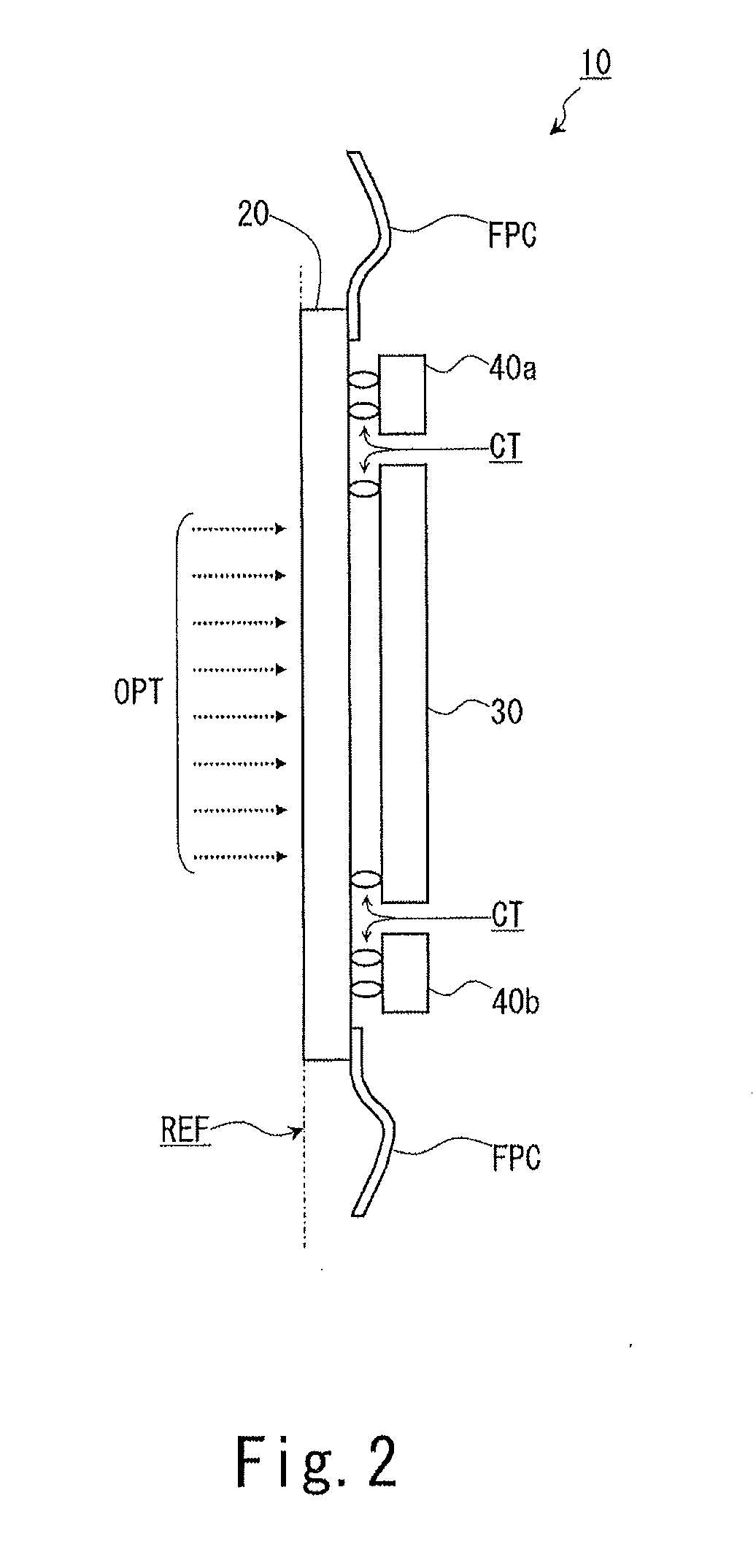

Imaging device

ActiveUS20160065876A1Improve performanceSpeeding up signal processingTelevision system detailsTelevision system scanning detailsAnalog signalComputer science

An imaging device has a sensor chip and a signal processing chip. The sensor chip includes a pixel array in which a plurality of pixels are arranged in a 2-dimensional matrix and a data output terminal group made up of a plurality of data output terminals which output analog signals of pixels for each pixel column of the pixel array. The signal processing chip includes a data input terminal group electrically coupled to the data output terminal group, a plurality of A / D converters which convert analog signals of pixels received by the data input terminal group into digital signals for each pixel column of the pixel array, and a control unit which controls operation of the plurality of A / D converters.

Owner:NIKON CORP