Semiconductor integrated circuit, method of manufacturing semiconductor integrated circuit, charge pump circuit, layout designing apparatus, and layout designing program

a semiconductor integrated circuit and integrated circuit technology, applied in the field of semiconductor integrated circuits, can solve the problems of complex layout of transistors to transistors, increased layout area, and inability to easily change layouts, etc., and achieve the effect of increasing display area, low degree of design freedom, and increasing layout width

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

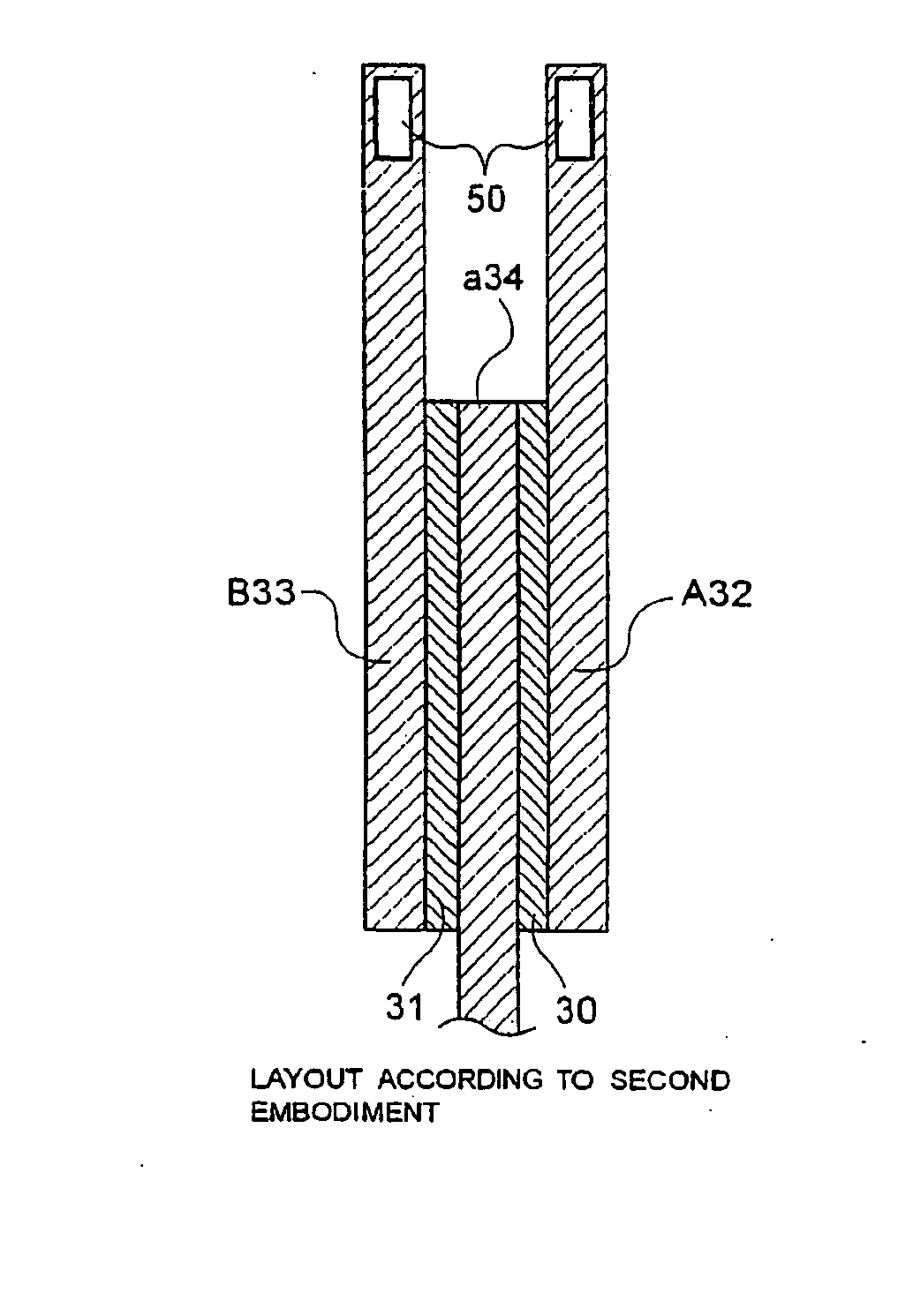

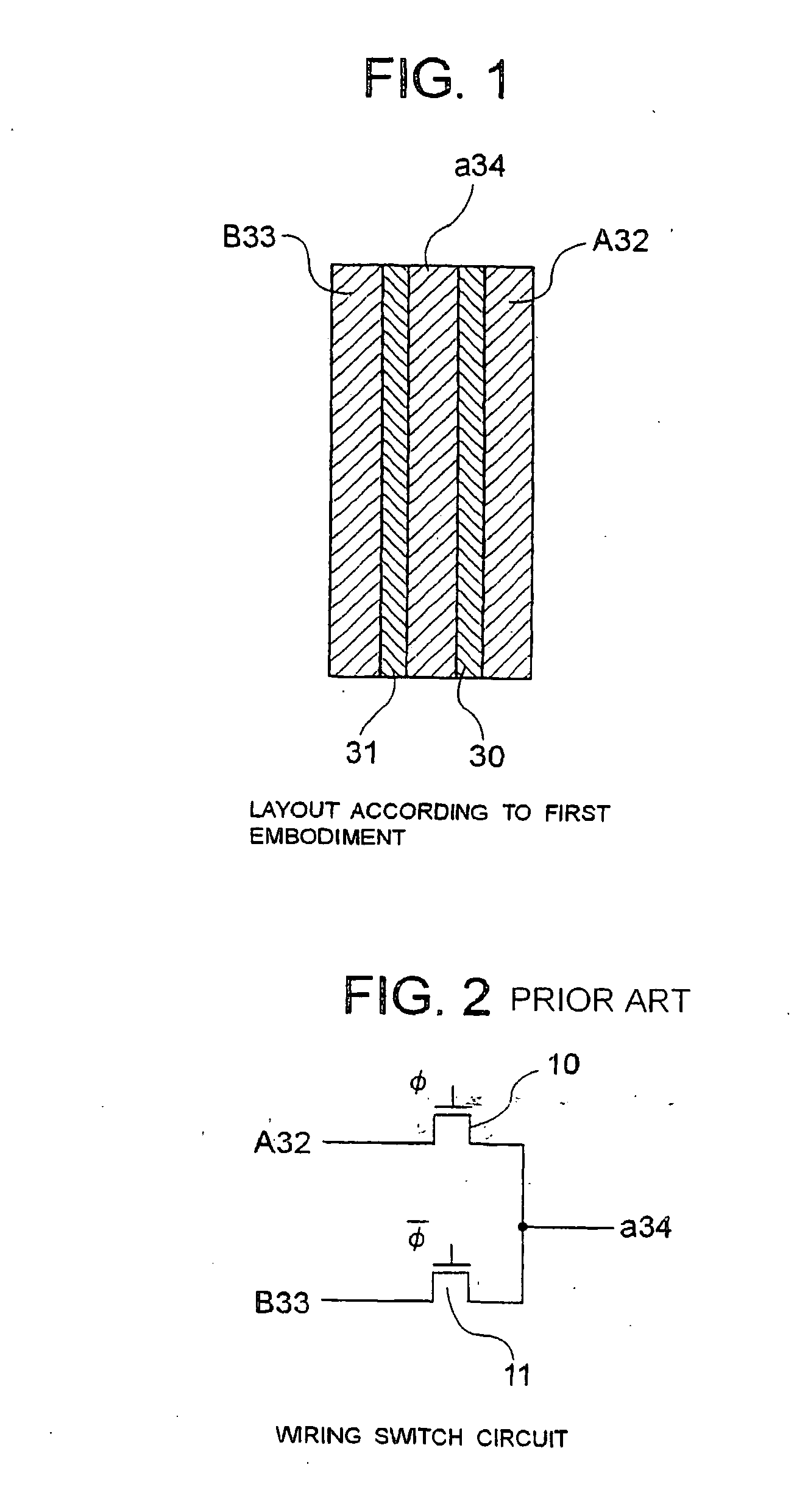

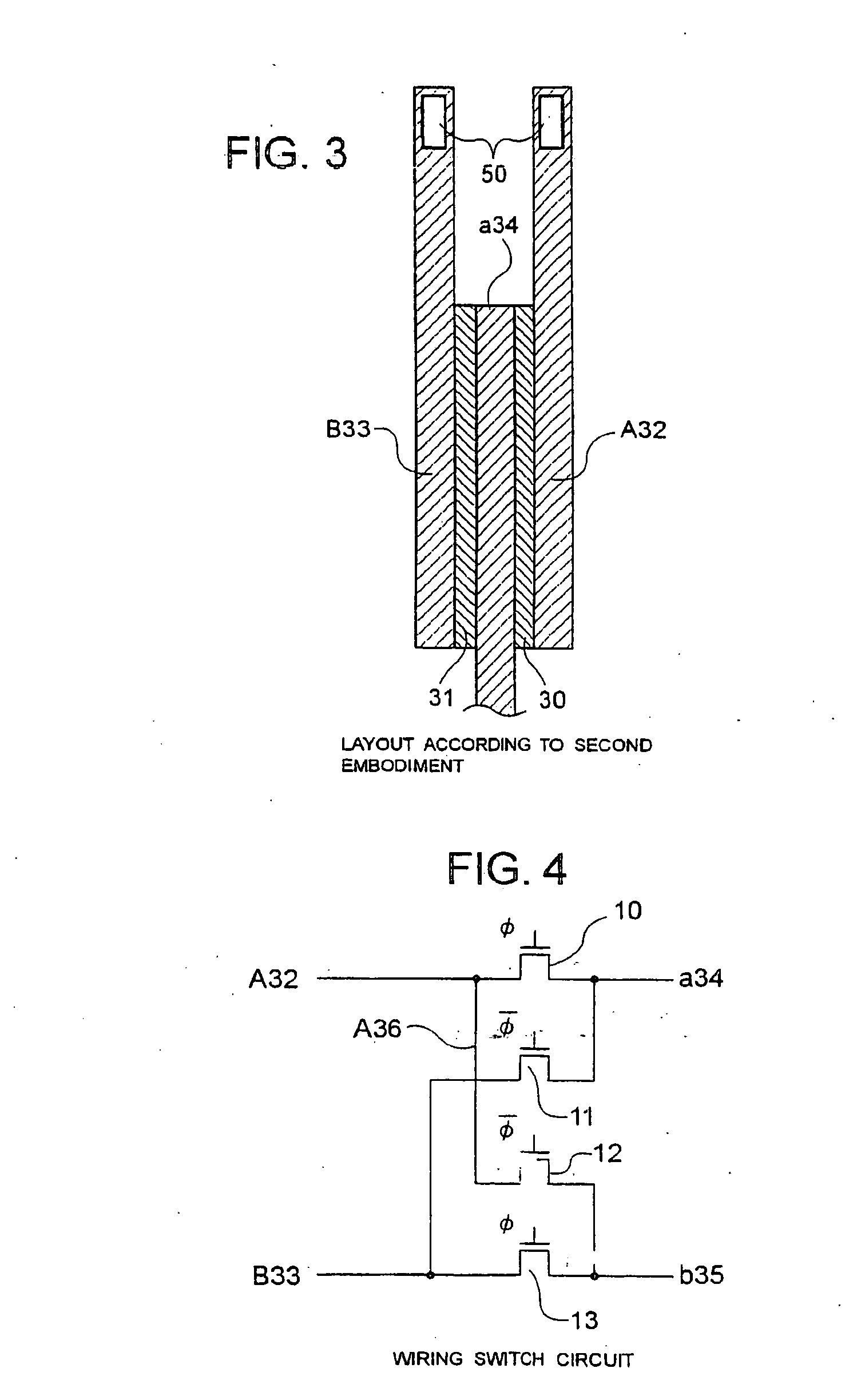

[0072] Embodiments of the present invention will be described in detail with reference to the accompanying drawings. FIG. 1 shows a layout which represents the present invention. This layout corresponds to the circuit shown in FIG. 2 as a circuit for switching the connection of a power supply line a34 between power supply lines A32 and B33. The power supply lines A32, a34, and B33 are placed in the above-mentioned order, and transistors 10 and 11 are placed in the gaps between the power supply lines A32, a34, and B33. In the layout shown in FIG. 1, each transistor has one gate electrode. The gate electrode of the transistor 10 is indicated by 30 and the gate electrode of the transistor 11 is indicated by 31. The gate electrodes 30 and 31 are placed on the opposite sides of the power supply line a34, and each gate electrode is formed by a gate layer. The power supply lines are each formed by a first metal layer and are electrically connected to active regions in the bodies of the tra...

second embodiment

[0074]FIG. 3 is a diagram showing a layout which represents the present invention. In this embodiment, a function for connection to external terminals concentrated on one side is added to the layout shown in FIG. 1. To externally apply potentials to the power supply lines A32 and B33, the power supply lines are extended upward as viewed in the figure in wiring using the first metal layer, thereby enabling connection through external connection terminals 50. The power supply line a34 is extended downward as viewed in the figure as wiring for connection to another internal circuit. This layout is characterized by avoiding an increase in width of the circuit layout even though wiring extensions are made.

third embodiment

[0075]FIG. 5 is a diagram showing a layout which represents the present invention. This layout corresponds to a wiring switching circuit shown in FIG. 4. In this circuit, connections are exclusively made between power supply lines A32 and B33 and power supply lines a34 and b35. This circuit operates as described below. When the gate signal φ is high level, the transistors 10 and 13 are in the on state, the power supply lines A32 and a34 are connected to each other, and the power supply lines B33 and the power supply line b35 are also connected to each other. When the gate signal φ is low level, the transistors 11 and 12 are in the on state and reverse connections are established, that is, the power supply lines A32 and b35 are connected to each other, and the power supply lines B33 and the power supply line a34 are connected to each other namely resulting in reverse connection. For example, this circuit is used as a polarity reversing circuit. The power supply lines a34 and b35 are ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More