System for suppressing aliasing interferers in decimating and sub-sampling systems

a decimating and subsampling system technology, applied in the field of data communication, can solve the problems of less noise floor, less unwanted signals, and interference with desired signals, and achieve the effects of reducing noise levels, reducing complexity, cost, and reducing the requirements of anti-aliasing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

Notation Used Throughout

[0029] The following notation is used throughout this document.

TermDefinitionA / DAnalog to DigitalASICApplication Specific Integrated CircuitC / NCarrier to NoiseDSPDigital Signal ProcessorFPGAField Programmable Gate ArrayHDLHardware Description LanguageISMIndustrial Scientific MedicalLOLocal OscillatorLPFLow Pass FilterTDDTime Division Duplex

Detailed Description of the Invention

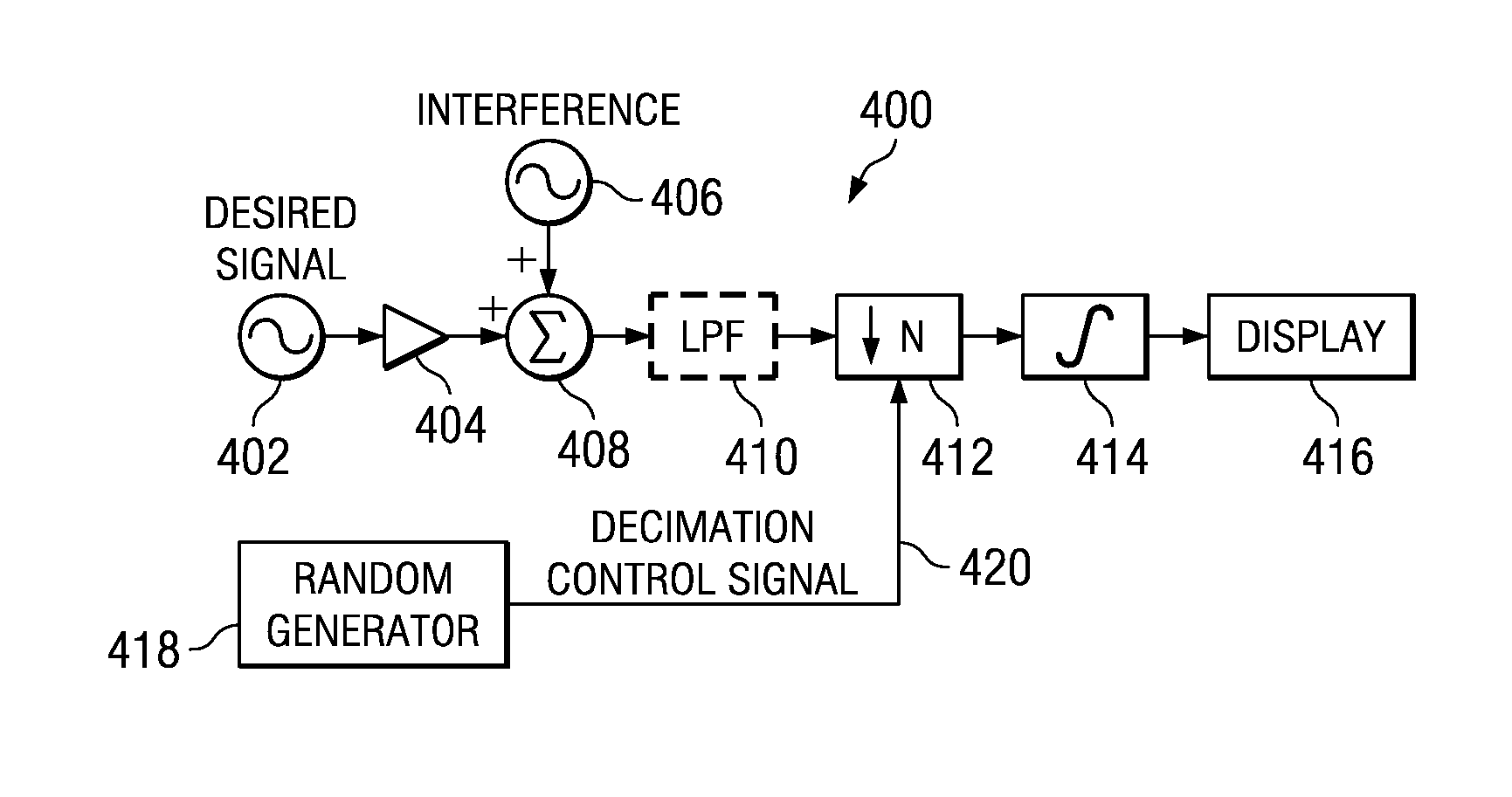

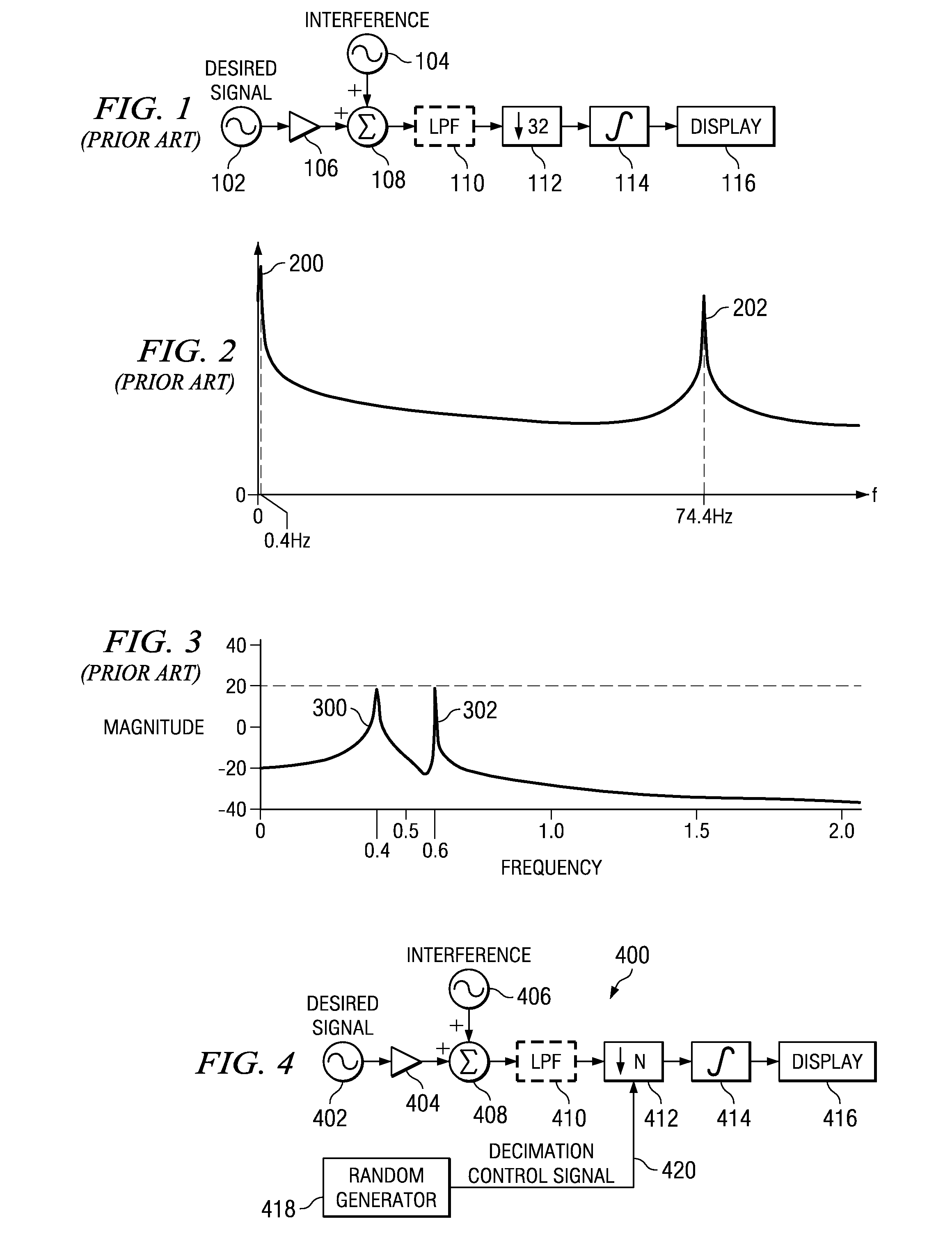

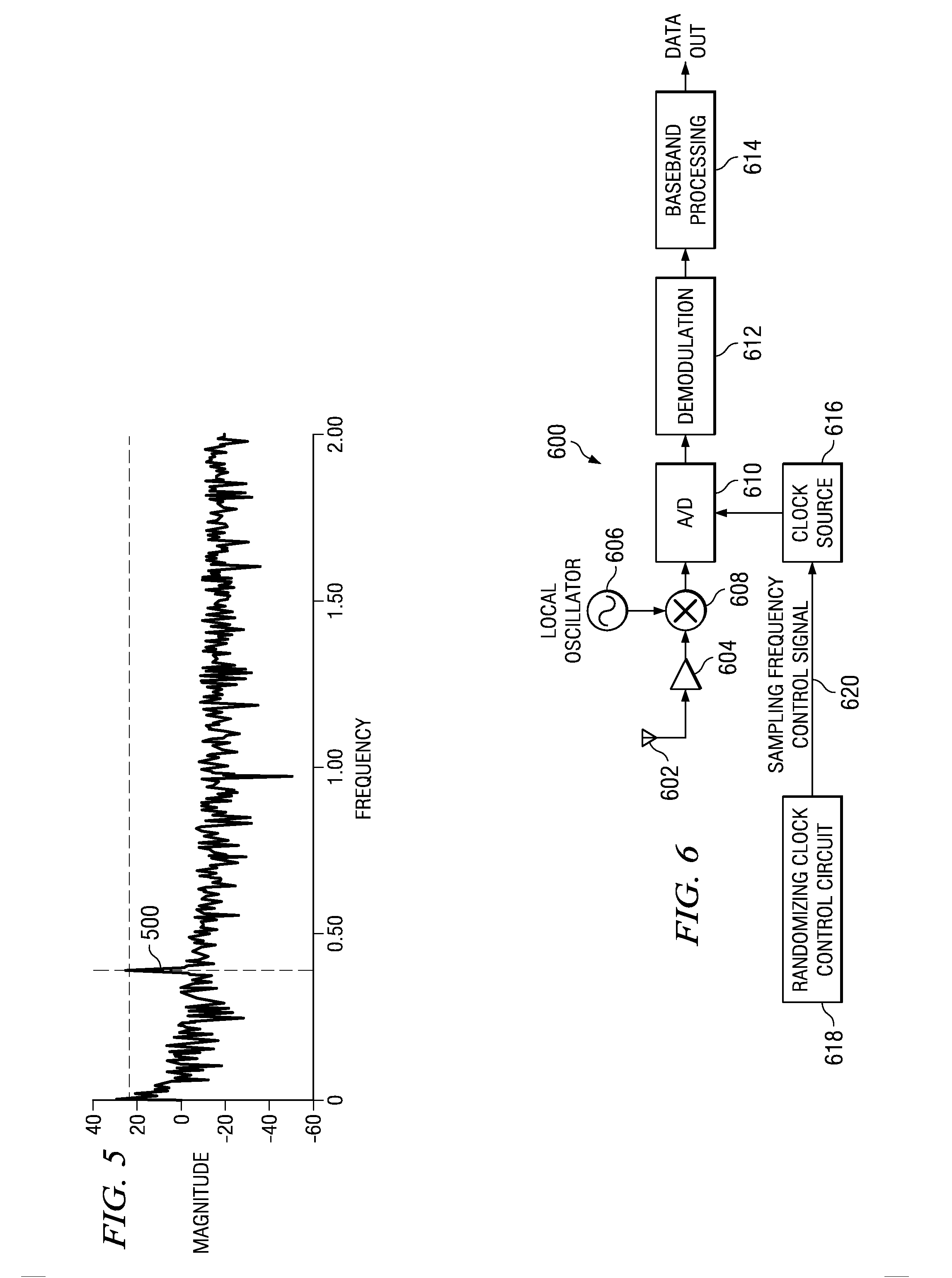

[0030] The present invention is a method and apparatus for suppressing aliasing interferers in decimating and sub-sampling systems. The invention is applicable for use in numerous types of systems and is particular applicable to sub-sampling and sample rate decimating discrete time systems. For example, the invention is applicable in TDM applications such as Bluetooth environments. The invention can be used to eliminate altogether the need for a costly anti-aliasing filter having demanding requirements. Alternatively, the present invention can be used to significantly reduce the requ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More