Plating Device, Plating Method, Semiconductor Device, And Method For Manufacturing Semiconductor Device

a technology of plating solution and semiconductor, which is applied in the manufacture of electrolysis components, tanks, manufacturing tools, etc., can solve the problems of oxidative decomposition of additives in the plating solution, deterioration of the quality of the plating solution, and consumption of more plating solution

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

embodiment 1

[0058]With reference to FIGS. 1 to 6, the following explains an embodiment of the present invention.

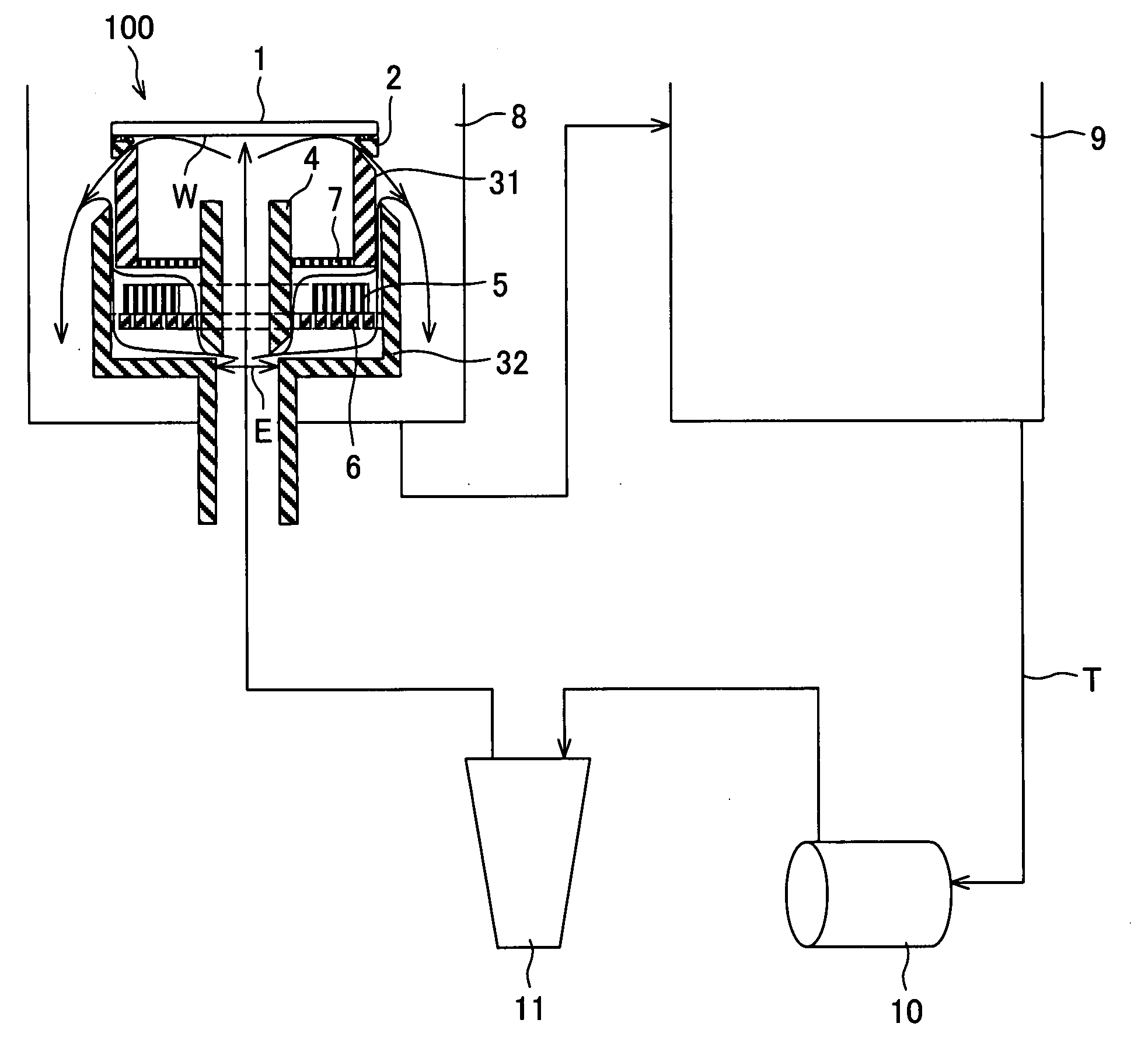

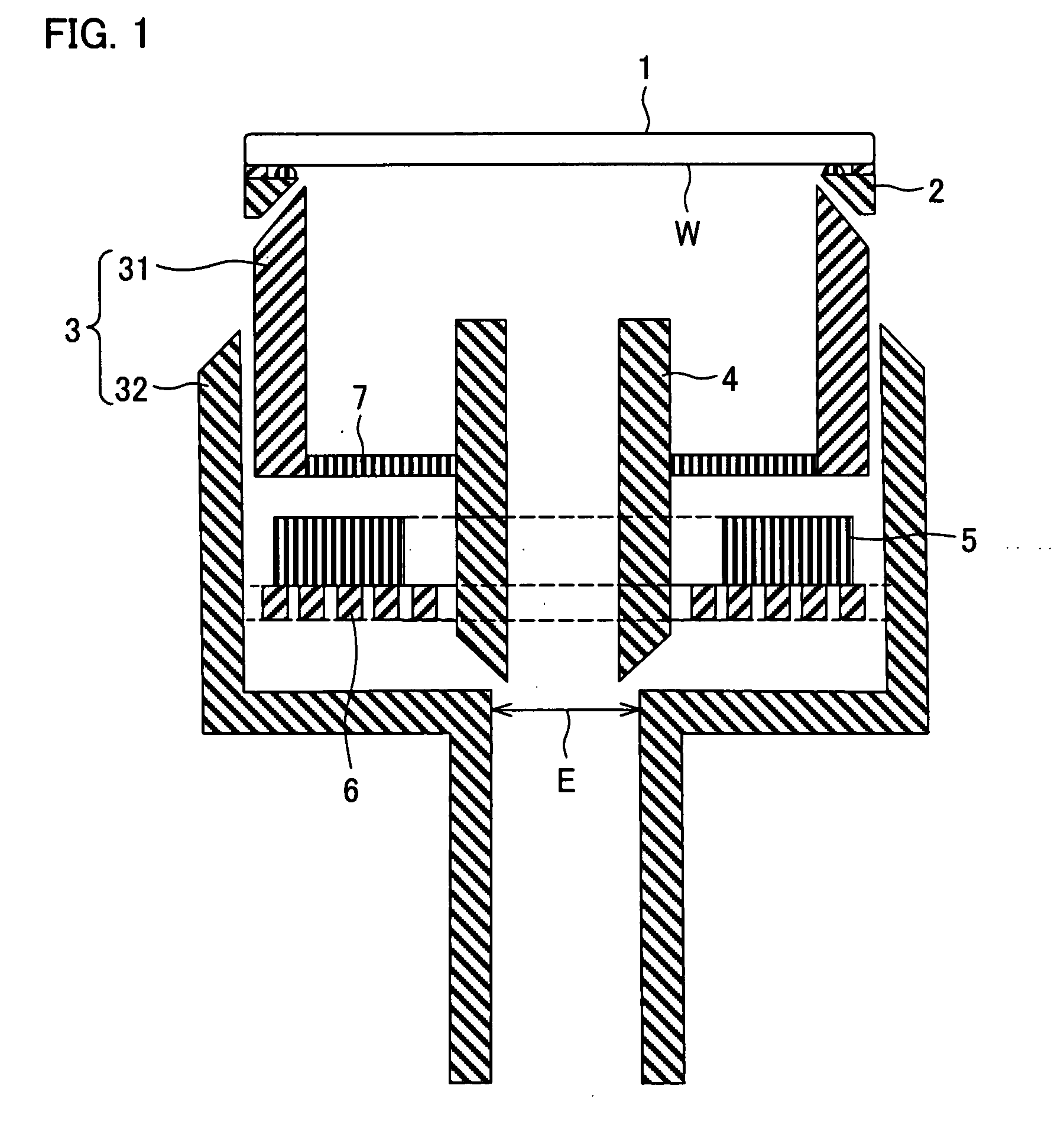

[0059]FIG. 1 is a cross sectional drawing schematically illustrating a structure of a plating tank provided in a plating device of the present embodiment. As shown in FIG. 1, a plating tank 100 includes: a wafer holder 2 for holding a semiconductor wafer (substrate-to-be-plated) 1; a cup 3; a plating solution jetting pipe 4; an anode 5; a supporter 6 for supporting the anode 5; and a partition 7. The cup 3 includes an internal cylinder 31 and an external cylinder 32.

[0060]The internal cylinder (second cylindrical cup) 31 and the external cylinder (first cylindrical cup) 32 are cups each having substantially a cylindrical shape, with its upper end open. The diameter of the internal cylinder 31 is smaller than the diameter of the external cylinder 32. The external cylinder 32 has at its lowest central part a plating solution flowing-in port E through which a plating solution flows in.

[0...

embodiment 2

[0125]With reference to FIGS. 9 to 12, the present embodiment will detail the semiconductor wafer 1 used as a substrate to be plated in Embodiment 1 and a method for manufacturing the substrate. They are examples of a semiconductor device and a method for manufacturing the semiconductor device. FIG. 9 is a drawing schematically illustrating a structure of the semiconductor wafer 1 used in the present embodiment. FIG. 10 is a drawing schematically illustrating a structure of a semiconductor chip 33 formed on the semiconductor wafer 1 after a plating step. FIG. 10(a) is a plan drawing. FIG. 10(b) is a cross sectional drawing.

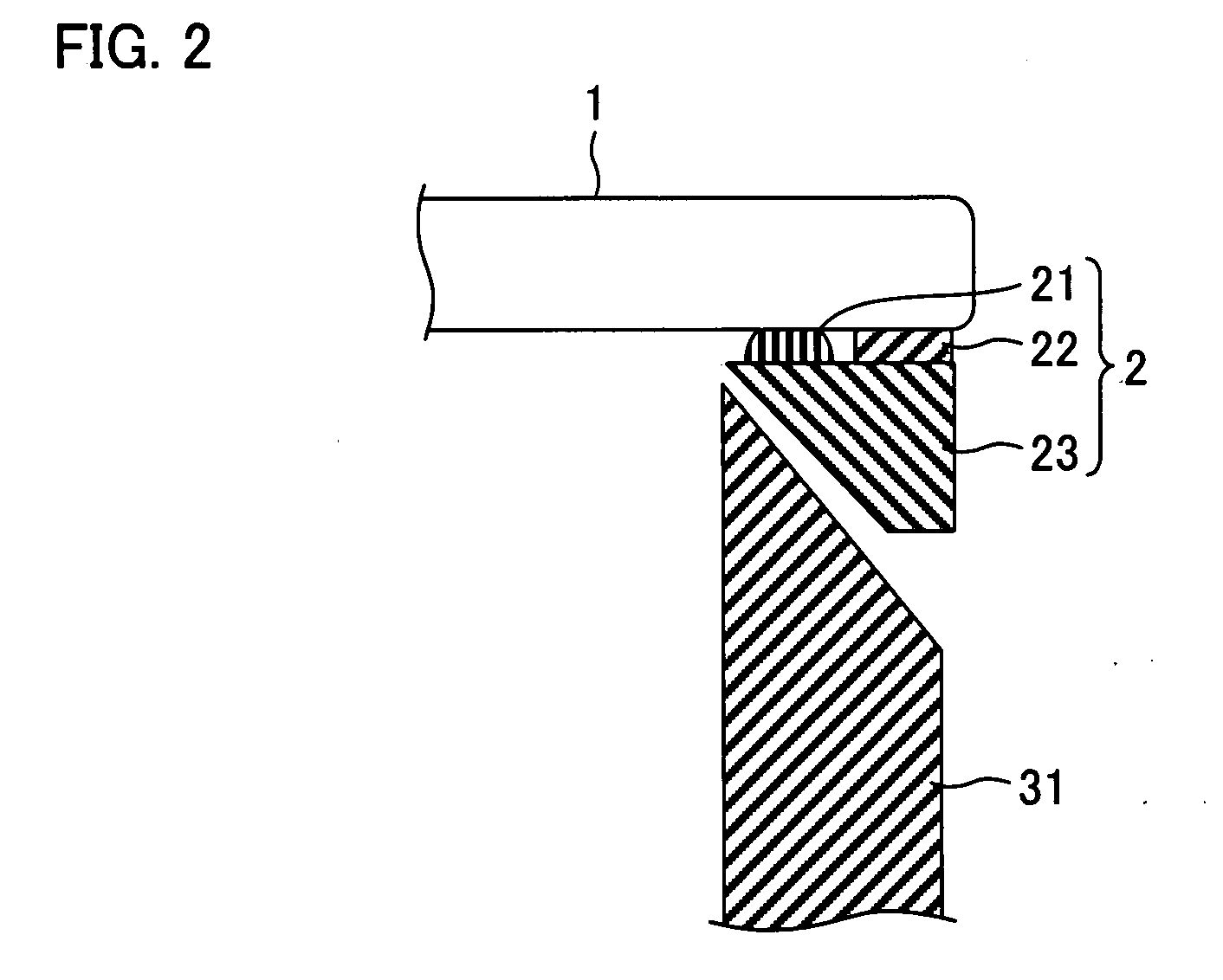

[0126]As illustrated in FIG. 9, a plurality of semiconductor chips 41 are formed on a surface of the semiconductor wafer 1. A contact section 42 is provided on the periphery of the semiconductor wafer 1. The contact section 42 includes a plating seed layer (not shown) which is exposed. The contact section 42 touches the contact member 22 illustrated in FIG. 2.

[012...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Mass | aaaaa | aaaaa |

| Flow rate | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More