Reference Clock Rate Detection for Variable Rate Transceiver Modules

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

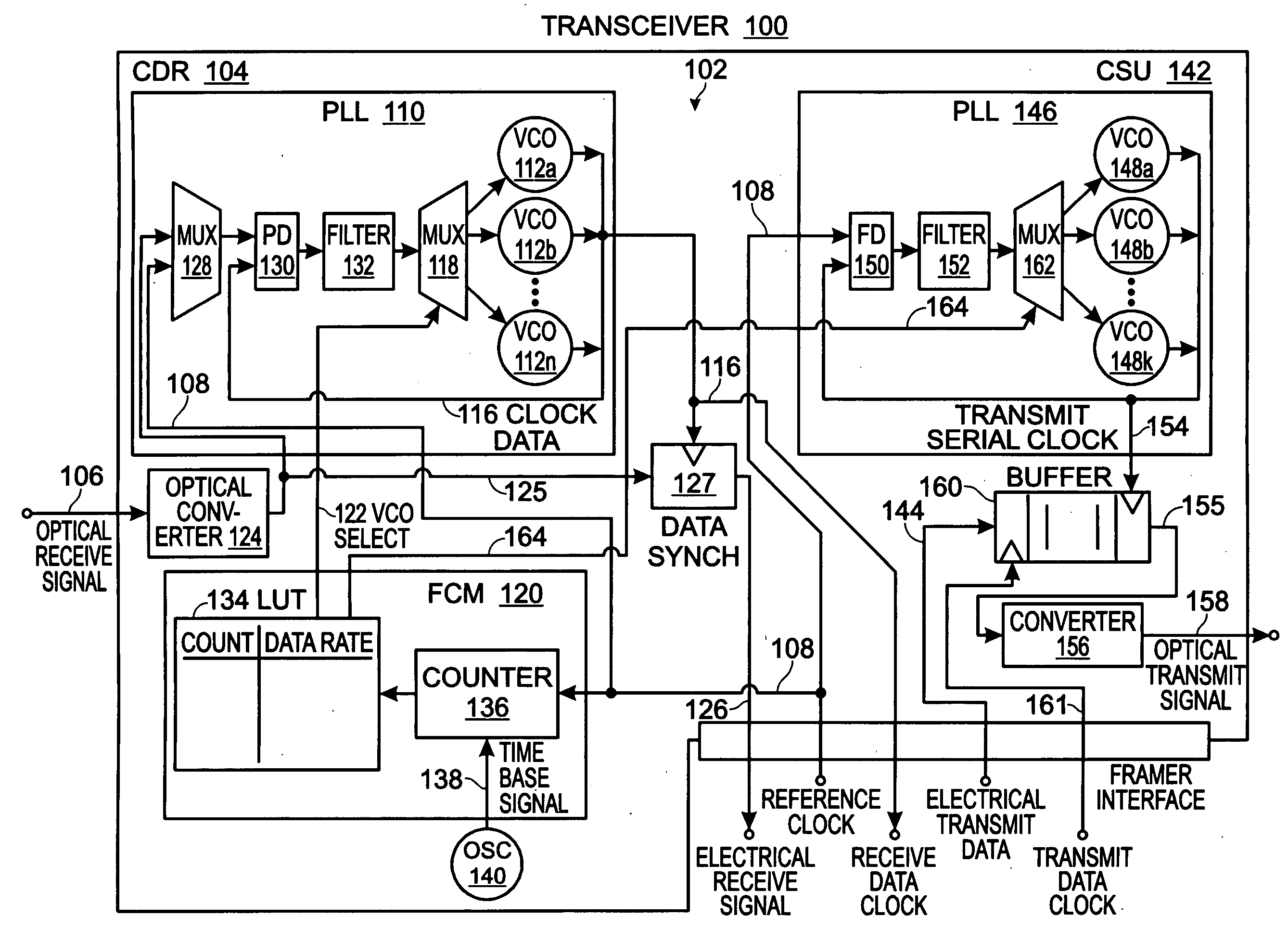

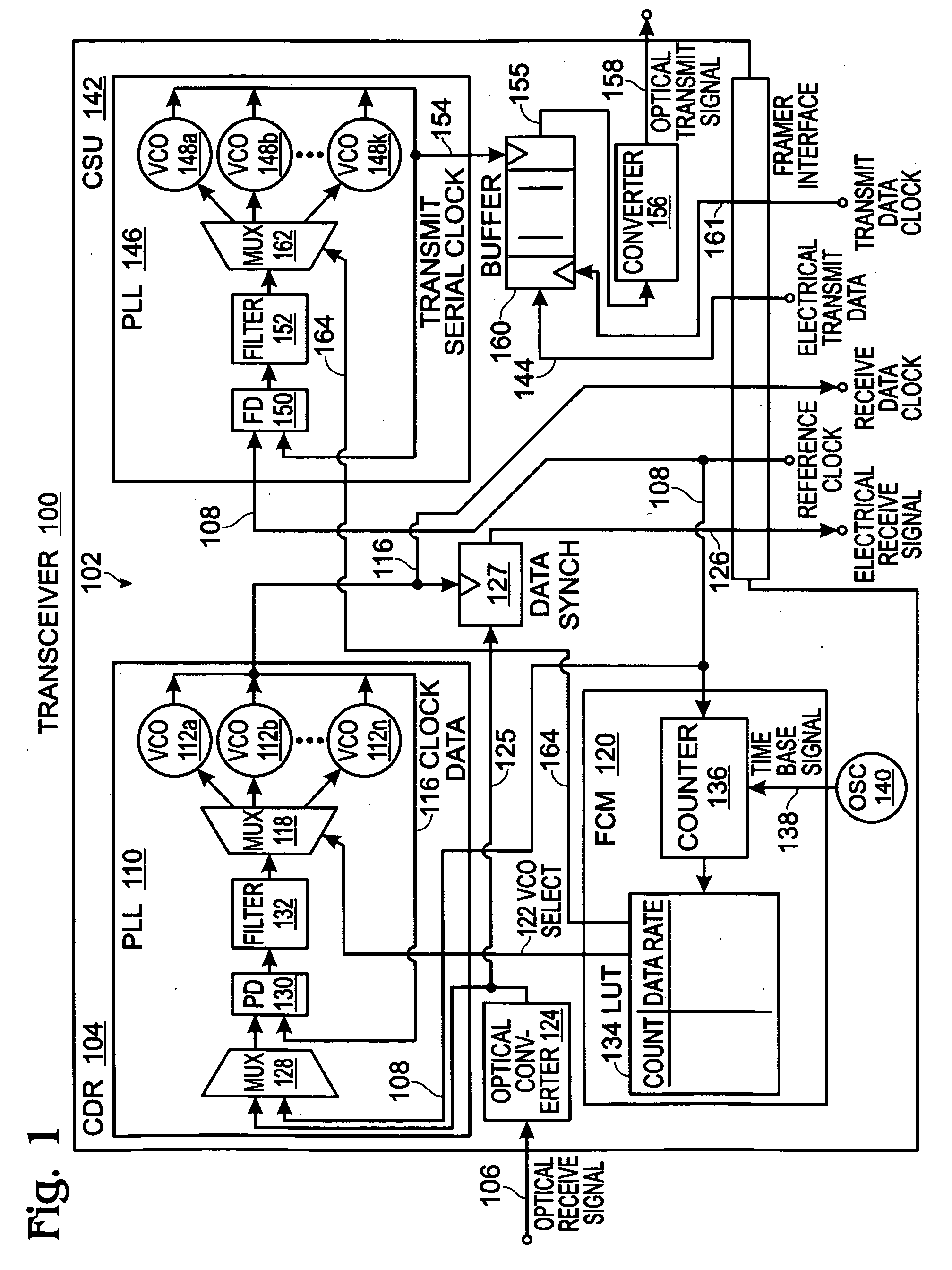

[0019]FIG. 1 is a schematic block diagram of an optical / electrical transceiver 100 with a system for determining an optical signal frequency range. The system 102 comprises a clock data recovery (CDR) unit 104 having network interface on line 106 to accept an optical receive signal having a non-predetermined data rate. The CDR 104 also has a framer interface to accept an electrical reference clock signal on line 108 having a non-predetermined frequency. The CDR 104 further comprises a phase-locked loop (PLL) 110 including a selectable voltage controlled oscillator (VCO) 112 to supply an electrical receive data clock on line 116 via the framer interface. In one aspect, the CDR PLL 110 includes a plurality of VCOs with a corresponding plurality of unique output frequency ranges, selectively engagable in response to a VCO selection signal. Typically, the VCOs have overlapping output frequency ranges. VCOs 112a through. 112n are shown, selectable through multiplexer (MUX) 118. Note: n i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More