Semiconductor integrated circuit

a technology of integrated circuits and semiconductors, applied in the direction of instruments, generating/distributing signals, pulse techniques, etc., can solve the problems of insufficient reduction of clock skew, clock skew occurring between, clock skew, etc., to reduce power consumption, reduce clock skew, and reduce clock skew

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first exemplary embodiment

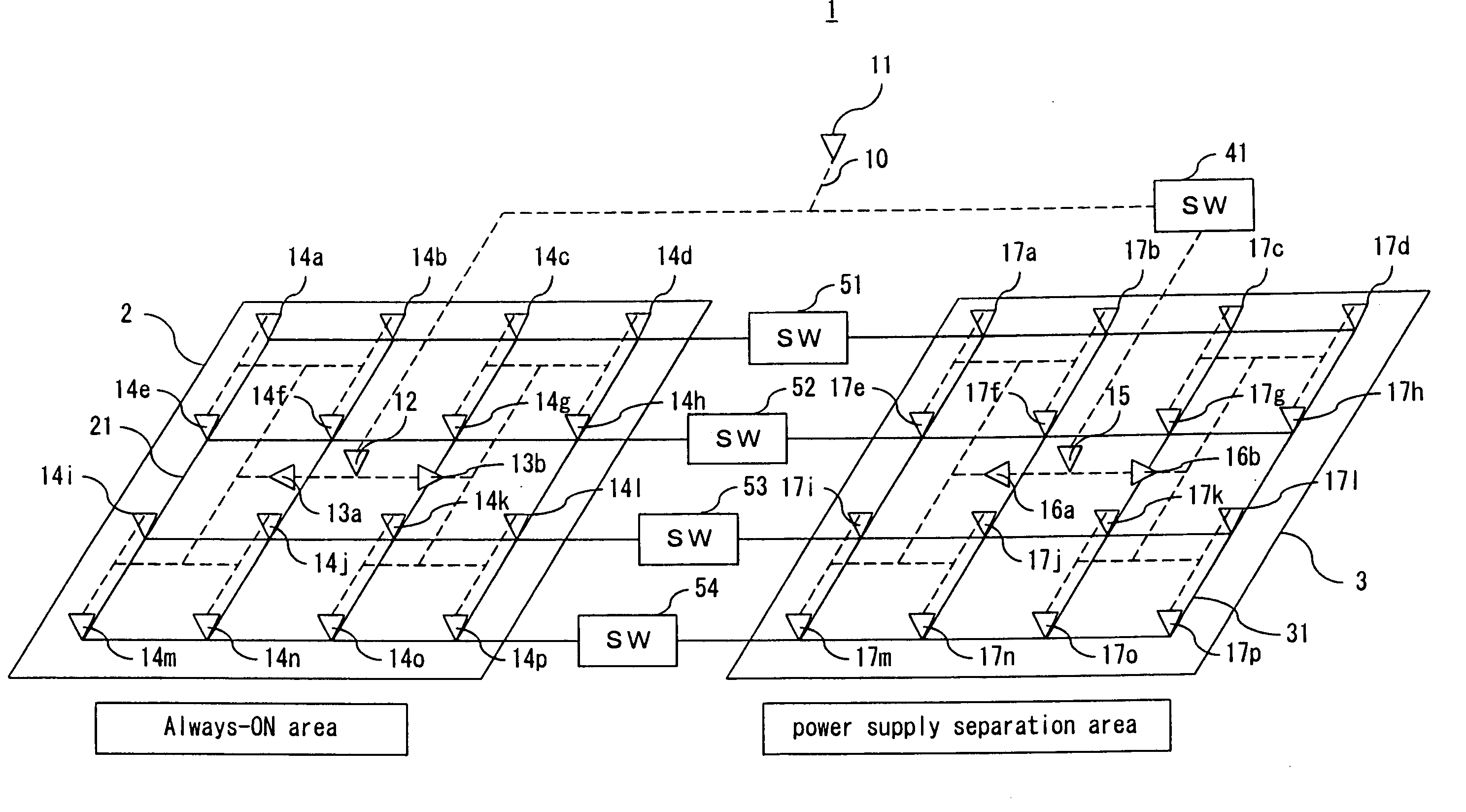

[0035]A configuration of a semiconductor integrated circuit in accordance with a first exemplary embodiment of the present invention is explained with reference to FIG. 1. FIG. 1 is a configuration diagram of a semiconductor integrated circuit in accordance with a first exemplary embodiment of the present invention.

[0036]A semiconductor integrated circuit 1 includes a Always-ON area 2, a power supply separation area 3, a clock tree 10, a clock root buffer 11, a switch (hereafter, referred to as a “clock tree”) 41 and switches 51, 52, 53, and 54. The clock tree 10 includes the clock root buffer 11.

[0037]The clock tree 10 branches in the subsequent stage of the clock root buffer 11. The clock tree 10, in a tree shape wire (hereafter, referred to as a “branch”) in the Always-ON area 2, includes a clock buffer 12 in the next stage of the clock root buffer 11, clock buffers 13a and 13b in the next stage of the clock buffer 12, and clock buffers 14a-14p in the next stage of the clock buff...

second exemplary embodiment

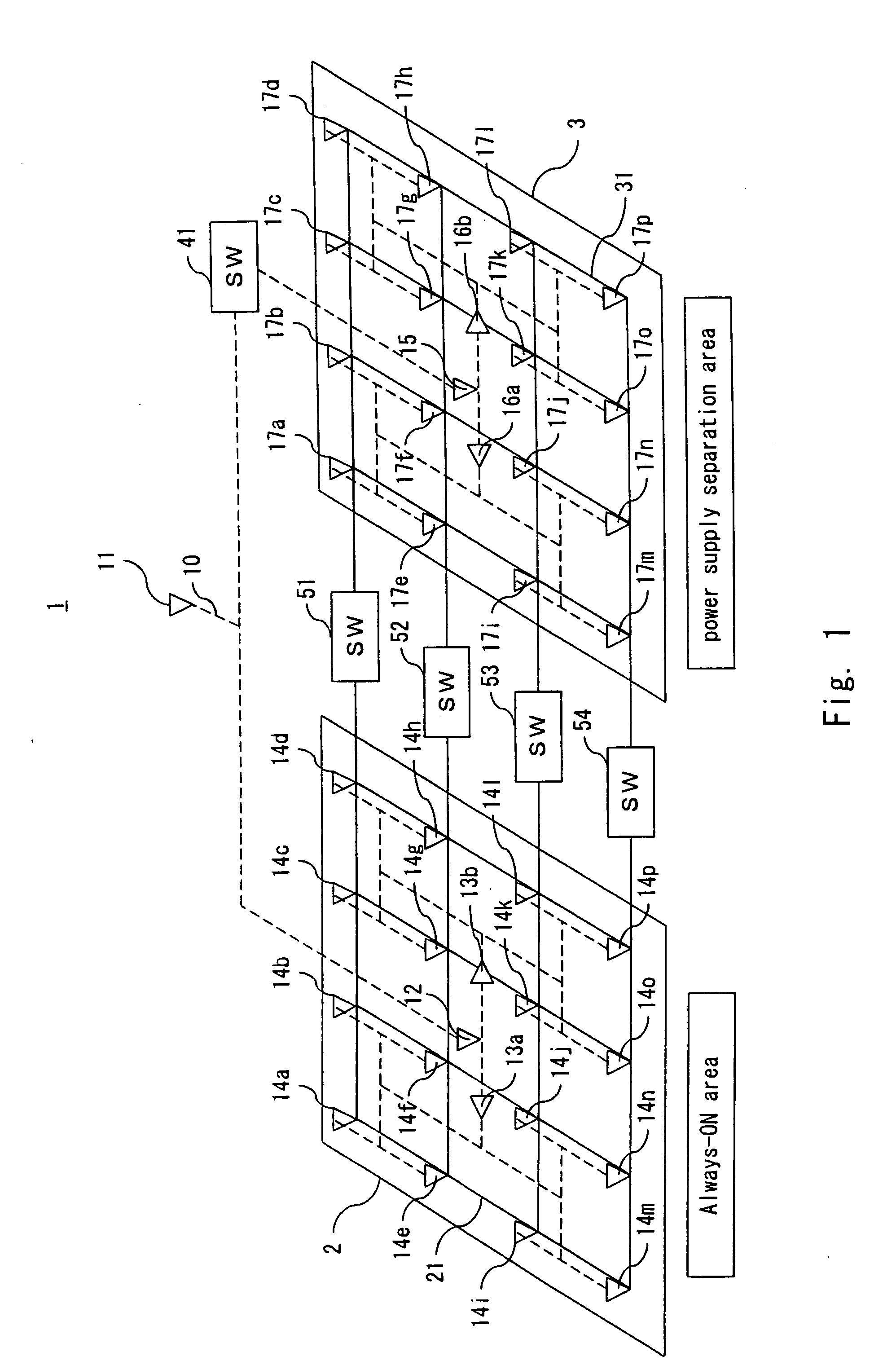

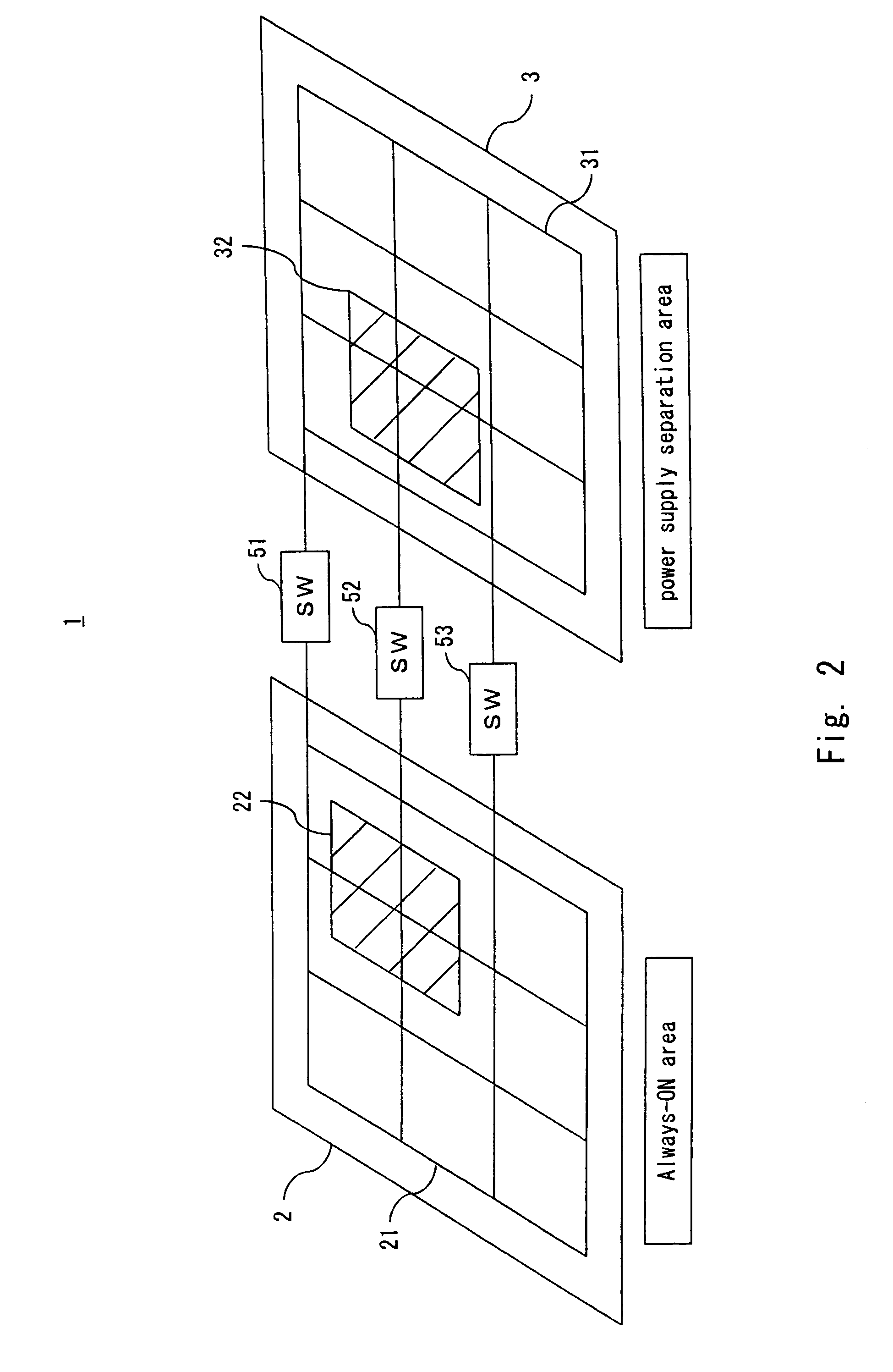

[0057]A configuration of a semiconductor integrated circuit in accordance with a second exemplary embodiment of the present invention is explained with reference to FIG. 2. FIG. 2 is a configuration diagram of a semiconductor integrated circuit in accordance with a second exemplary embodiment of the present invention.

[0058]The semiconductor integrated circuit 1 in accordance with a second exemplary embodiment of the present invention is a semiconductor integrated circuit 1 is, in accordance with a first exemplary embodiment of the present invention, in which the Always-ON area 2 includes a drive target circuit 25 and the power supply separation area 3 includes a drive target circuit 35.

[0059]In the second exemplary embodiment of the present invention, as shown in FIG. 2, the SWs 51-53 are laid out at a position that corresponds to the place laid out the drive target circuits 22 and 32 of the clock mesh 21 and the clock mesh 31.

[0060]As explained in the related arts, the reason why t...

third exemplary embodiment

[0064]A configuration of a semiconductor integrated circuit in accordance with a third exemplary embodiment of the present invention is explained with reference to FIG. 3. FIG. 3 is a configuration diagram of a semiconductor integrated circuit in accordance with a third exemplary embodiment of the present invention.

[0065]The semiconductor integrated circuit 1 in accordance with a third exemplary embodiment of the present invention includes the Always-ON area 2 and the power supply separation area 3 as with the first exemplary embodiment of the present invention. The Always-ON area 2 includes clock meshes 23 and 24, and a drive target circuits 25 and 26. The power supply separation area 3 includes clock meshes 33 and 34, and the drive target circuits 35 and 36.

[0066]The clock meshes 23, 24, 33, and 34 are supplied with a clock signal from the clock tree (not shown) to reduce the clock skew each of the Always-ON area 2 and the power supply separation area 3.

[0067]The clock mesh 23 sup...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com