Optimization method of multi-level gating clock network in nanotechnology

A gated clock and clock network technology, applied in the electronic field, can solve problems such as single structure and limited effect of multi-level gated clock design, and achieve the effects of reducing clock deviation, regular clock structure, and increasing clock common paths

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] The present invention will be described in further detail below in conjunction with the accompanying drawings and embodiments.

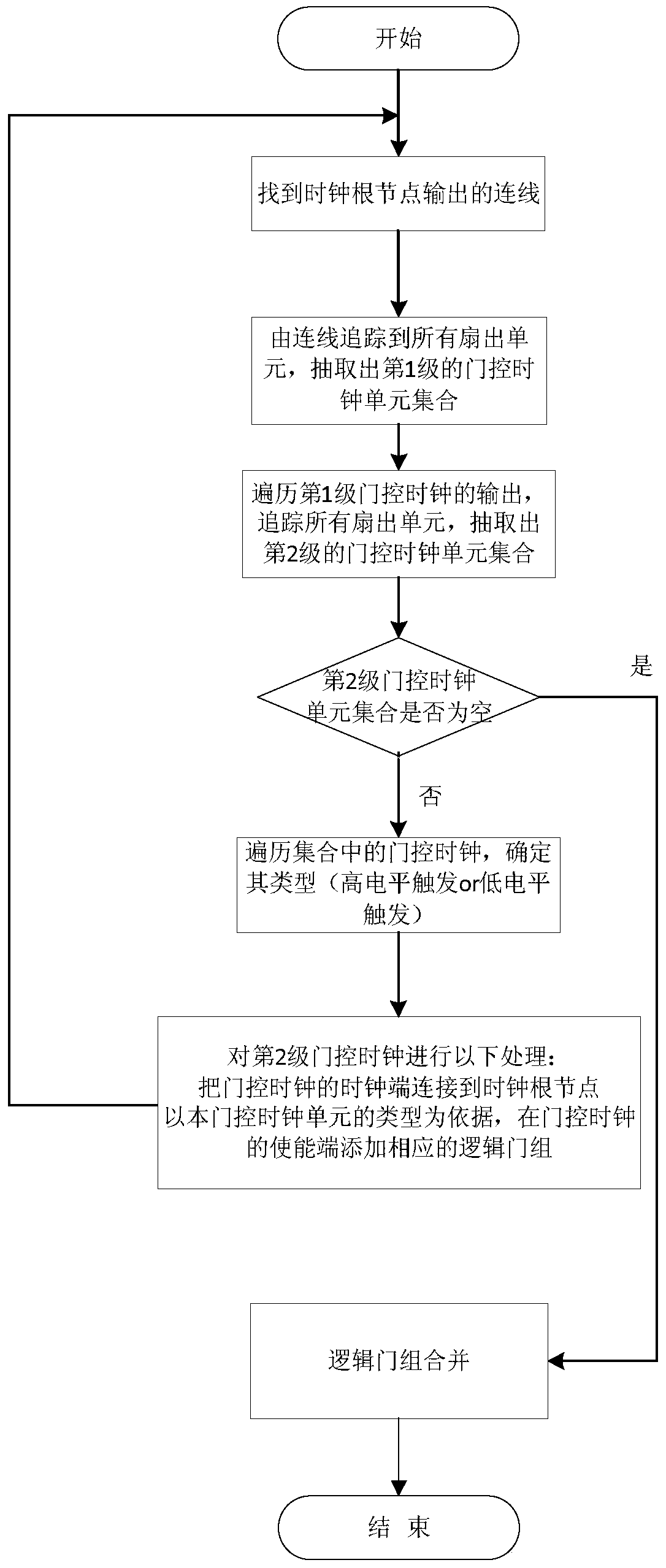

[0037] Such as figure 1 As shown in the figure, it is a flow chart of reducing the multi-level gating clock to level 1. The specific process is as follows:

[0038] (11) Starting from the clock root node, find its connection;

[0039] (12) From all the units traced to the fan-out by the connection, find out all the gated clock units directly connected to the clock root node to form a set of the first-level gated clock units;

[0040] (13) Traverse each element (i.e., the gated clock unit) in the set of the first-level gated clock unit obtained in step (12) to perform the following operations: ① detect the type of the gated clock unit (high level trigger or low-level trigger) and record, ②find and record the connection of the enable terminal input of the gated clock unit, and record, ③find and record the connection of the output terminal of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More