Method for testing nonlinearity error of high speed digital-to-analog converter

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

The embodiments are described in detail in cooperation with the drawings to demonstrate the technical contents of the present invention.

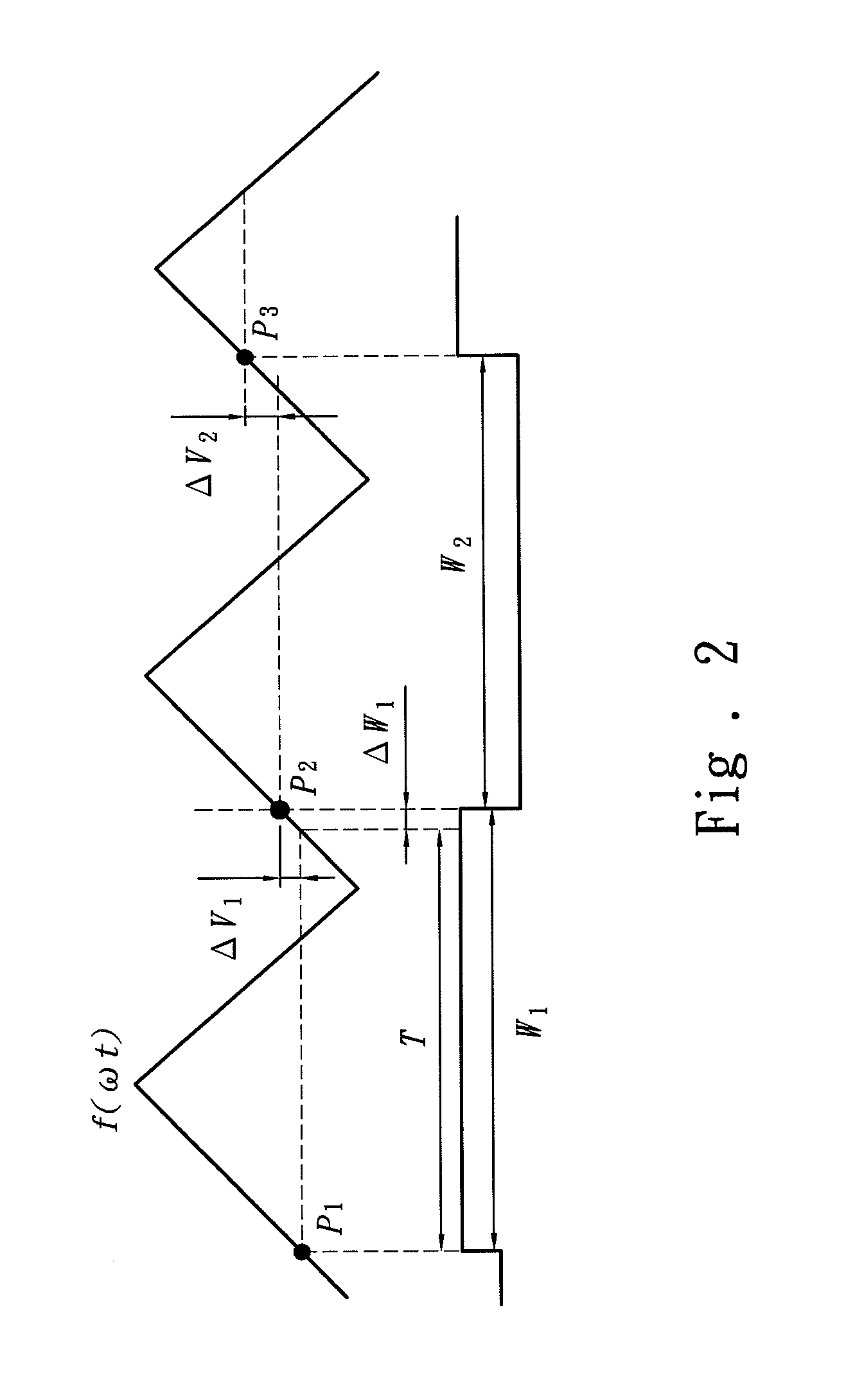

Refer to FIG. 2 and FIG. 3 for the sampling theorem of the present invention. Suppose that f(ωt) is the waveform output by a digital-to-analog converter (DAC) 10 and that the waveform has a period of T. Three sampling points p1, p2 and p3, which are originally sampled from a single cycle, are respectively arranged in three different cycles. Respectively define the time difference and voltage difference of a first sampling point and a second sampling point to be ΔW1 and ΔVi. Thus, ΔWi=Wi−T. The nonlinearity error of the tested circuit f(ωt) / dt can express the signal difference of the sampling points as the pulse width signal, i.e. the variation of the pulse width ΔWi.

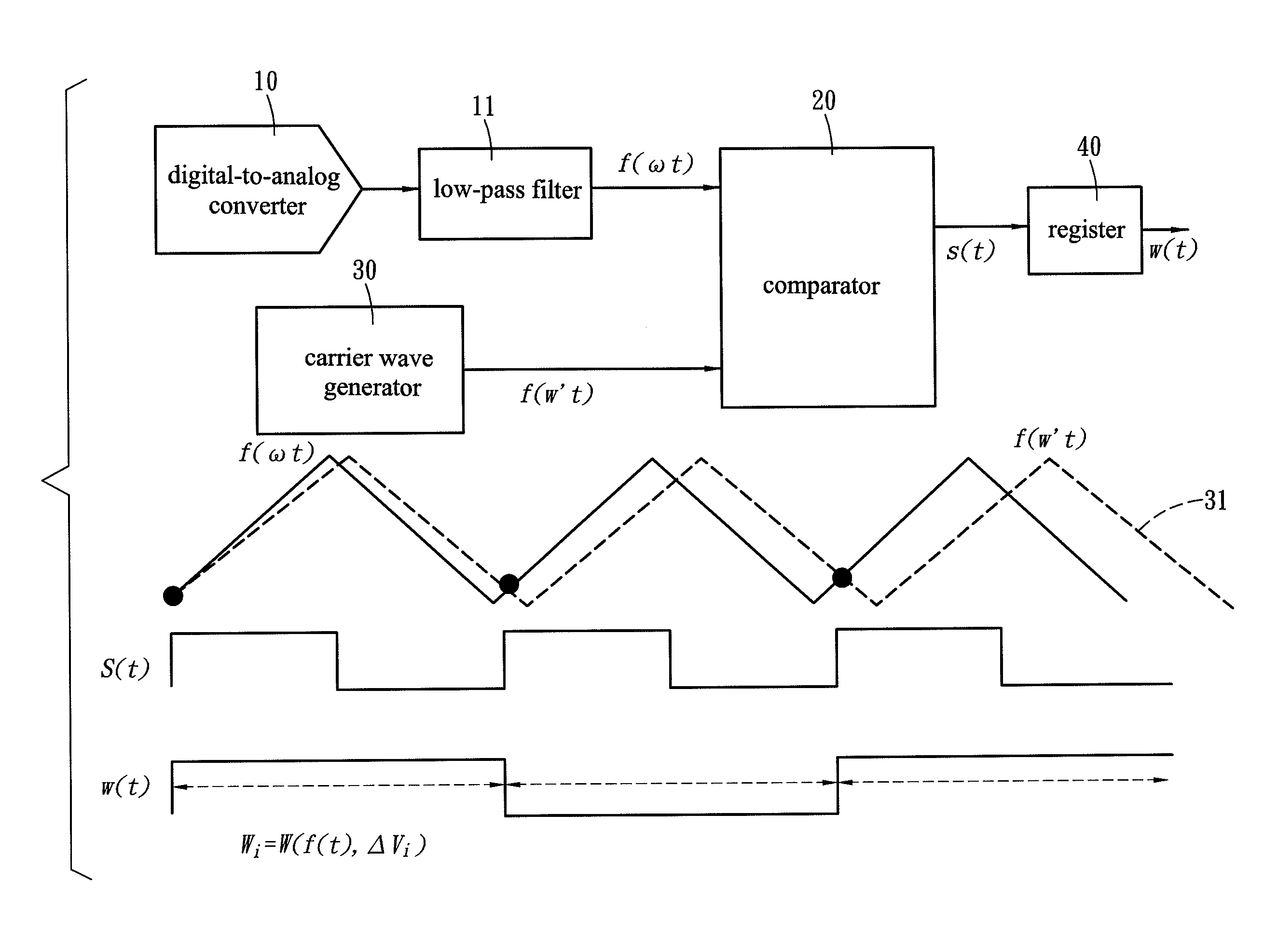

Refer to FIG. 3 for the sampling circuit according to the present invention. In FIG. 3, f(ωt) is the digital-to-analog conversion output signal of the DAC 10. The digital-to-analog conve...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More