Method for packaging wafer

a technology of wafers and packaging, applied in the direction of basic electric elements, electrical apparatus, semiconductor devices, etc., can solve the problems of difficulty in forming through silicon vias, insulation problems of through silicon vias, and damage to existing circuitry, so as to reduce the cost of substrate, reduce the cost of wire bonding and molding/encapsulation process, and achieve high density chips.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

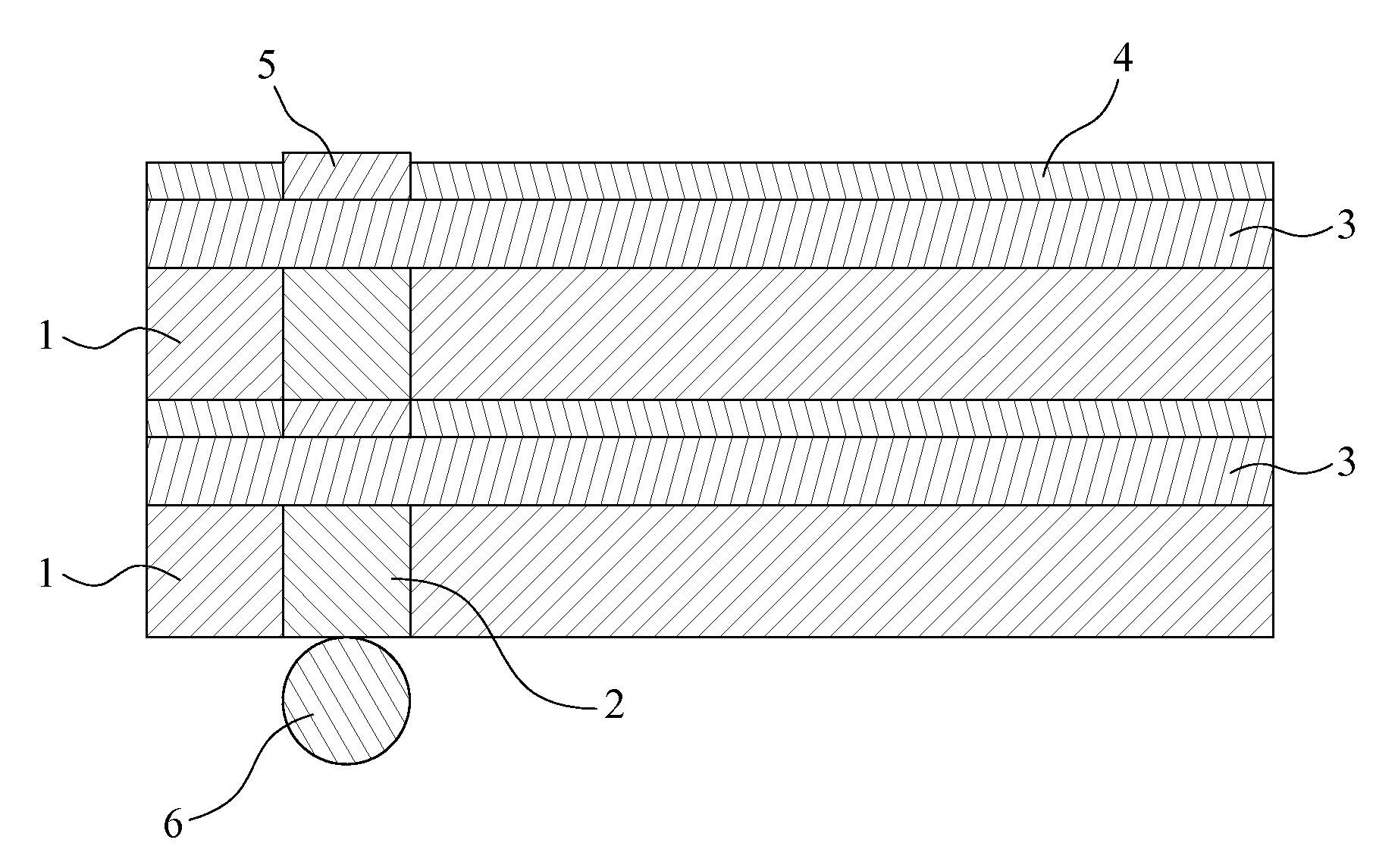

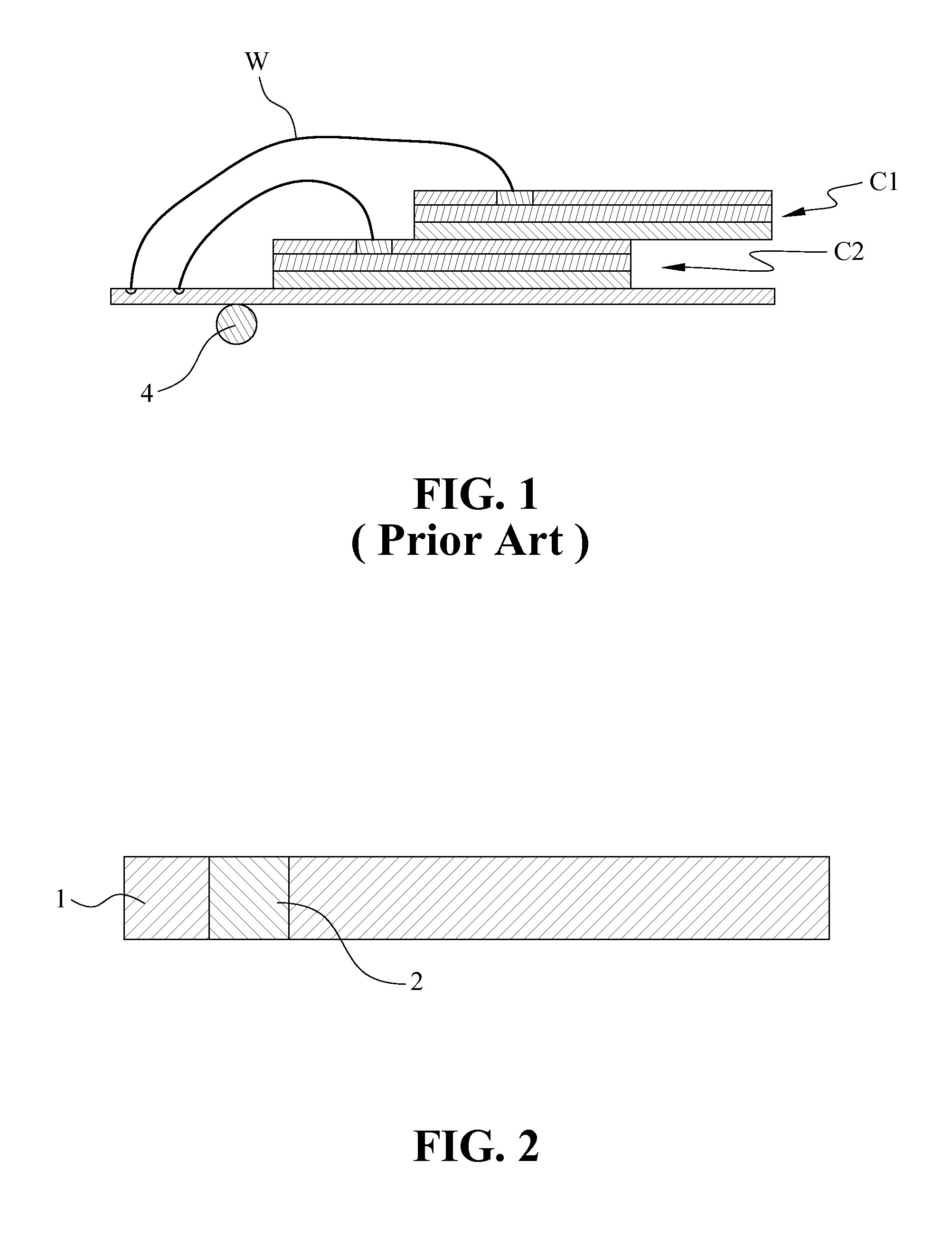

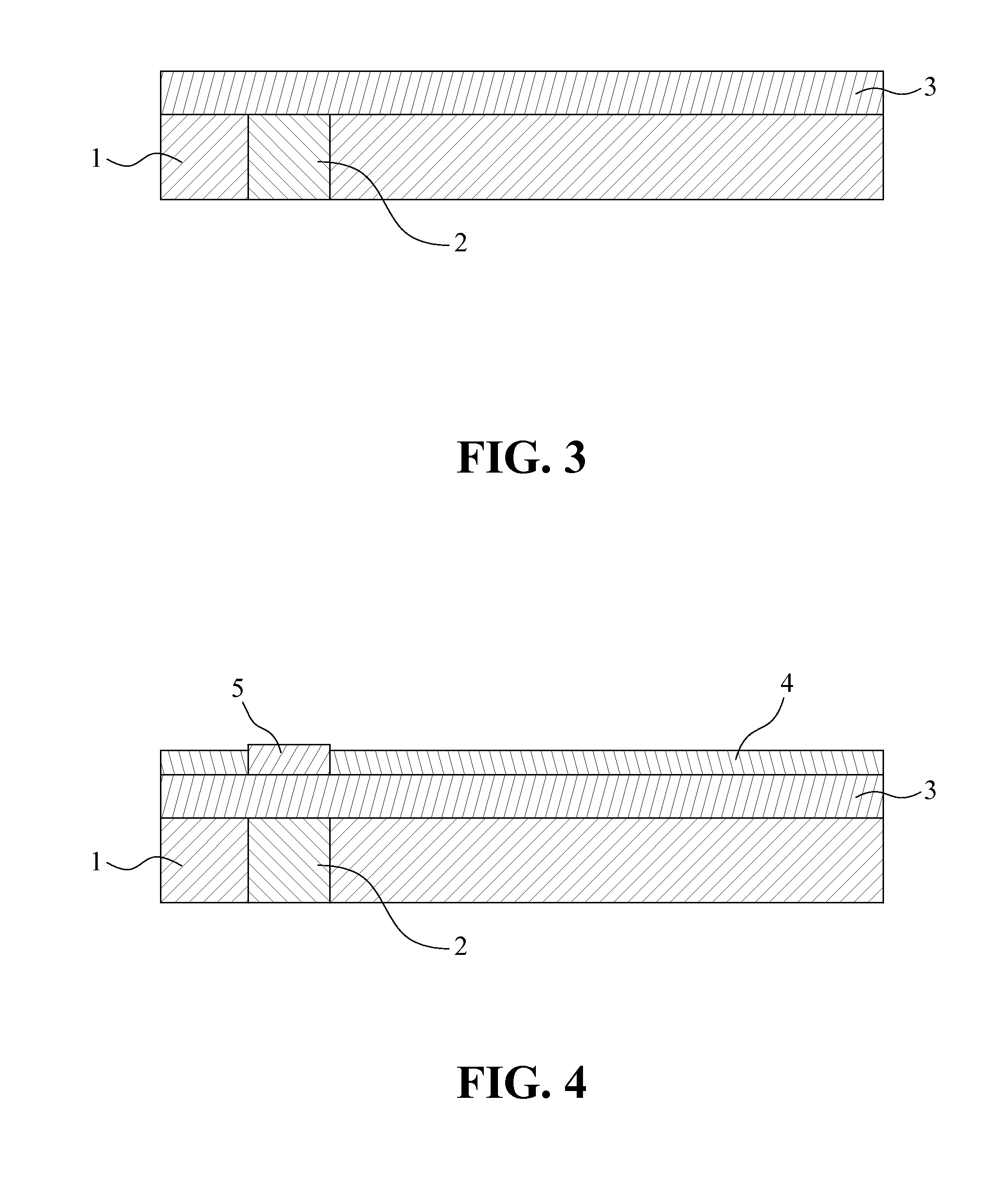

[0013]The method for packaging a wafer of the present invention comprises the steps as following: (1) a plurality of through silicon vias across through the bare wafer 1 are formed at the predetermined positions of the bare wafer 1, and the through silicon vias are filled with the conducting metal 2 (as shown in FIG. 2); (2) a redistribution layer is formed on the bare wafer 1, and the redistribution layer is connected to each of the through silicon vias; (3) a chemical mechanical polishing process is performed to planarize a surface of the bare wafer 1; (4) a wafer forming process is performed to treat the planarized bare wafer; (5) a metal layer 3 is formed on the wafer 1 after processed (as shown in FIG. 3); (6) a plurality of connection pads 5 are formed on the metal layer 3, and the connection pads 5 are respectively electrically connected to their corresponding through silicon vias (as shown in FIG. 4); (7) a passivation layer 4 is formed on the metal layer 3 (referring to FIG...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More