Reduced residual offset sigma delta analog-to-digital converter (ADC) with chopper timing at end of integrating phase before trailing edge

a residual offset and analog-to-digital converter technology, applied in analogue/digital conversion, instruments, transmission systems, etc., can solve problems such as errors in chopper stabilization and more charge under their channels

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

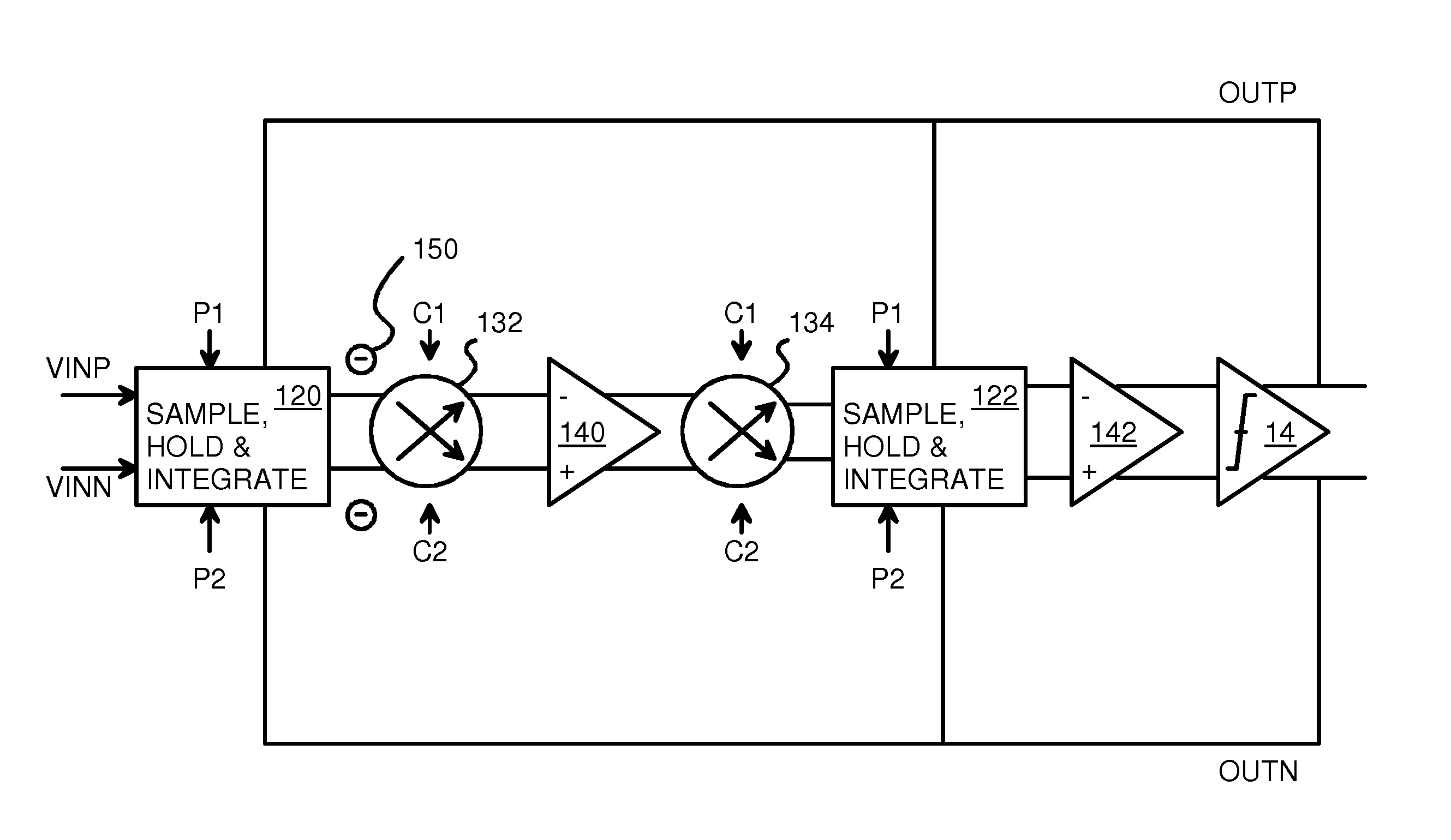

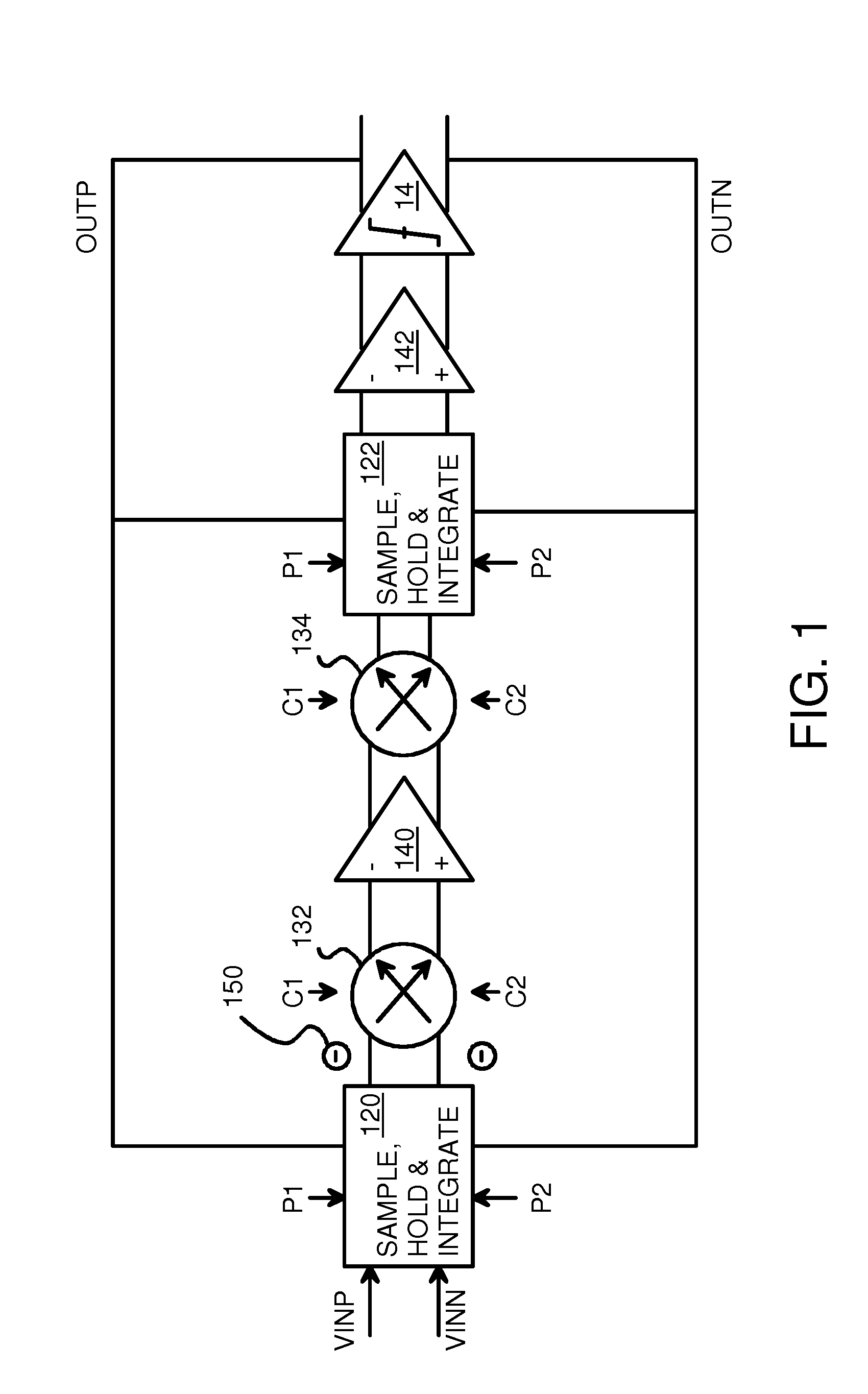

[0026]The present invention relates to an improvement in chopper-stabilized sigma-delta modulators. The following description is presented to enable one of ordinary skill in the art to make and use the invention as provided in the context of a particular application and its requirements. Various modifications to the preferred embodiment will be apparent to those with skill in the art, and the general principles defined herein may be applied to other embodiments. Therefore, the present invention is not intended to be limited to the particular embodiments shown and described, but is to be accorded the widest scope consistent with the principles and novel features herein disclosed.

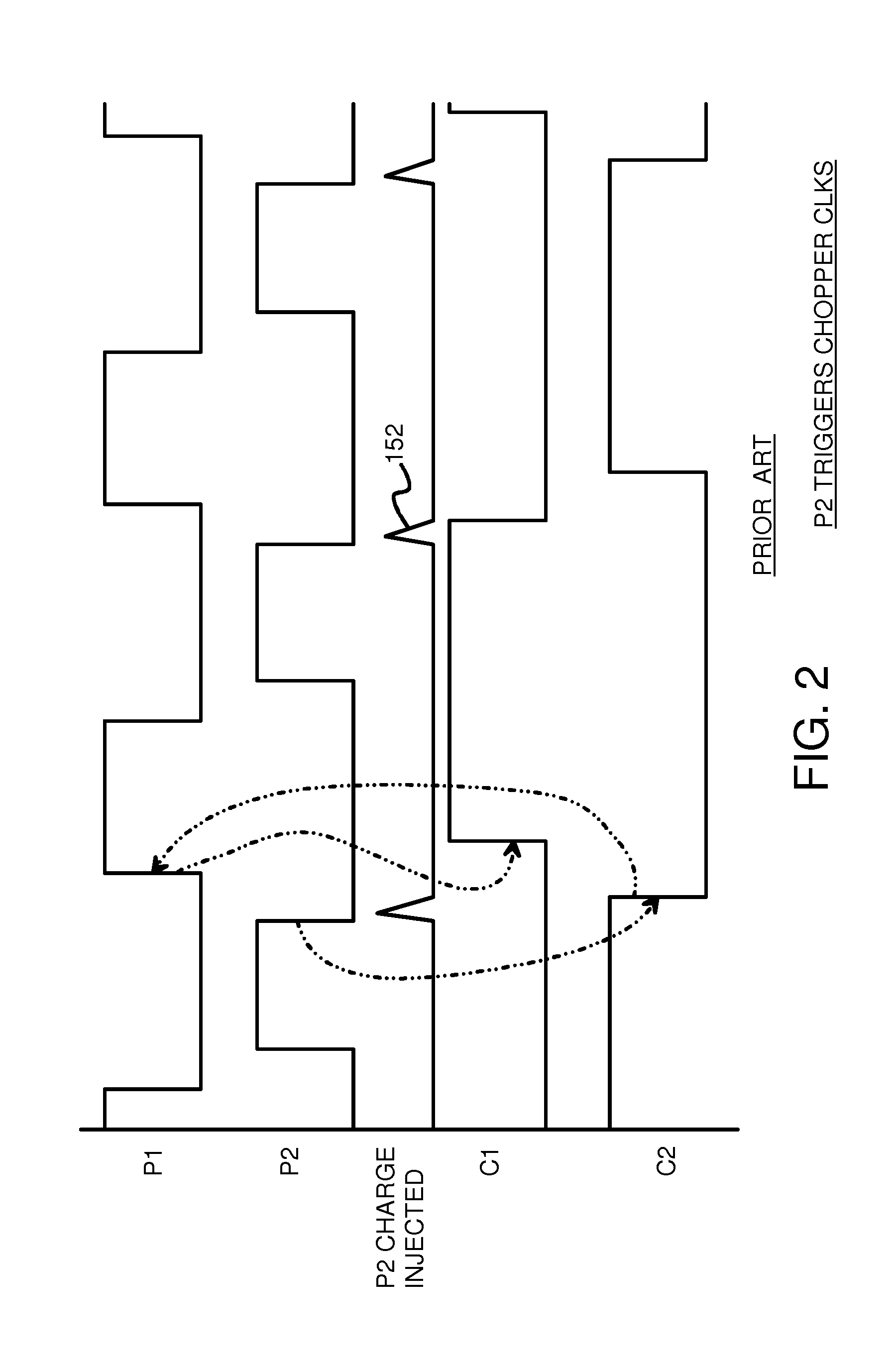

[0027]The inventors have realized that the prior-art chopper-clock timing is undesirable since charge is injected by the phase clock turning off just before the chopper clocks change. The injected charge occurs at a critical time when node voltages should be stable. The inventors further realize that chopper ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More