Mixer bias circuit

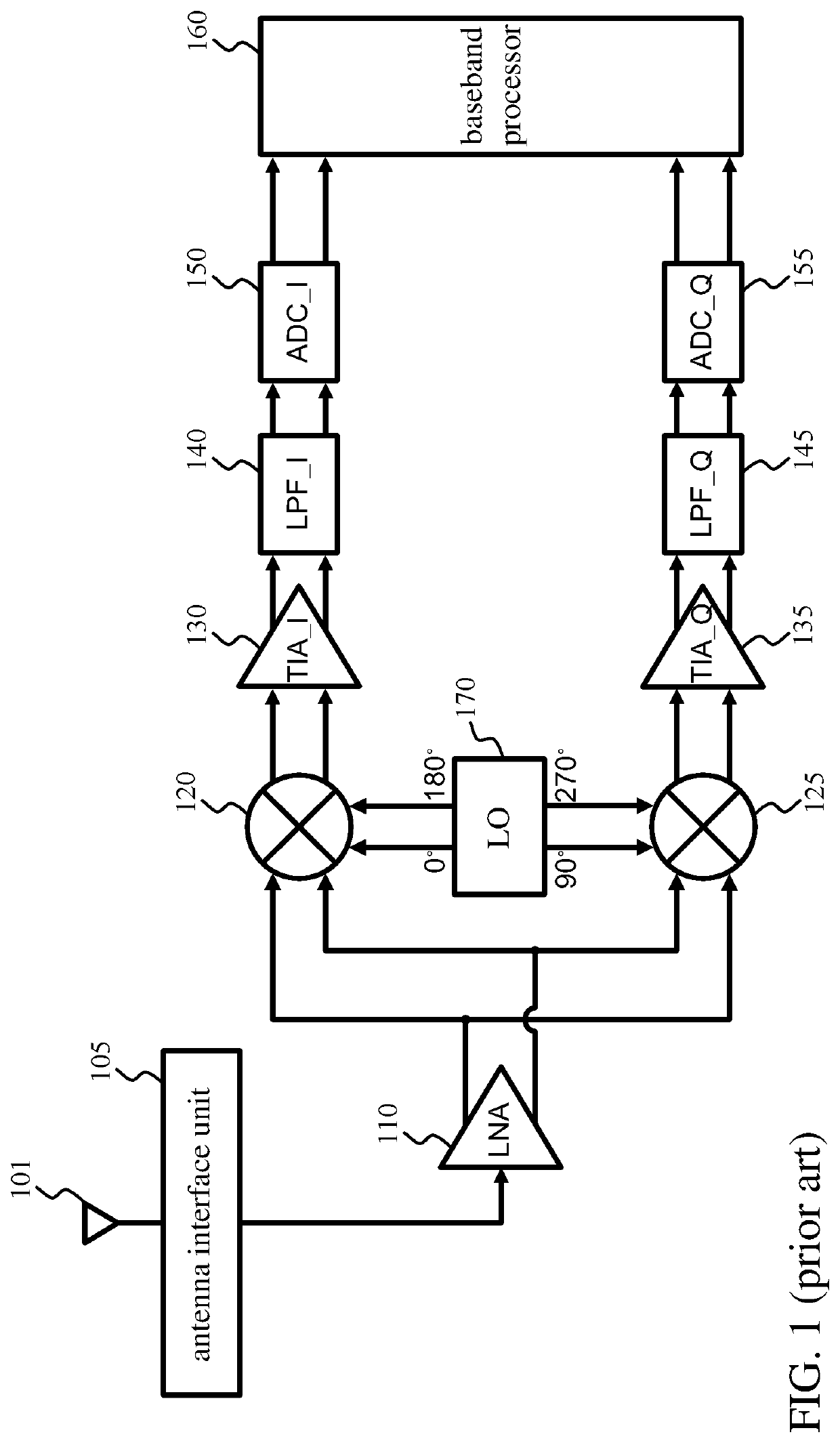

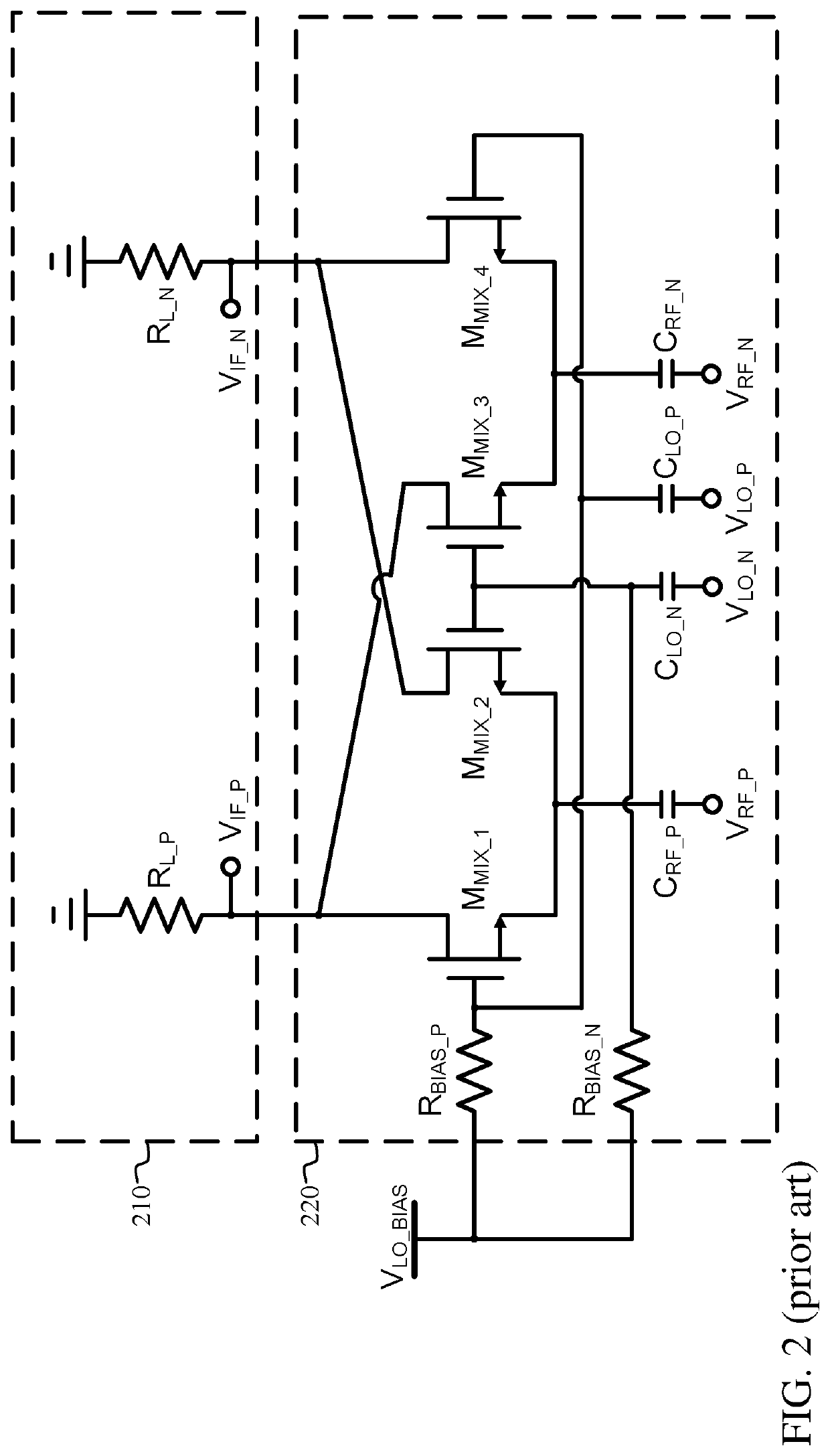

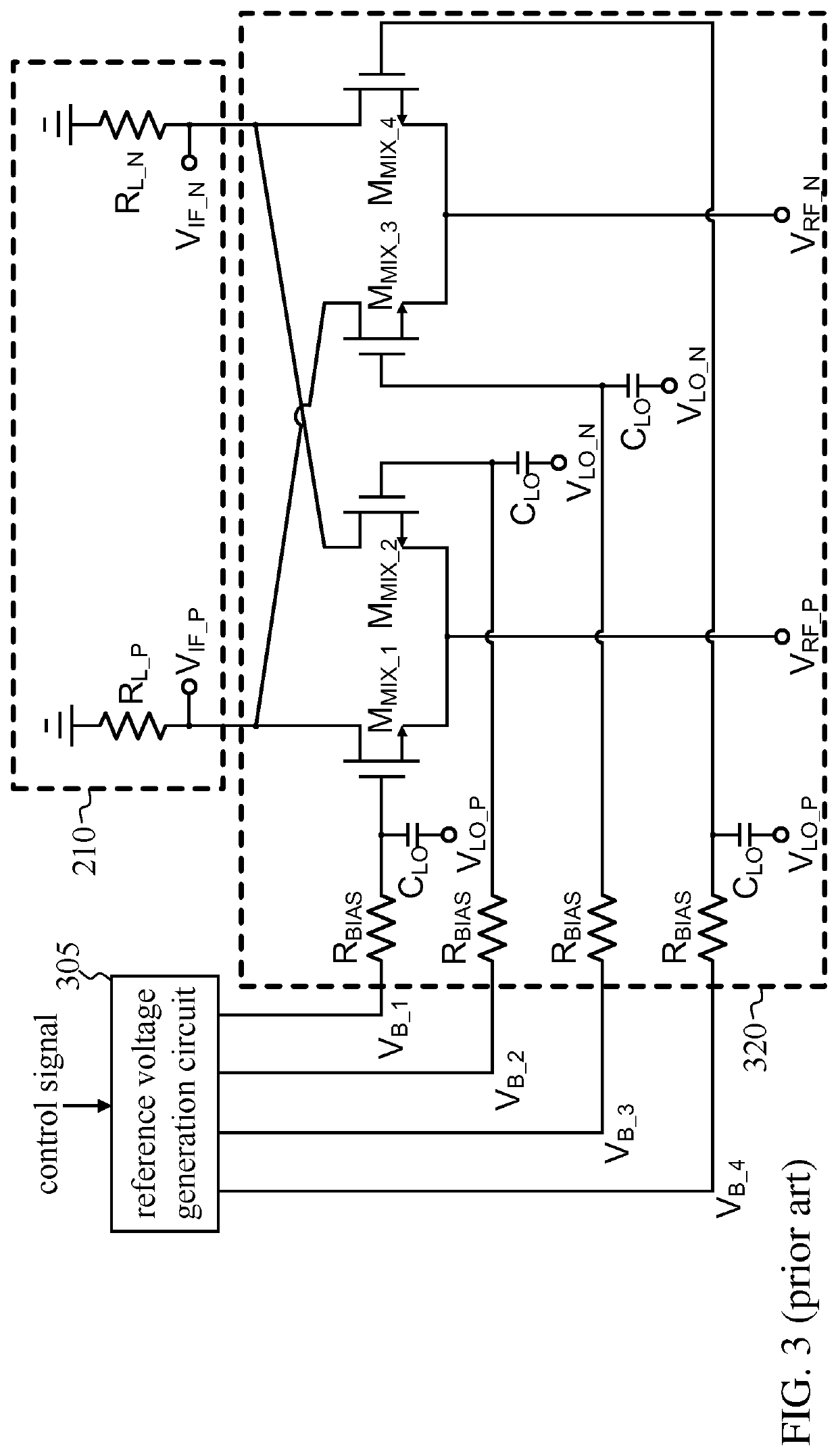

a bias circuit and mixer technology, applied in the field of mixer bias circuits, can solve the problems of affecting the sensitivity of the rf rxfe, the ip2 degradation of the calibrated mixer, and the imr performance of the dc offset and image rejection ratio (imr), so as to improve the ip2

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022]The following description is written by referring to terms of this technical field. If any term is defined in this specification, such term should be explained accordingly. In addition, the connection between objects or events in the below-described embodiments can be direct or indirect provided that these embodiments are practicable under such connection. Said “indirect” means that an intermediate object or a physical space exists between the objects, or an intermediate event or a time interval exists between the events.

[0023]The disclosure herein includes a mixer bias circuit. On account of that some or all elements of the mixer bias circuit could be known, the detail of such elements is omitted provided that such detail has little to do with the features of this disclosure and this omission nowhere dissatisfies the specification and enablement requirements. A person having ordinary skill in the art can choose components equivalent to those described in this specification to...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More