Synchronous semiconductor memory device having an auto-precharge function

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

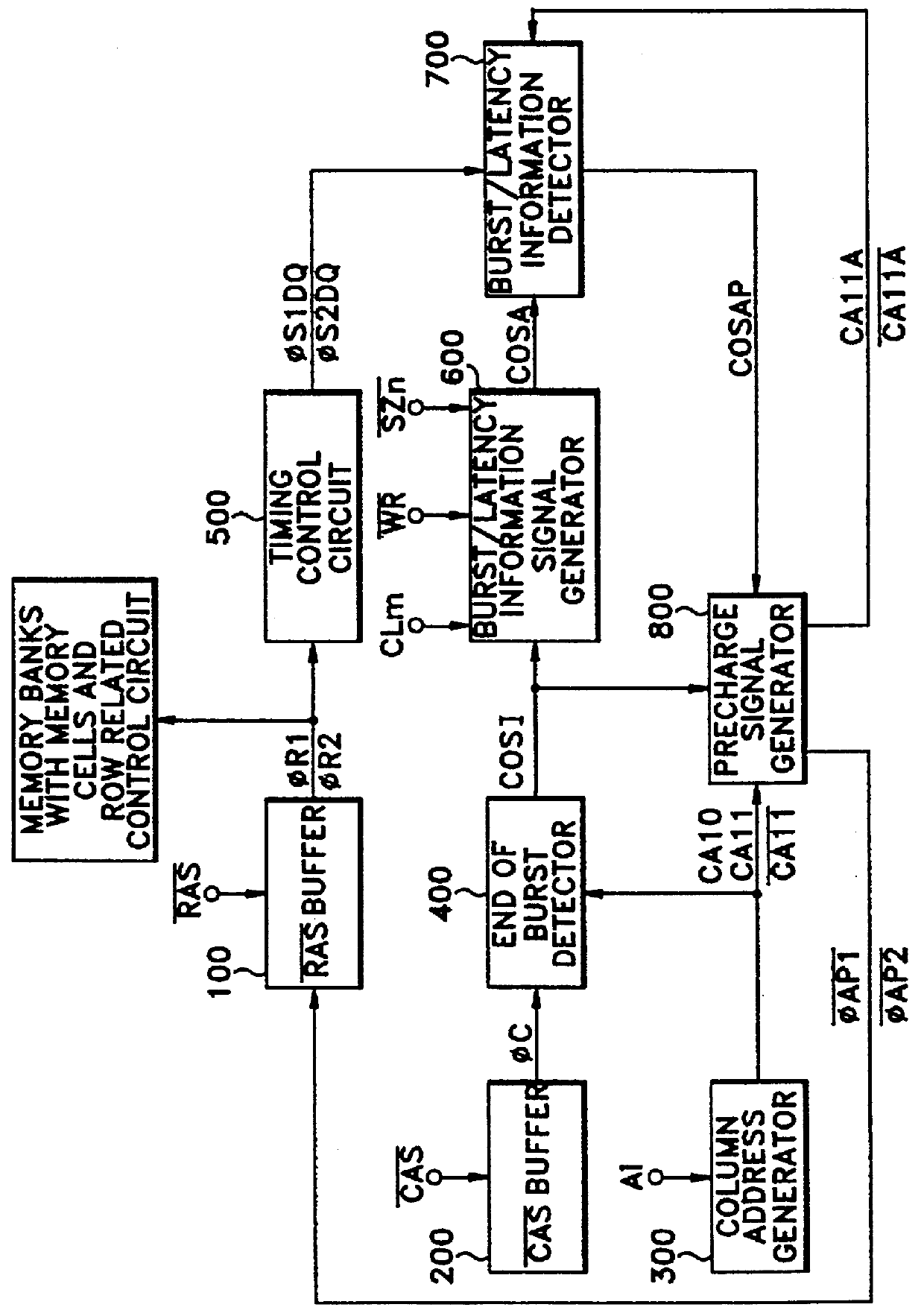

The construction of FIG. 2 required in realizing an auto precharge function according to the present invention includes a RAS buffer 100 that receives a row address strobe signal RAS and then generates row master clocks .phi.R1 and .phi.R2. A CAS buffer 200 receives a column address strobe signal CAS and then generates a column master clock .phi.C which drives column related control circuits. A column address generator 300 receives and buffers an address signal Ai to a CMOS level and then generates a plurality of column address signals (include CA10, CA11 and CA11) from the buffed address signal. An end of burst detector 400 receives the column master clock .phi.C and the counted column address signals and then generates a burst length detection signal COSI which detects the end state of the burst length. A timing controller 500 receives the row master clocks .phi.R1 and .phi.R2 and then generates timing control signals .phi.S1DQ and .phi.S2DQ. A burst / latency information signal gen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More