Method of multi-level storage in DRAM and apparatus thereof

a multi-level storage and dram technology, applied in differential amplifiers, dc-amplifiers with dc-coupled stages, amplifiers, etc., can solve the problems of low noise margin, method suffers from poor signal margin, and cannot withstand the occasional -particle hit, so as to achieve relatively large noise margin and increase yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

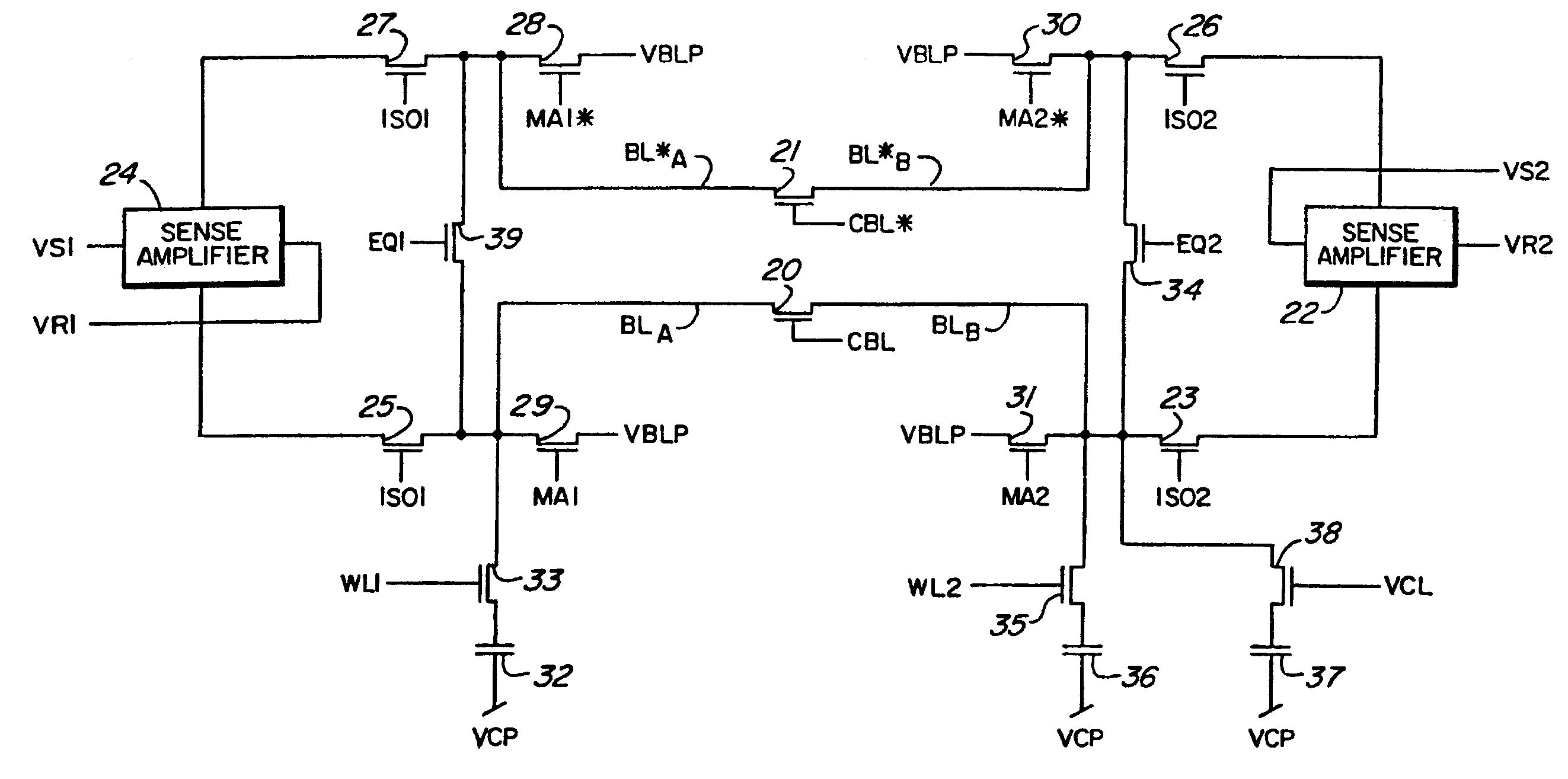

[0021]For a DRAM cell to store two bits using a single cell capacitor, the cell capacitor should store one of four voltage values Vcell0, Vcell1, Vcell2 or Vcell3, wherein Vcell0 represents the lowest and Vcell3 represents the highest cell voltage. To differentiate between the voltages, mid-point voltages Vref1, Vref2 and Vref3 are defined, as shown in FIG. 1. It may be seen that if the lowest actual cell voltage Vcell0 is VSS or zero, Vref1 is one-sixth the highest voltage VDD, Vcell1 is one-third VDD, Vref2 is one-half VDD, Vcell2 is two-thirds VDD, Vref3 is five-sixths VDD and Vcell3 equals VDD. Thus it may be seen that Vref1 is midway between Vcell0 and Vcell1, Vref2 is midway between Vcell0 and Vcell3 and Vref3 is midway between Vcell2 and Vcell3.

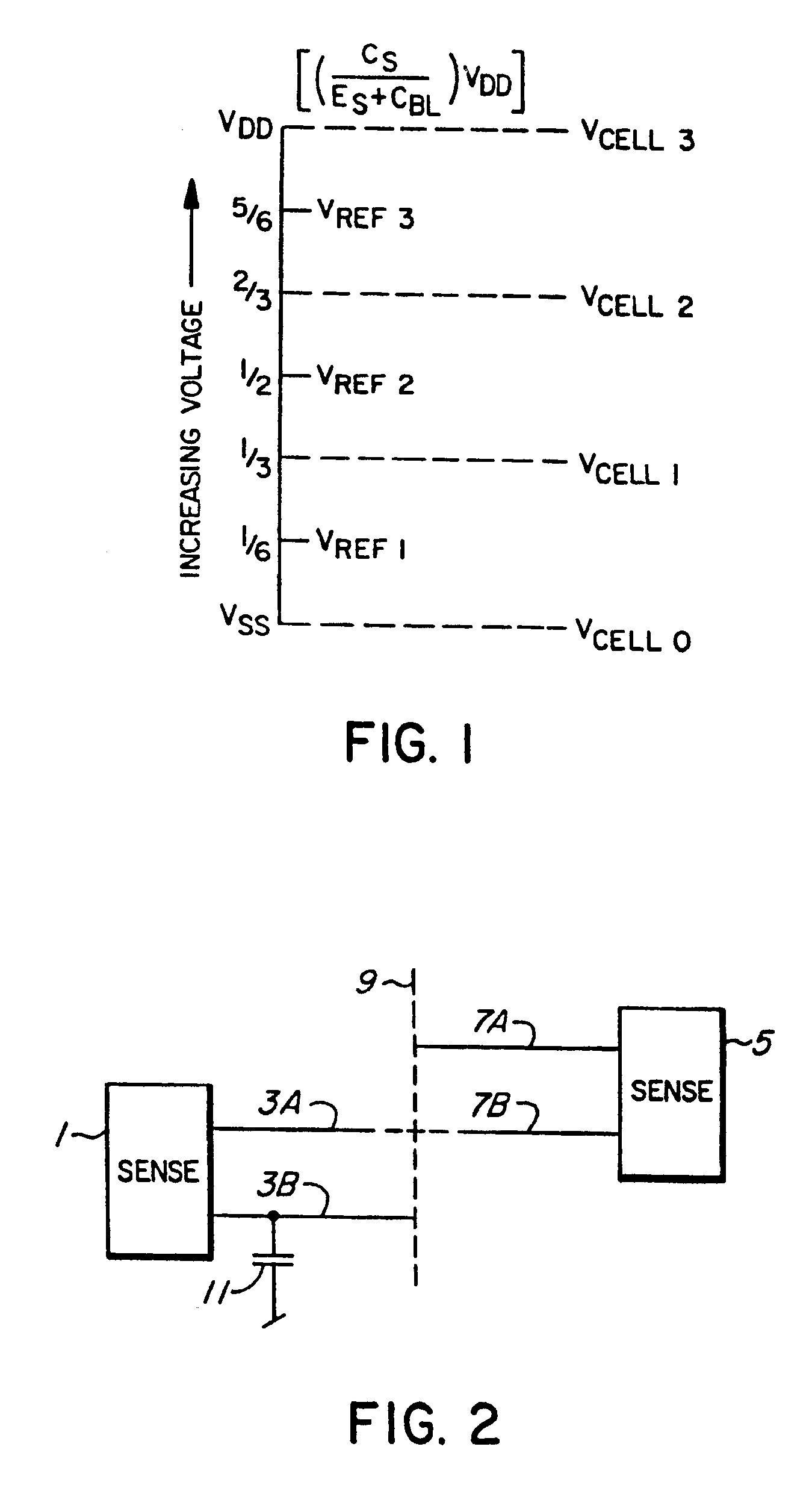

[0022]FIG. 2 will be used to illustrate the basic concept of the invention. A sense amplifier 1 can be connected to a pair of conductors 3A and 3B which form a folded bitline. Another sense amplifier 5 can be connected to a pair of con...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More