Method and system for displaying an analog image by a digital display device

a digital display device and analog image technology, applied in the field of graphics systems, can solve the problems of jitter in both reference signals, the reference frequency can drift over a prolonged period of time, and the integration difficulty of a relatively small-sized integrated circuit, so as to achieve considerable flexibility and instantaneous change of the bandwidth of the pll

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042]1. Overview and Discussion of the Invention

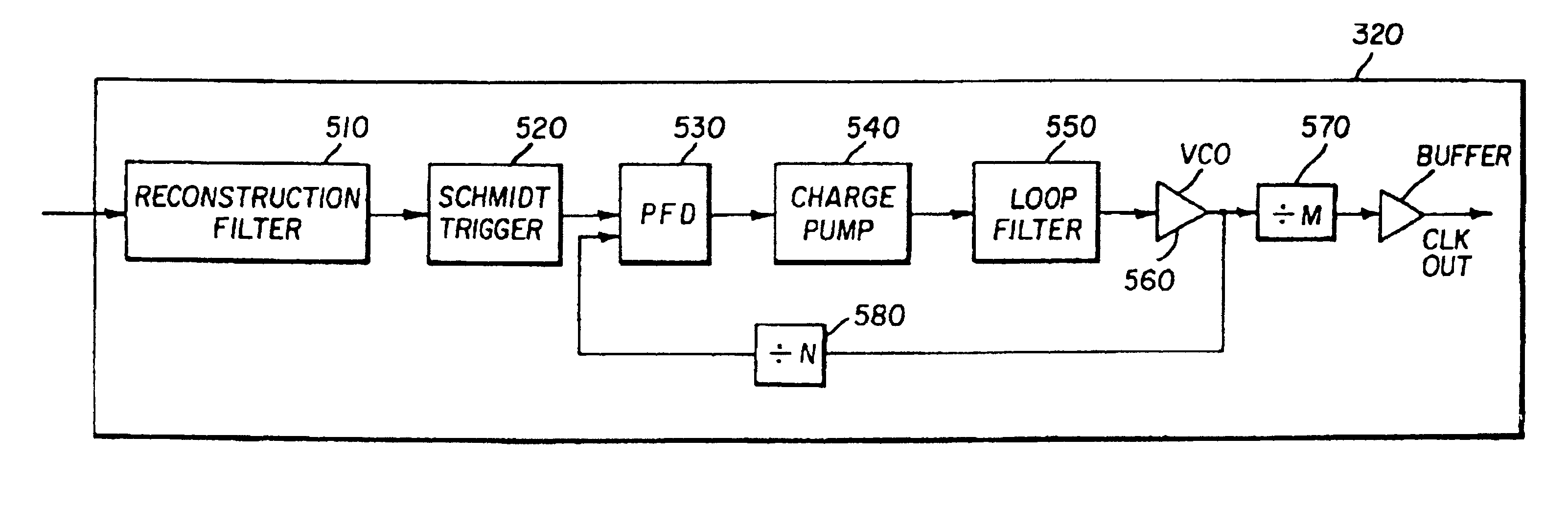

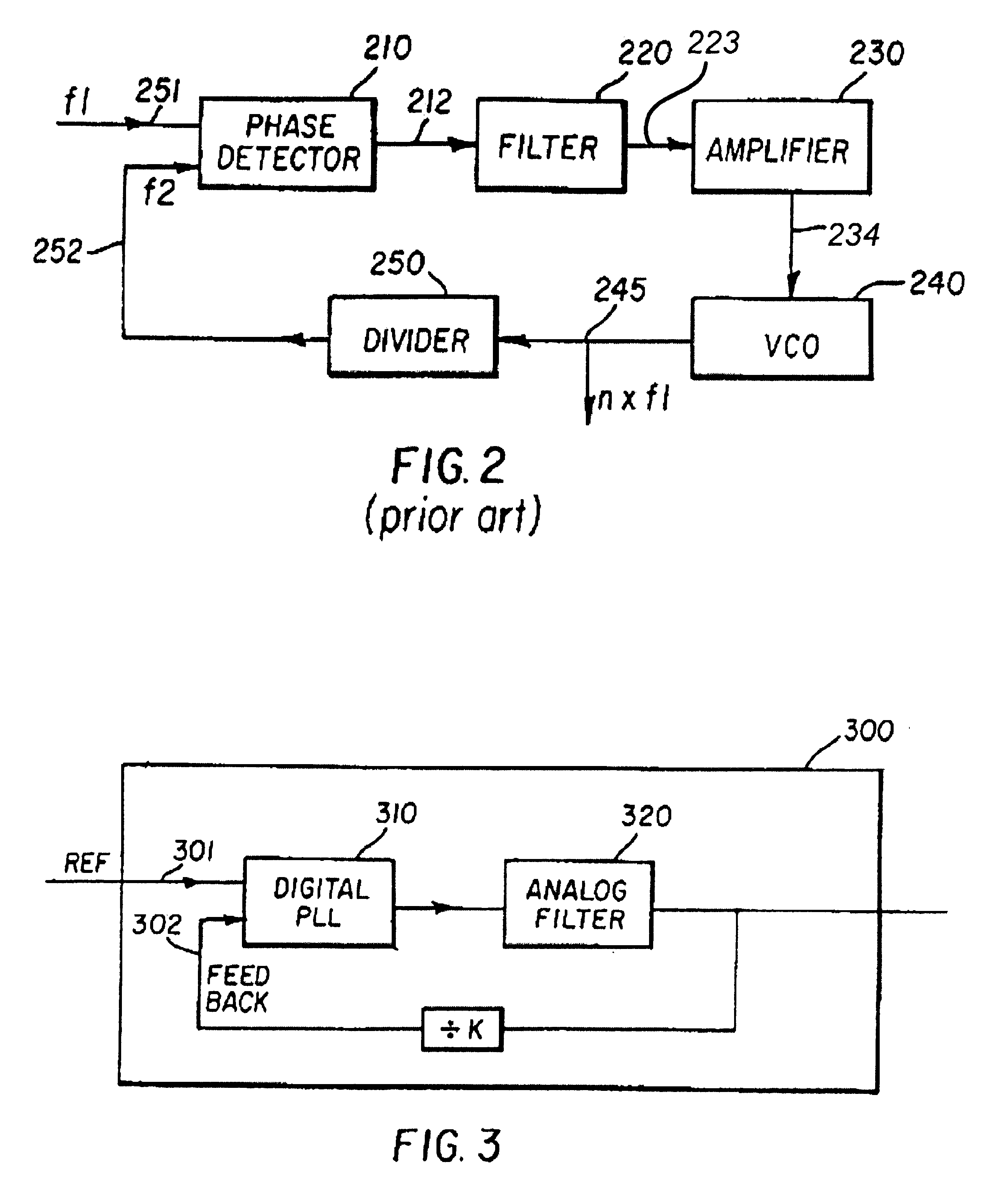

[0043]The present invention is described in the context of clock recovery circuit 300 (FIG. 3) which includes digital PLL circuit 310 and analog filter 320. The output of PLL circuit 310 is coupled to the input of analog filter 320. PLL circuit 310 is implemented using digital components and signals.

[0044]In operation, PLL circuit 310 receives as input a time reference 301 and generates output signal 312. While generating the output signal, PLL signal 310 attempts to synchronize the output signal 312 with time reference. Analog filter 320 filters any undesirable spectral components in the output signal 312 and provides the filtered signal as input to PLL circuit on input 302.

[0045]PLL circuit 310 is implemented using digital components and a designer is provided considerable flexibility to specify the degree or manner in which output signal 312 should track reference signal 301. Due to such a flexibility, the bandwidth of PLL circuit ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More