Multi-phase locked loop for data recovery

a phase lock and data technology, applied in the field of phase lock loop for data recovery, can solve the problems of difficult to reduce clock jitter, worse clock jitter, etc., and achieve the effect of enhancing the tolerance for data random jitter and reducing clock jitter

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029]Before describing the preferred embodiment in accordance with the invention, it should be made clear that the loop filter in the multi-phase-locked loop of the invention are similar to that of the prior art and will not be explained here.

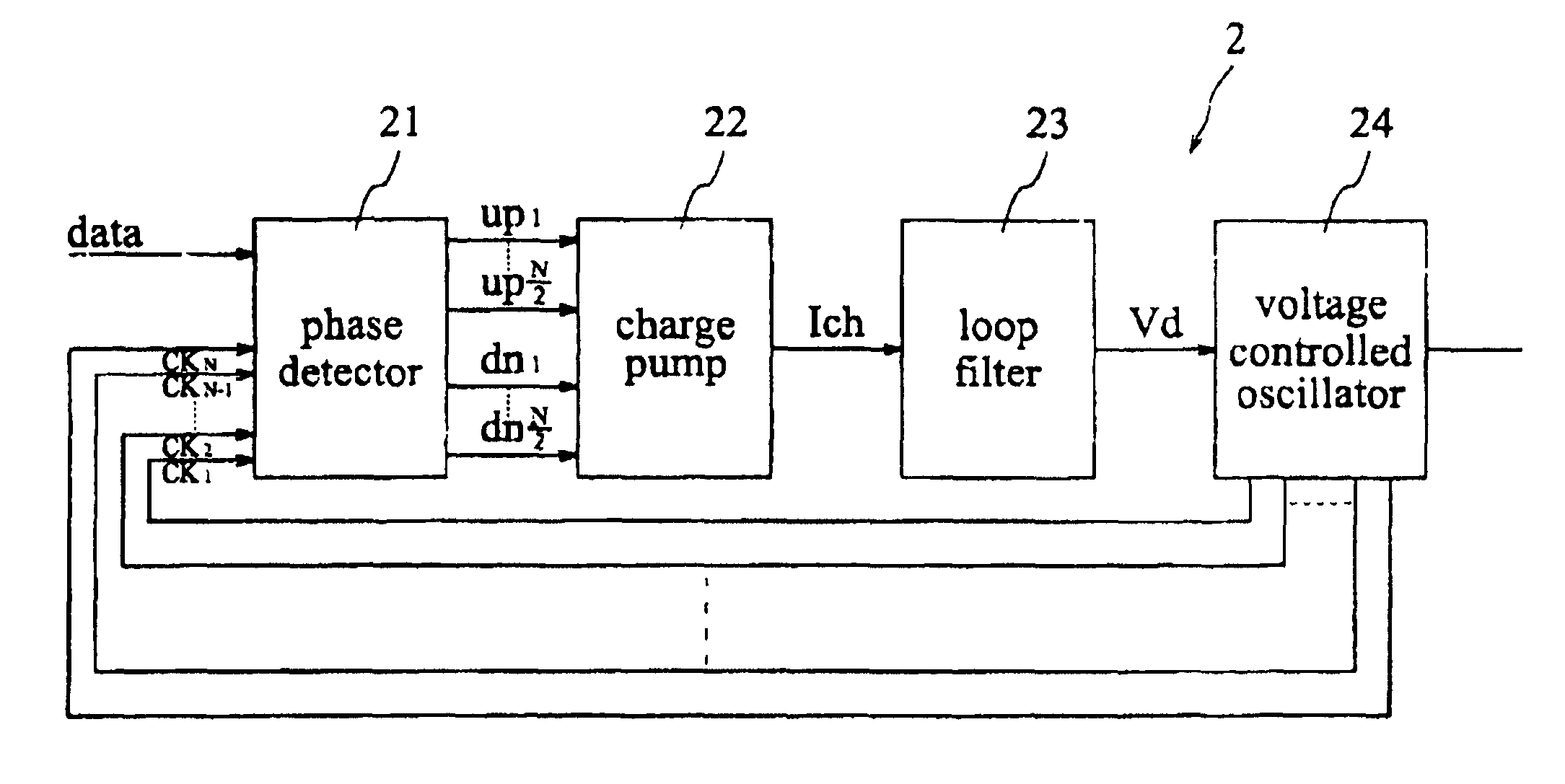

[0030]Firstly, referring to FIG. 5, the multi-phase-locked loop for data recovery in accordance with the invention includes: a phase detector 21, a charge pump 22, a loop filter 23, and a multi-phase VCO 24.

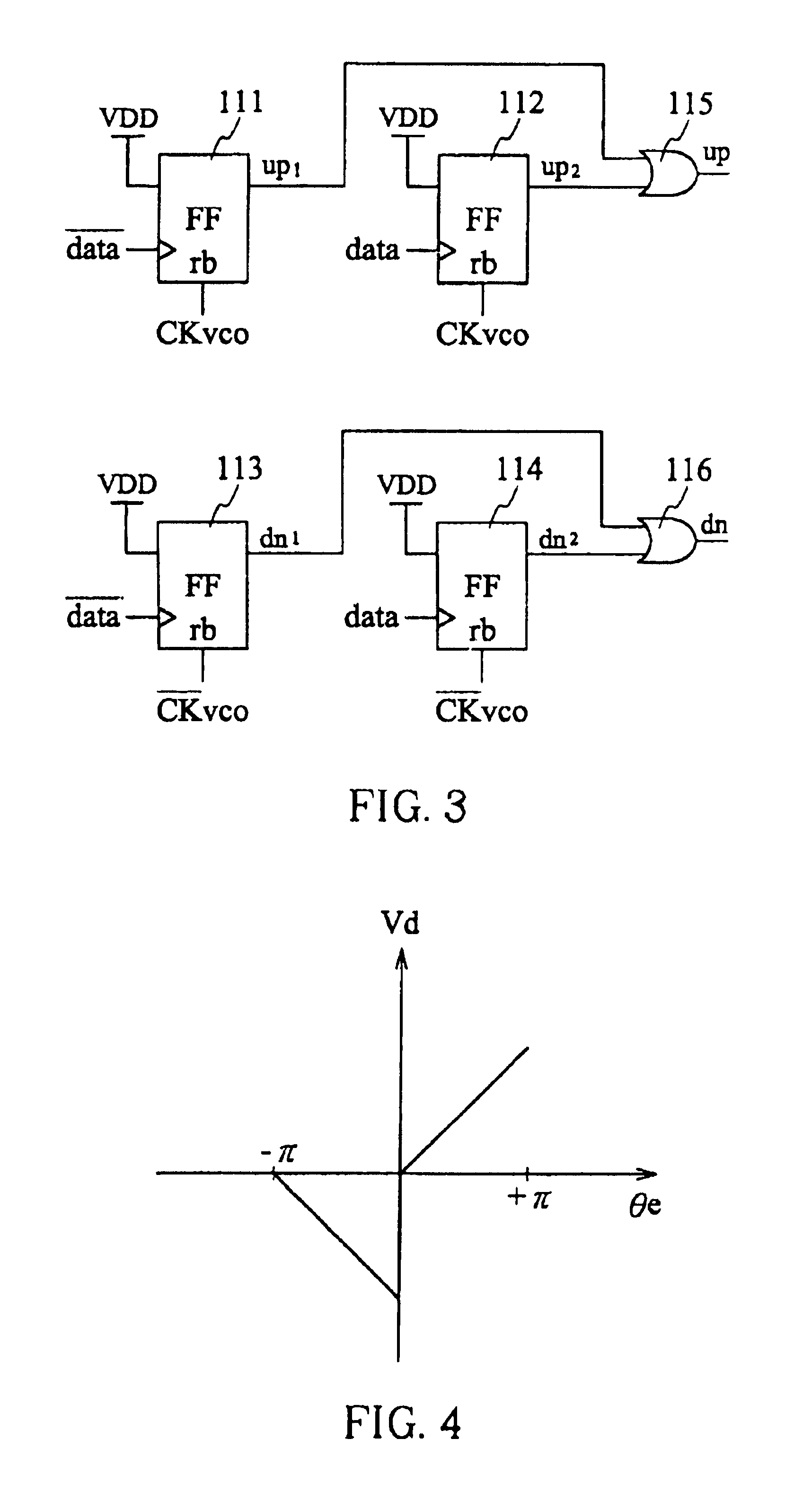

[0031]As illustrated in FIG. 6, the phase detector 21 is constituted by N phase detection units (U1, U2, . . . , UN), wherein N is even and N≧4. The phase detection units (U1, U2, . . . , UN) are connected in cascade configuration, and each phase detection unit contains: a data signal input terminal 61 for receiving a data signal from outside; a clock signal input terminal 62 for receiving multiphase clock signals (CK1, CK2, . . . , CHN) from outside; a delay signal input terminal 63 for receiving the output delay signal from another phase ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More