Method of and apparatus for providing look ahead column redundancy access within a memory

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

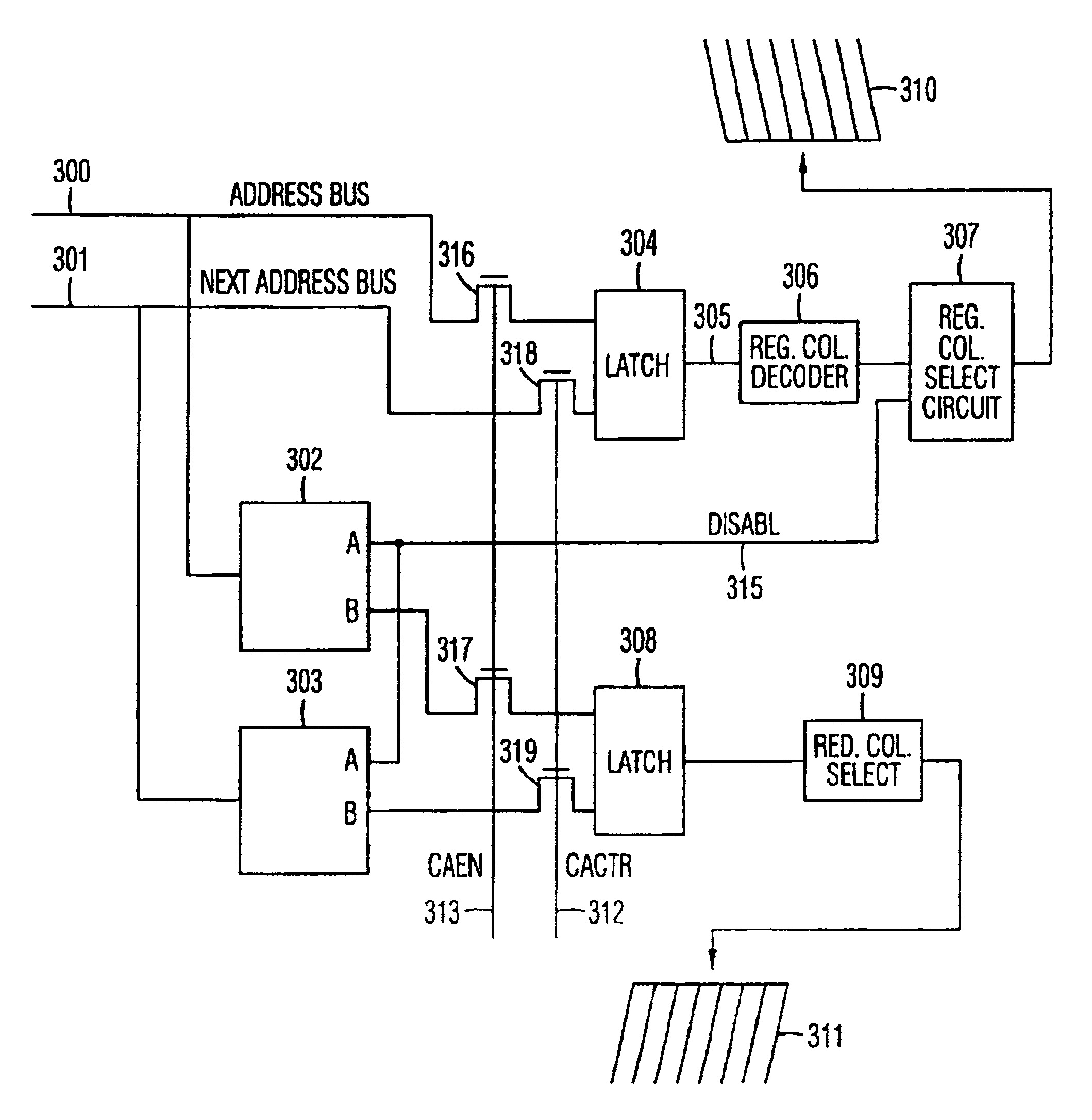

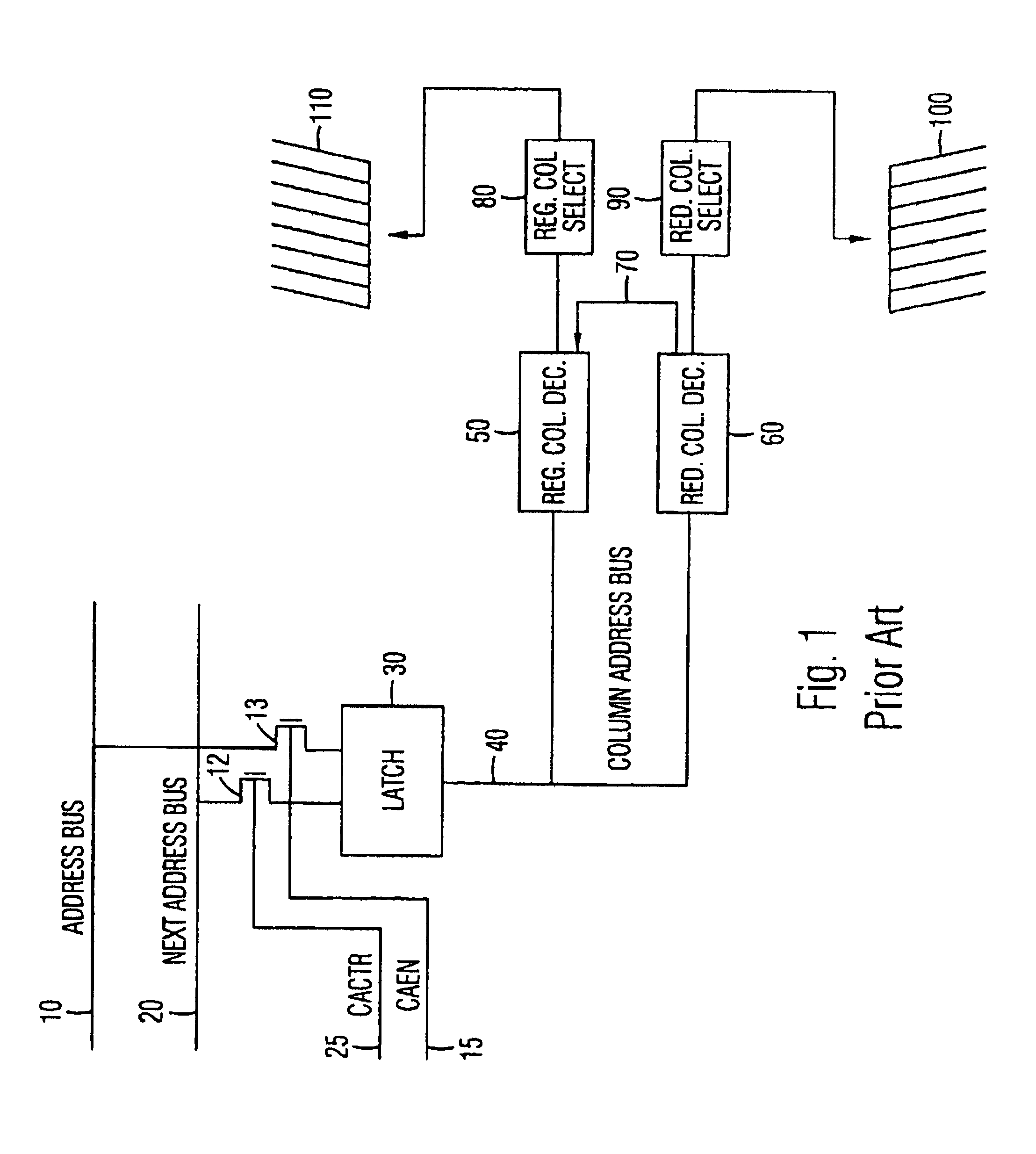

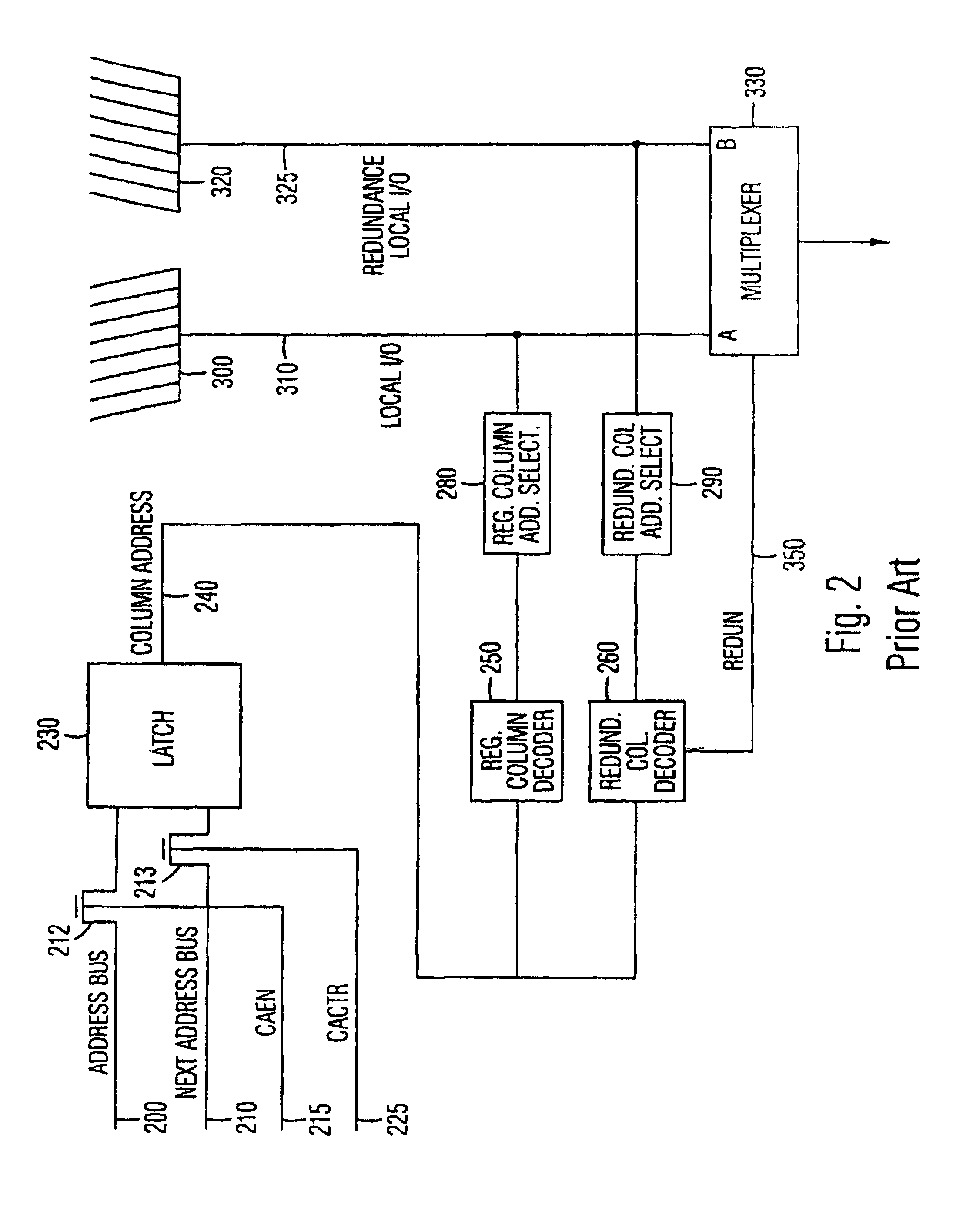

[0021]A look-ahead column redundancy circuit of the present invention includes a main memory pathway and a redundancy pathway in order to minimize memory access time and delays during memory access operations. Addressing information from an address bus and a next address bus is provided to a pair of redundant column decoders. The redundant column decoders decode the addressing information and determine if the addressing information corresponds to an address within the redundant memory array. The decoded information from the redundant column decoders is then provided to a redundancy column pathway as the addressing information from the address bus and the next address bus is provided to a main column pathway. The main column pathway includes a latching circuit, a main column decoder and a main column select circuit. A disabling signal is activated by the redundant column decoders if the addressing information for the current memory access operation corresponds to an address within th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More