Nonvolatile semiconductor memory including multi-threshold voltage memory cells including voltage ranges indicating either an erase state or a two or more program state

a technology of nonvolatile semiconductor memory and memory cells, which is applied in the field of semiconductor memory devices, can solve the problems of large fluctuations of increase in the peak current of the write operation, and increase in the average power consumption, so as to reduce the peak current and average power consumption in the write operation, and minimize the threshold voltage attributed to word line disturbance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029]Now, various embodiments of the present invention will be described with reference to the drawings in relation to the case where the invention is applied to a flash memory which is capable of storing a quaternary value in one memory cell.

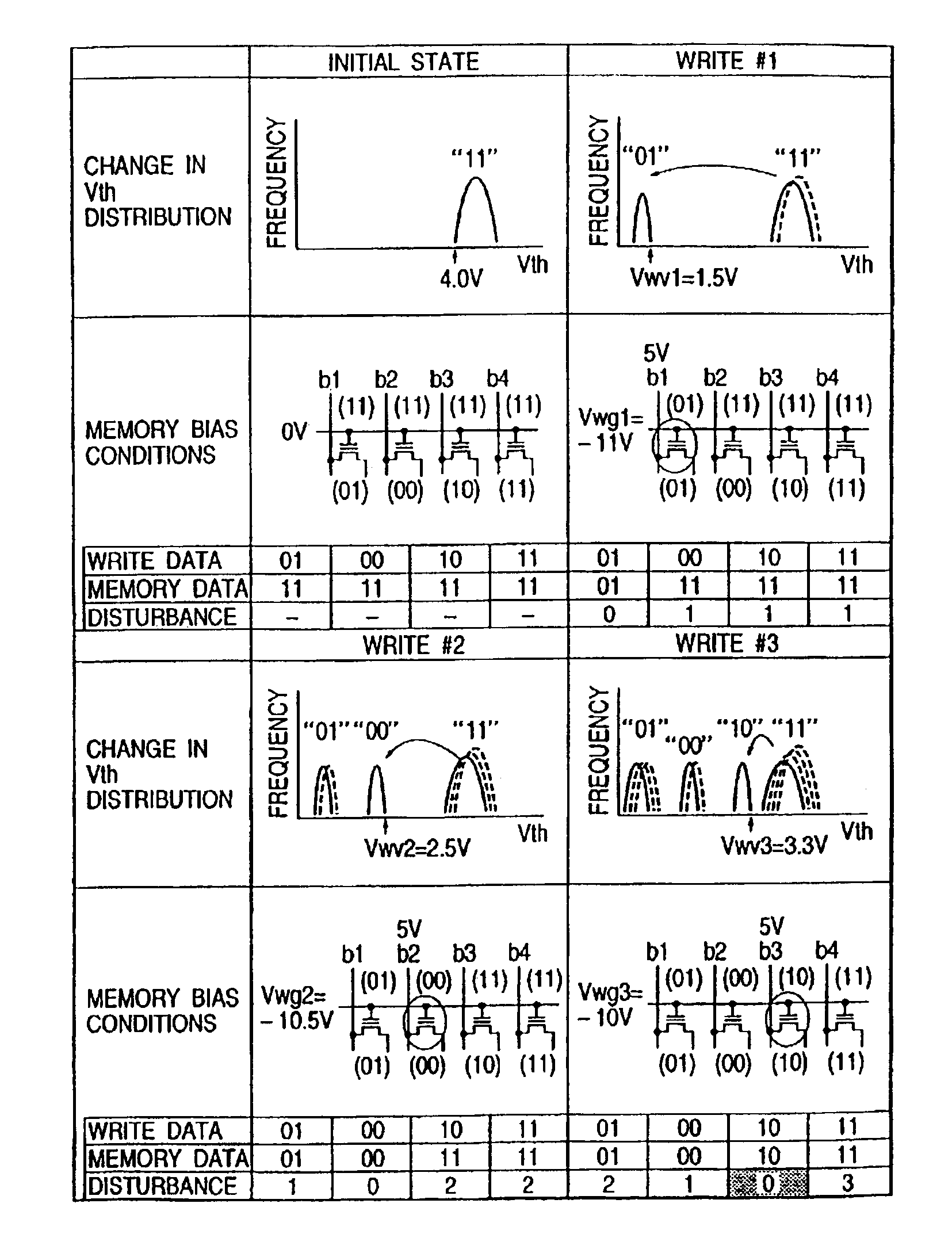

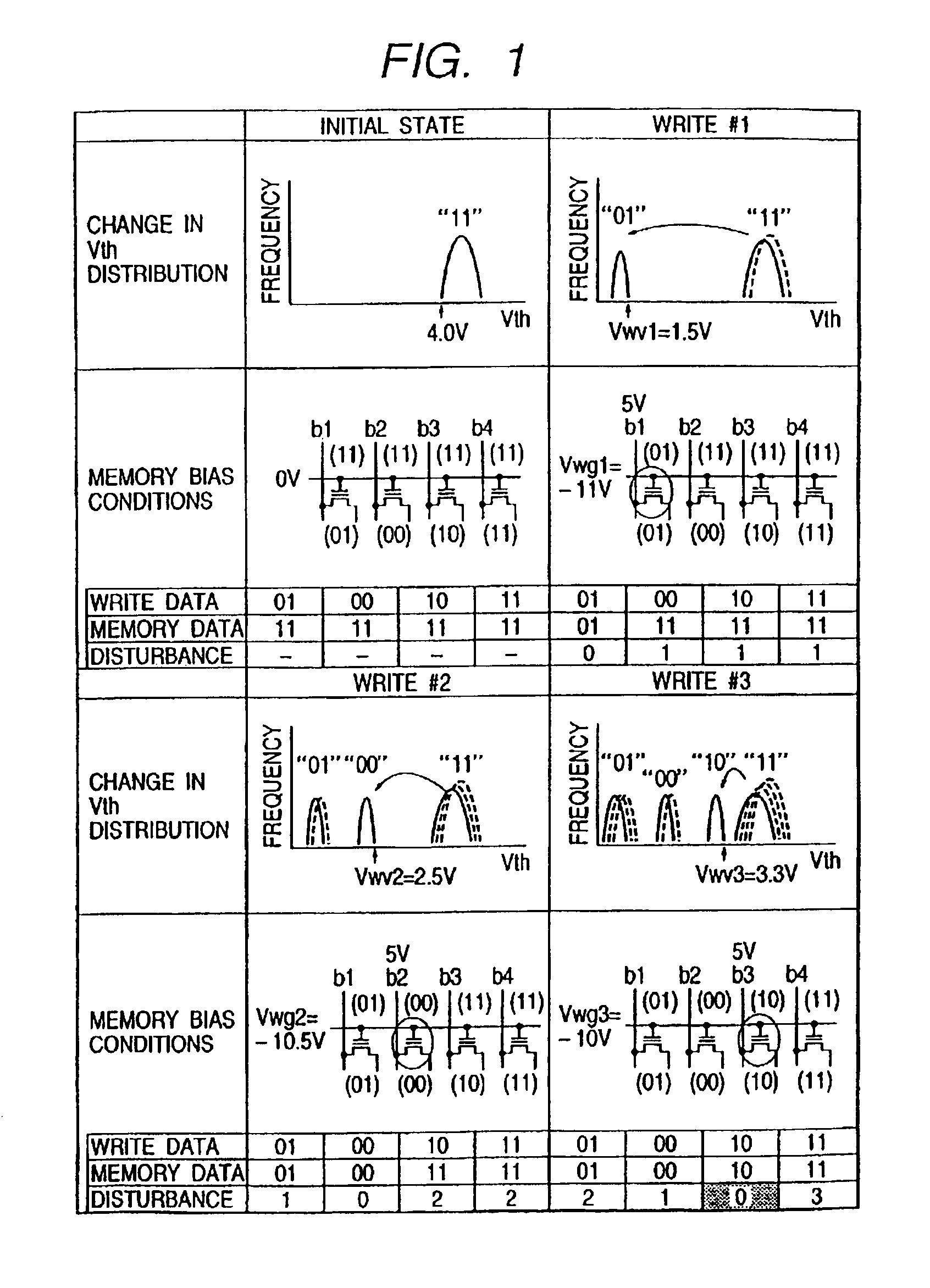

[0030]FIG. 1 illustrates the data writing sequence of a flash memory in one embodiment of the present invention. In this embodiment, all the memory cells thereof are brought into the threshold voltage region (the threshold voltages are at least 4 V and the stored data is “11”) of the erase level prior to the writing operation. Subsequently, as shown in FIG. 1, data is written into the memory cell (stored data is “01”) whose threshold voltage region (the threshold voltage is higher than 0 V and not higher than 1.4 V) is the farthest (lowest) from the erase level. Thereafter, the data is written into the memory cell (stored data is “00” whose threshold voltage region (the threshold voltage is not lower than 1.6 V and not higher than 2.4 V) is th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More