Relay base plate and multilayer printed wiring board

A relay substrate, multi-layer printing technology, applied in the direction of circuits, electrical components, electrical solid devices, etc., can solve the problems of difficult to carry high frequency, high performance, high ceramic resistance value, high dielectric constant, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

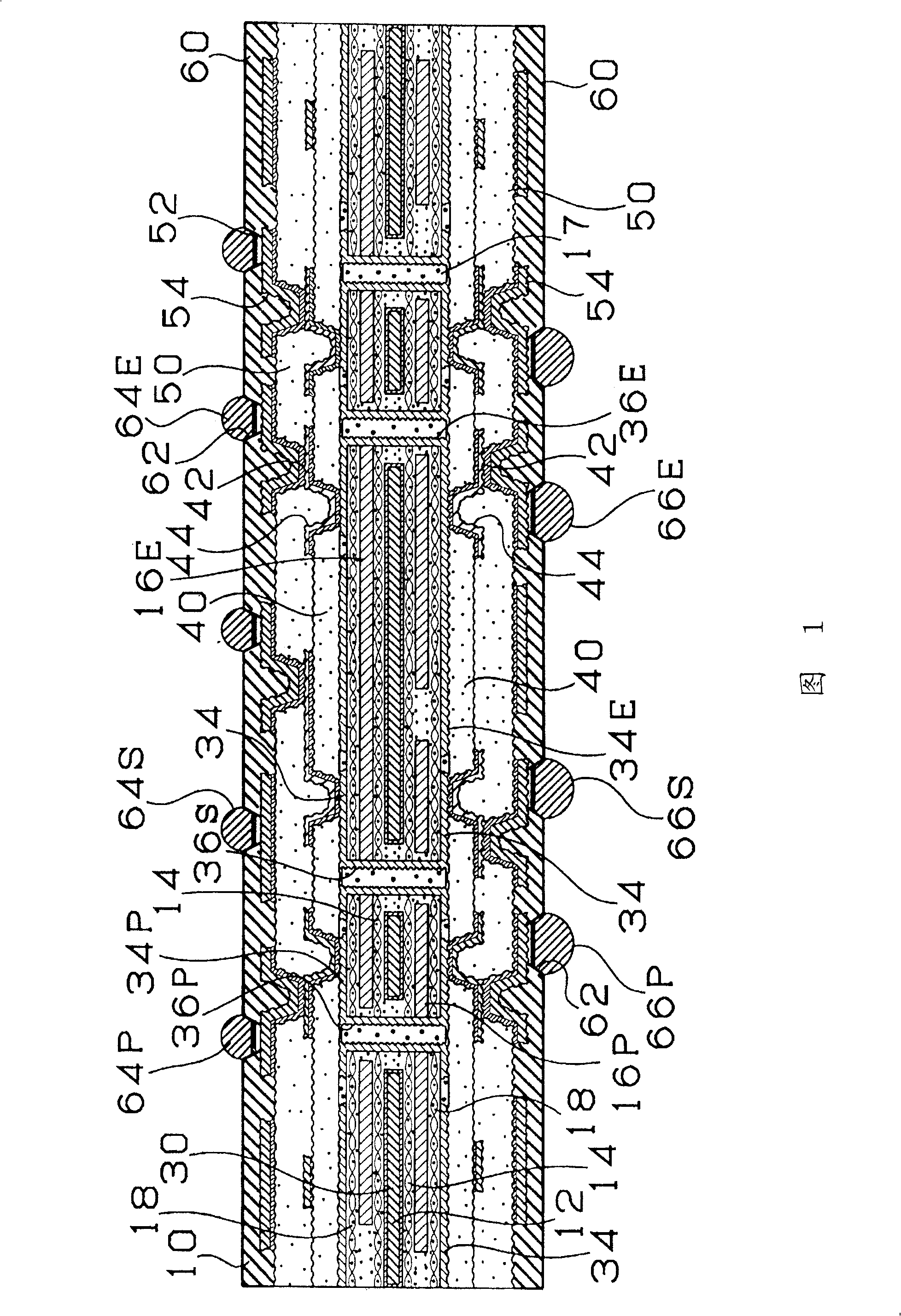

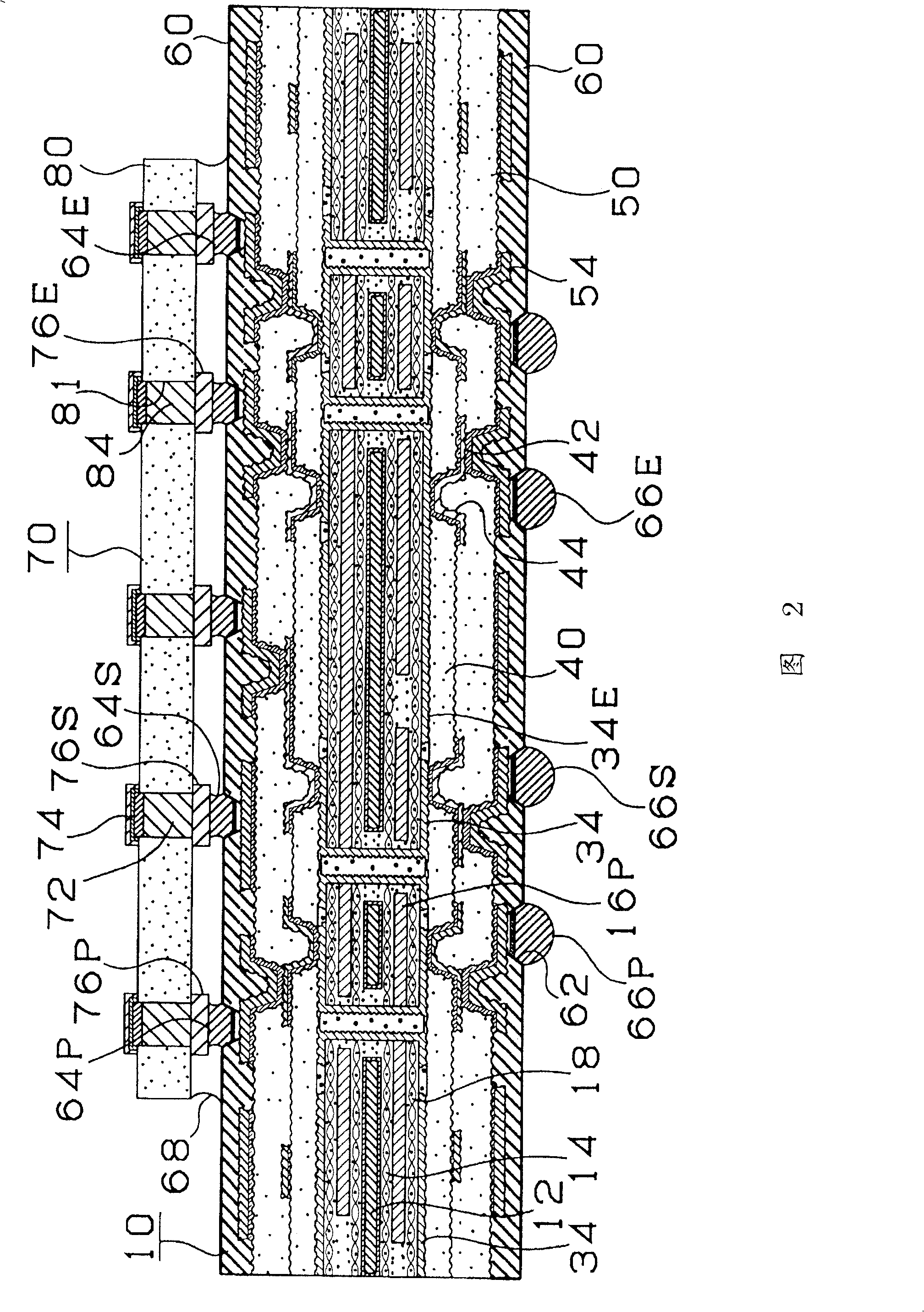

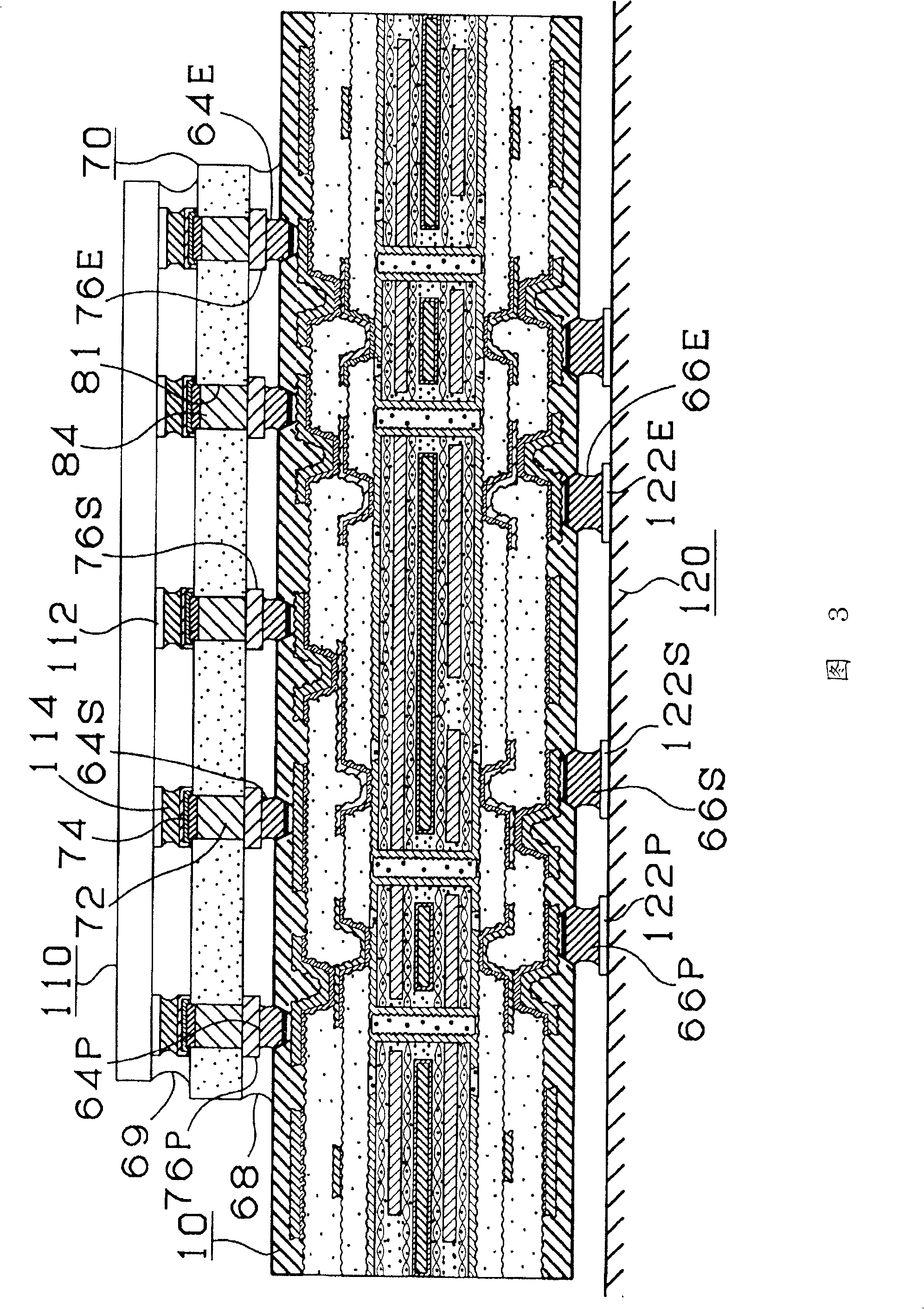

Embodiment 1

[0059]In the resin package substrate 10 of the first embodiment, the power supply capability to the IC chip 110 can be improved by using the conductor layers 34P and 16P as power supply layers. Therefore, when the IC chip 110 is mounted on the package substrate 10, the loop inductance from the IC chip 110 to the substrate 10 to the sub-board 120 side power supply can be reduced. Therefore, since the power shortage during the initial operation becomes smaller, it is less likely to cause a power shortage. Therefore, even if an IC chip in the high-frequency field is mounted, it will not cause erroneous operation or errors during the initial startup. In addition, by using the conductor layers 34E and 16E as ground layers, noise is not superimposed on the signal and power supply of the IC chip, and the occurrence of erroneous operations or errors can be prevented. In addition, by installing a capacitor not shown in the figure, the power stored in the capacitor can be used in an aux...

Embodiment 2

[0090] [Example 2] Young's modulus = 55GPa, external dimensions = 32mm × 32mm, relay substrate thickness = 64μm

[0091] For the relay substrate of Example 2, in Example 1, the substrate thickness of the starting material was set to 64 μm. Therefore, the laser conditions for forming the through holes were changed to the conditions shown in the table below. In addition, the plating time for filling the conductive agent in the through holes is changed according to the thickness of the substrate. Other than that, it was the same as Example 1.

[0092] 【Table 2】

[0093] "Laser Conditions"

Embodiment 3

[0095] [Example 3] Young's modulus = 55GPa, external dimensions = 32mm × 32mm, relay substrate thickness = 100μm

[0096] For the relay substrate of Example 3, in Example 1, the substrate thickness of the starting material was set to 100 μm. Therefore, the laser conditions for forming the through holes were changed to the conditions shown in the table below. In addition, the plating time for filling the conductive agent in the through hole is changed according to the thickness of the substrate. Other than that, it was the same as Example 1.

[0097] 【table 3】

[0098] "Laser Conditions"

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More