Ferroelectric field effect transistor storage device structure and preparation method

A technology of electric field effect and storage devices, which is applied in the fields of electric solid-state devices, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve problems such as excessive working voltage, and achieve the effects of overcoming poor interface, good storage performance, and simple process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

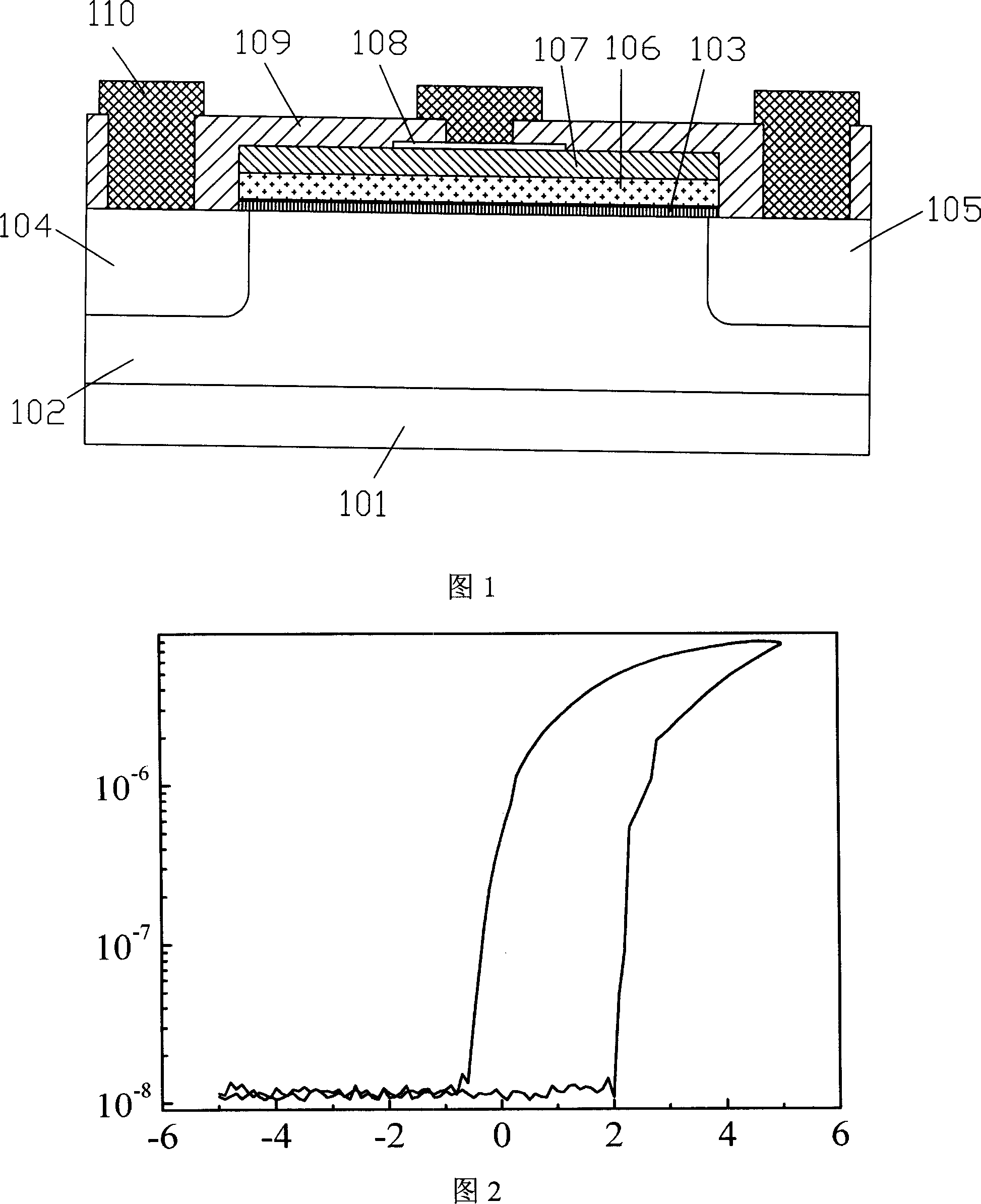

[0040] See Figure 1.

[0041] The ferroelectric field effect transistor of the present invention is composed of a substrate, a source region, a drain region and a gate region between the source region and the drain region, and the substrate is an n-type single crystal silicon wafer 101 with a (100) crystal orientation. After implantation to form the p-well 102, a layer of SiO is thermally oxidized on the surface 2 103 as an insulating layer.

[0042] The invention also includes directly forming p-channel transistors on n-type single-crystal silicon wafers.

[0043] Ferroelectric field effect transistor storage device structure, including Pt upper electrode 108, n + source region 104 and n + Drain region 105, layers from top to bottom are: PZT ferroelectric film 107, polysilicon 106, SiO 2 The insulating layer 103 , the p well 102 and the Si substrate 101 , and the upper electrode 108 are located on the PZT ferroelectric film 107 .

[0044] The preparation method of the a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More