Digital clock frequency multiplier

A digital clock and frequency multiplier technology, applied in the field of digital clock frequency multipliers, can solve the problems of consumption, high locking time, and the frequency of the input clock signal cannot be changed rapidly.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0013] The following detailed description, taken in conjunction with the accompanying drawings, is intended to describe presently preferred embodiments of the invention and is not intended to represent the only forms of implementing the invention. It is to be understood that the same or equivalent function may be accomplished by different embodiments which are intended to encompass the spirit and scope of the invention.

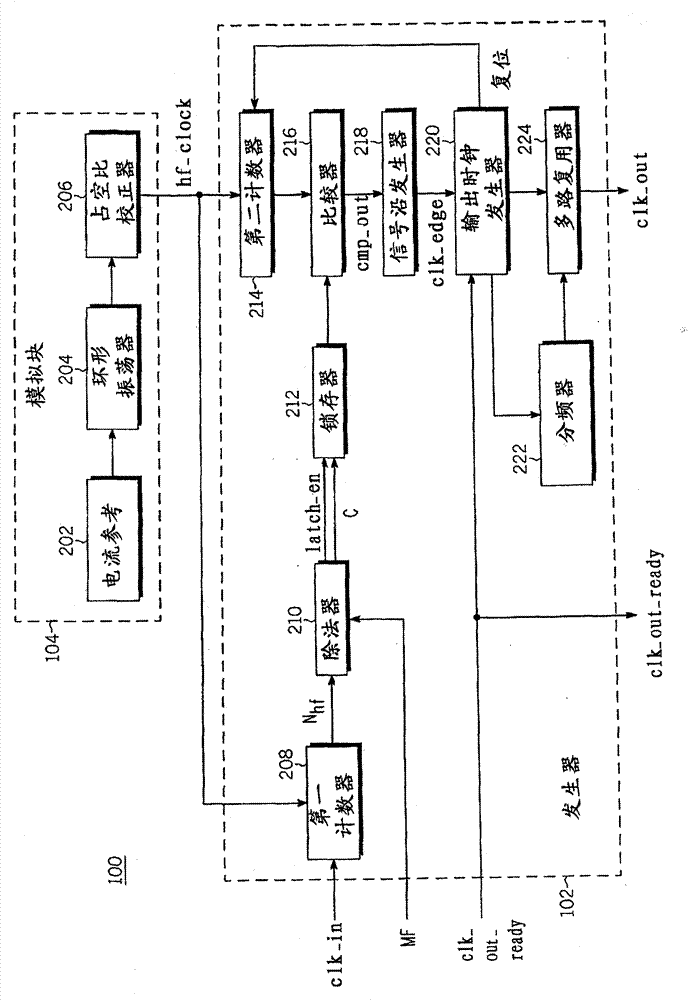

[0014] now refer to figure 1 , is a structural diagram of a digital clock frequency multiplier 100 according to an embodiment of the present invention. The digital clock multiplier 100 includes a generator 102 and an analog block 104 . with time period T clk_in The input clock signal “clk_in” of is input to the generator 102 . The generator 102 receives the input clock signal clk_in and the high-frequency digital signal "hf_clk" generated by the analog block 104, and one cycle T of the input clock signal clk_in clk_in Counting of the number of cycles of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com