'Soft error' suppress circuit based on isolate method

A technology for suppressing circuits and soft errors, applied in information storage, static memory, digital memory information, etc., can solve the problem of "soft error" suppression effect is small

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

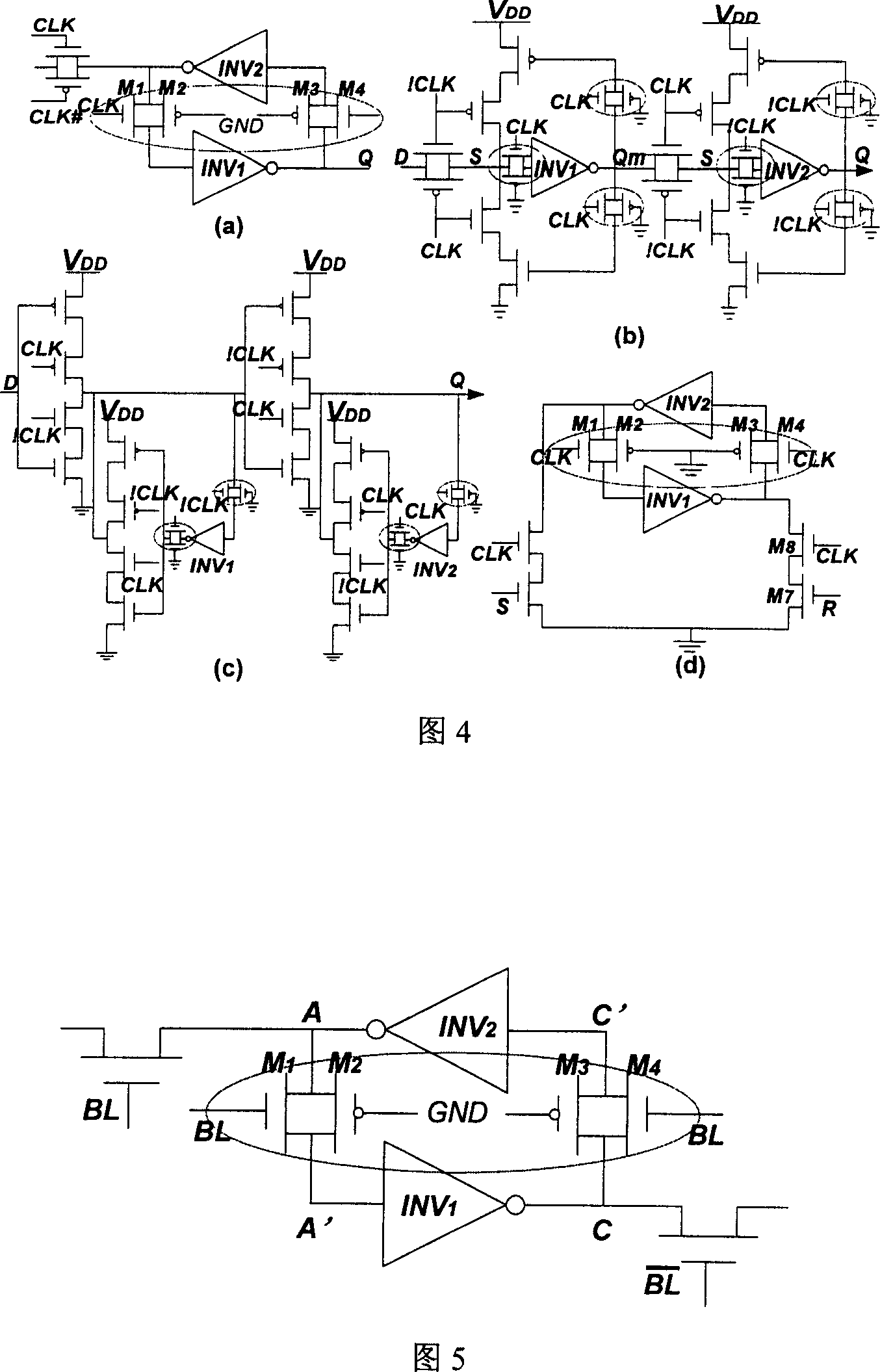

Embodiment Construction

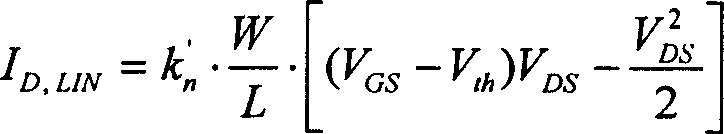

[0031] The circuit of the present invention can be slightly improved and obtained from the existing SRAM unit circuit: two transmission gate units are added, wherein, the grid of the NMOS transistor of the transmission gate is connected to the control line of the Bit line; and the grid of the PMOS transistor is grounded, Leave it normally open. In addition, there is no need to make any changes to the original circuit.

[0032] When this circuit is applied in a SRAM cell, it is shown in the figure. The work of the circuit is divided into two states: access state (AccessState) and hold state (Keep State), as shown in Figure 1. In the access state, the control signal makes the transmission gate turn on, and the data is stored or read normally; in the hold state, the NMOS transistor of the transmission gate is turned off, and the PMOS transistor is turned on. A sub-hit is equivalent to connecting an inrush current source at point A(C), as shown in Figure 2. The instantaneous im...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More