Stacked chip package using warp-proof insulative material and method of manufacturing the same

A technology of insulating layer and substrate material, which is applied in semiconductor/solid-state device manufacturing, auxiliary products for massage, and equipment for compressing reflection points, etc. It can solve problems such as fracture and peeling, and affect the reliability of yield devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0070]The present invention will now be described more fully with reference to the accompanying drawings, in which preferred embodiments of the invention are shown. This invention may, however, be embodied in different forms and should not be construed as limited to the example embodiments set forth herein. In the drawings and related descriptions, if a first layer is referred to as being "on" another layer, the first layer can be directly on the other layer, or intervening layers may be present. Like numbers refer to like elements throughout the specification.

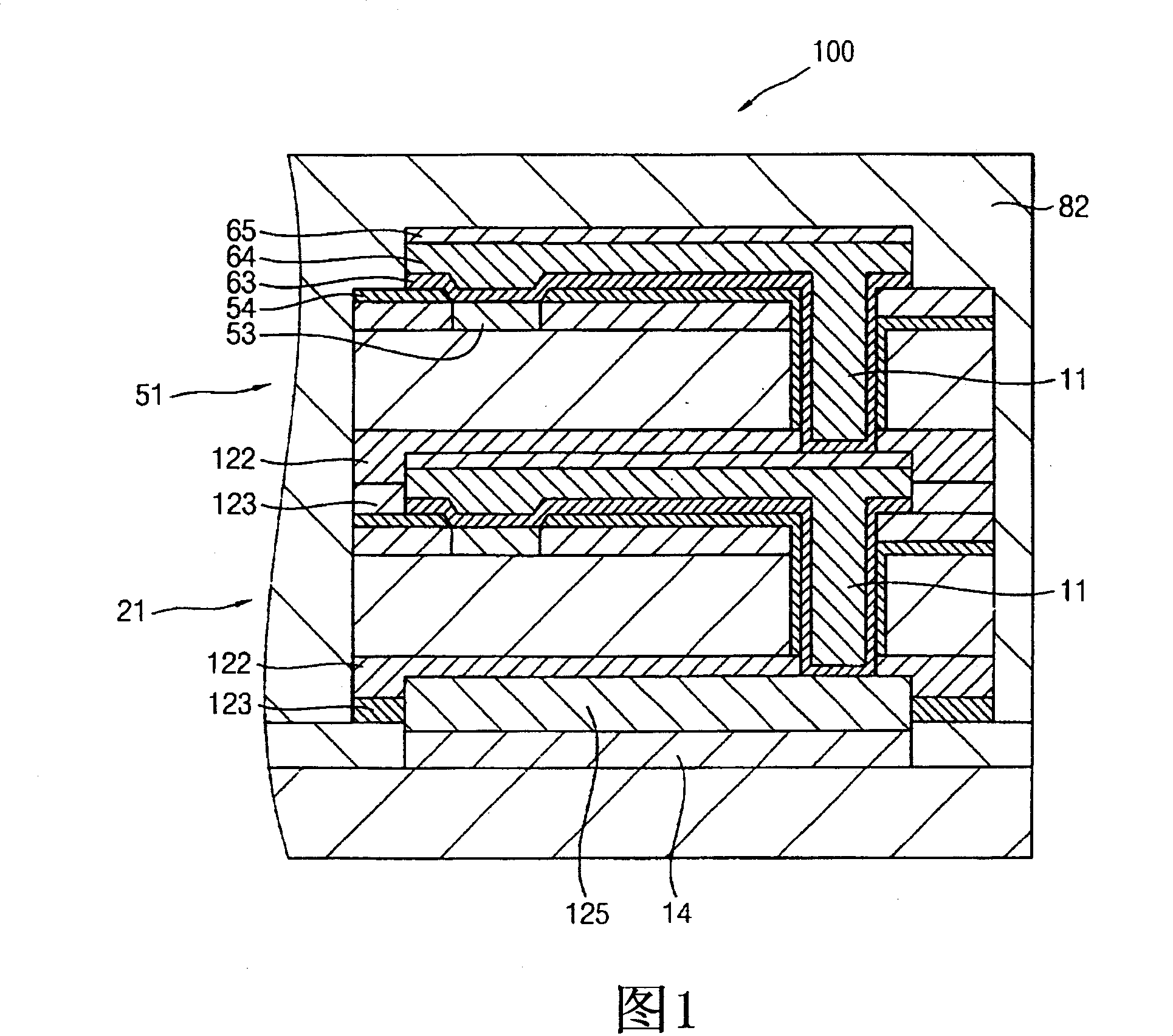

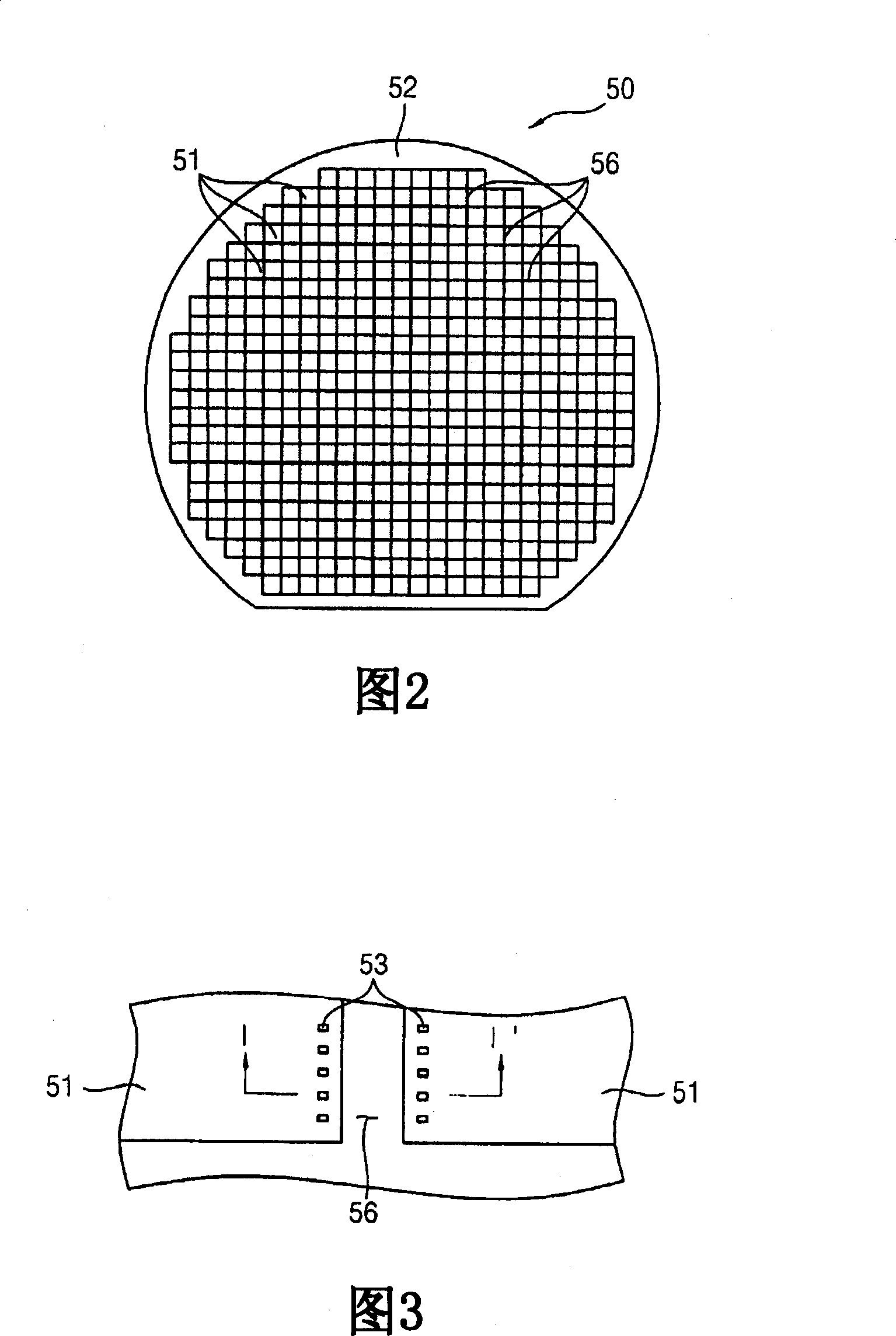

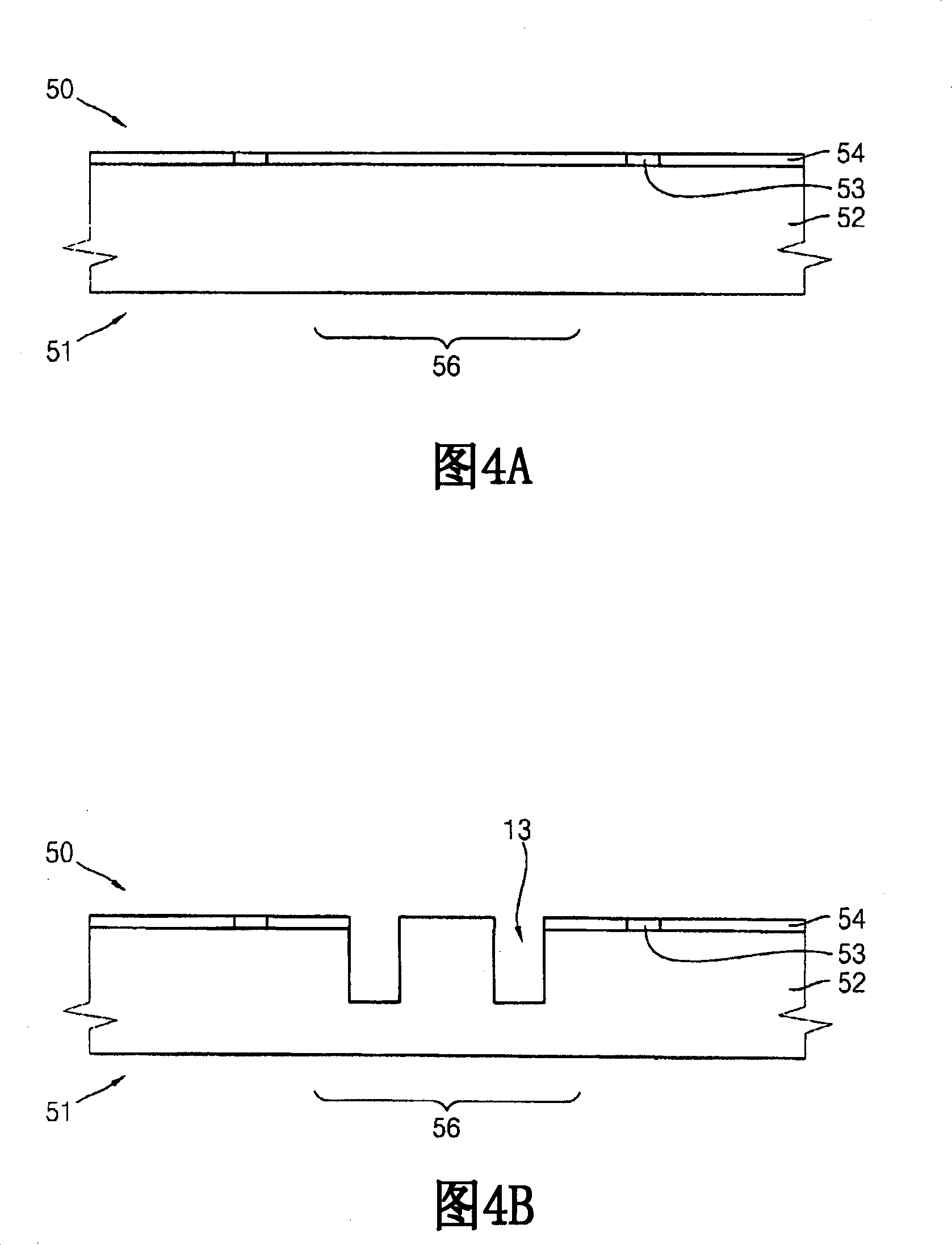

[0071] FIG. 1 is a cross-sectional view of a stacked die package according to the present invention. The stacked chip package according to the embodiment of FIG. 1 includes a printed circuit board 10 on which a chip stack including a first chip 21 and a second chip 51 is mounted. Each of the first and second chips 21, 51 includes a plurality of bond pads 53 for exchanging signals with locations off the chip and cond...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More