MPU FPGA verification device supporting stochastic instruction testing

A microprocessor and verification device technology, applied in the field of microprocessor design verification, can solve problems such as not providing support, and achieve the effect of fast test speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

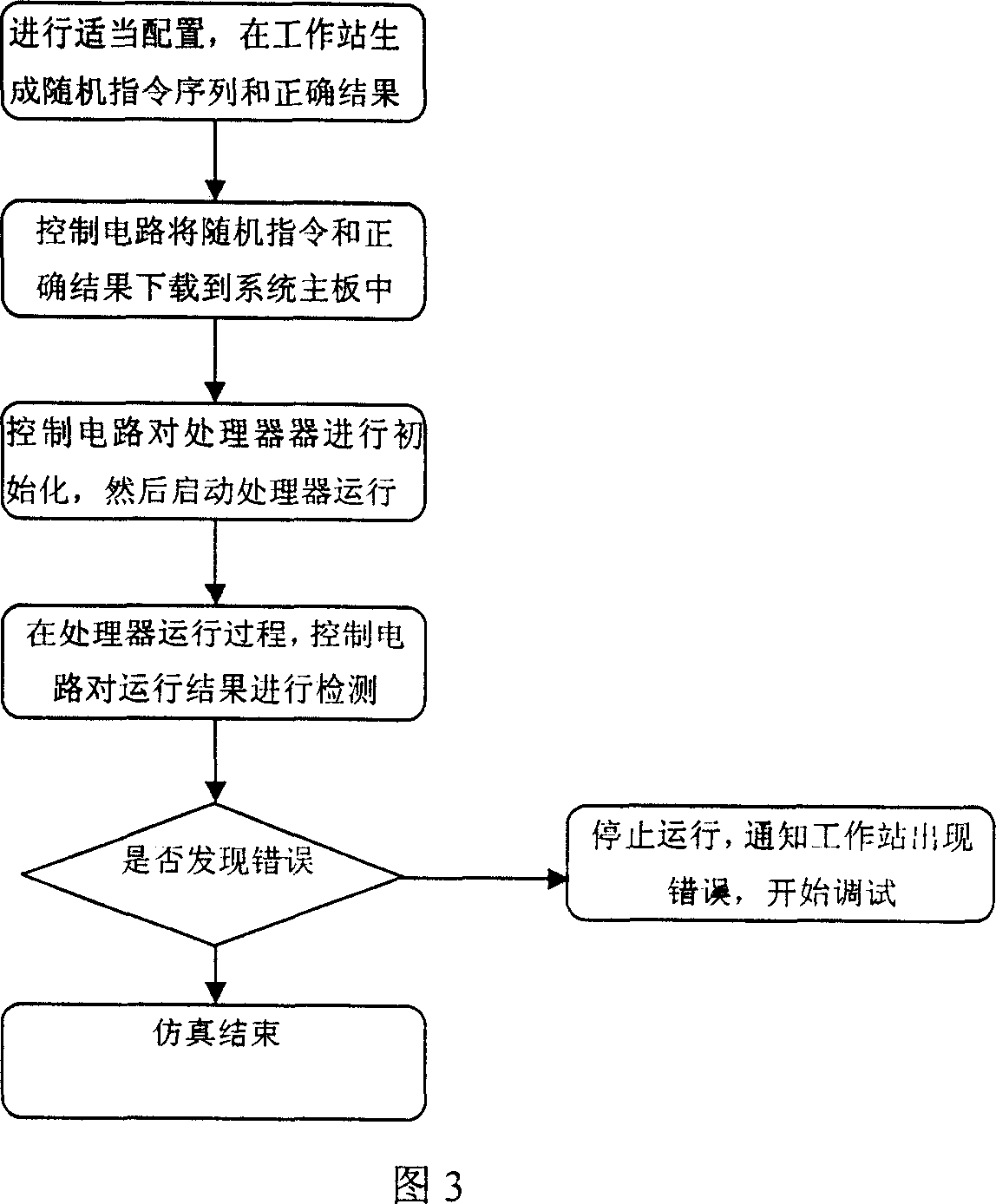

[0032] Below in conjunction with accompanying drawing and specific embodiment the present invention is described in further detail:

[0033] In this embodiment, taking the design verification of the Loongson-2 microprocessor as the verification object, the microprocessor FPGA verification device supporting random instruction testing of the present invention is described in detail. According to the detailed description of this embodiment, those skilled in the art are capable of manufacturing a device for performing design verification on different microprocessors.

[0034] The production of the microprocessor FPGA verification device is divided into two main stages, the first is the production of the system main board, and then the logic design of the main control circuit on the main board.

[0035] Production of the system board:

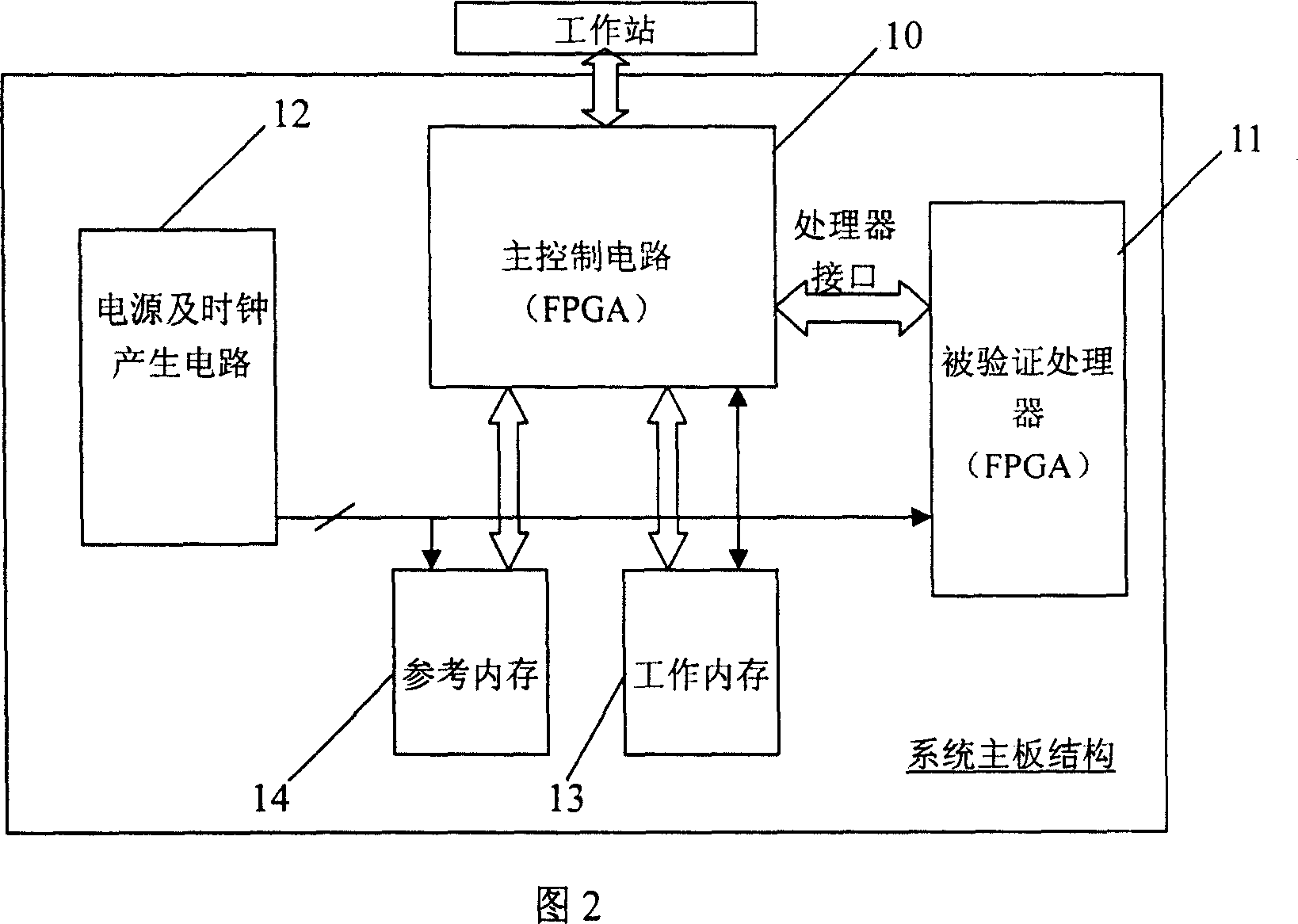

[0036] The structure of the system board is shown in Figure 2. The mainboard can ensure the hardware environment for the correct operation of the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More