Test system which

A technology for testing systems and chips to be tested, which is applied in the direction of electronic circuit testing, measuring electricity, measuring devices, etc., can solve the problems of long time-consuming, etc., and achieve the effect of improving the testing speed and prolonging the service life

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

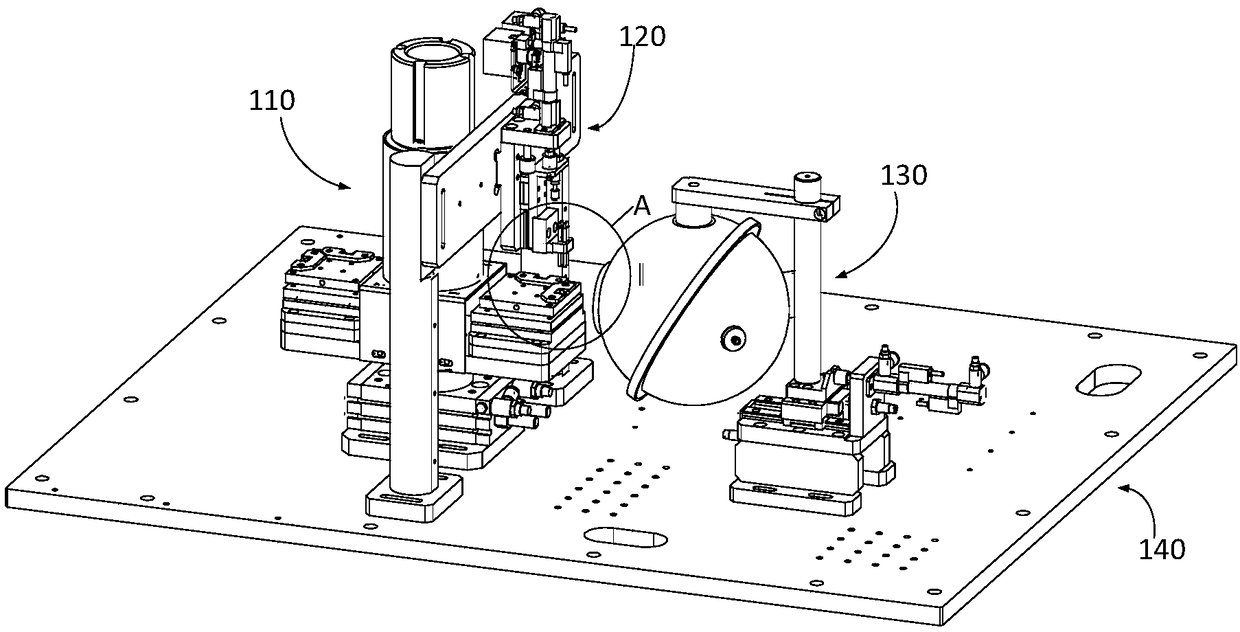

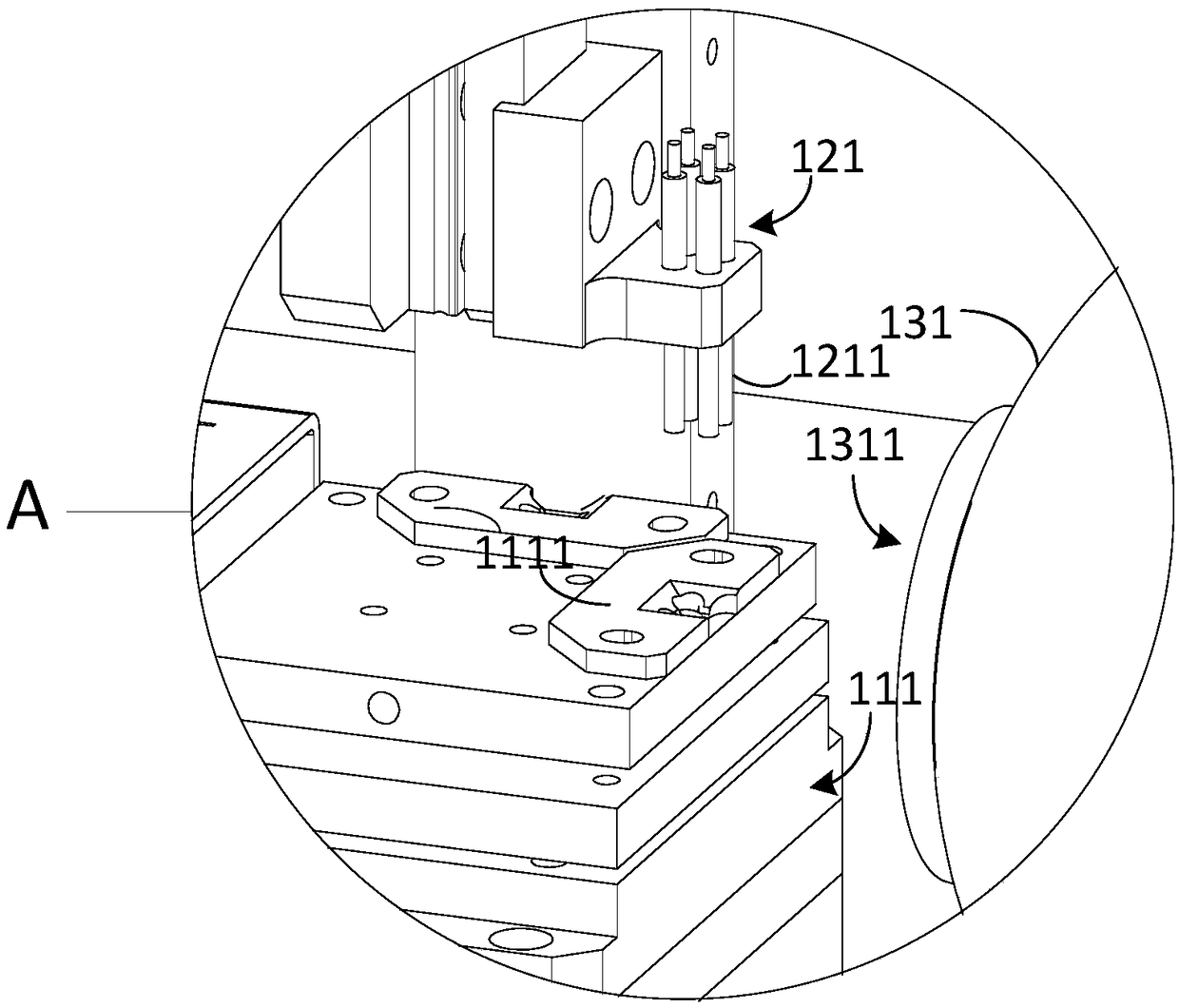

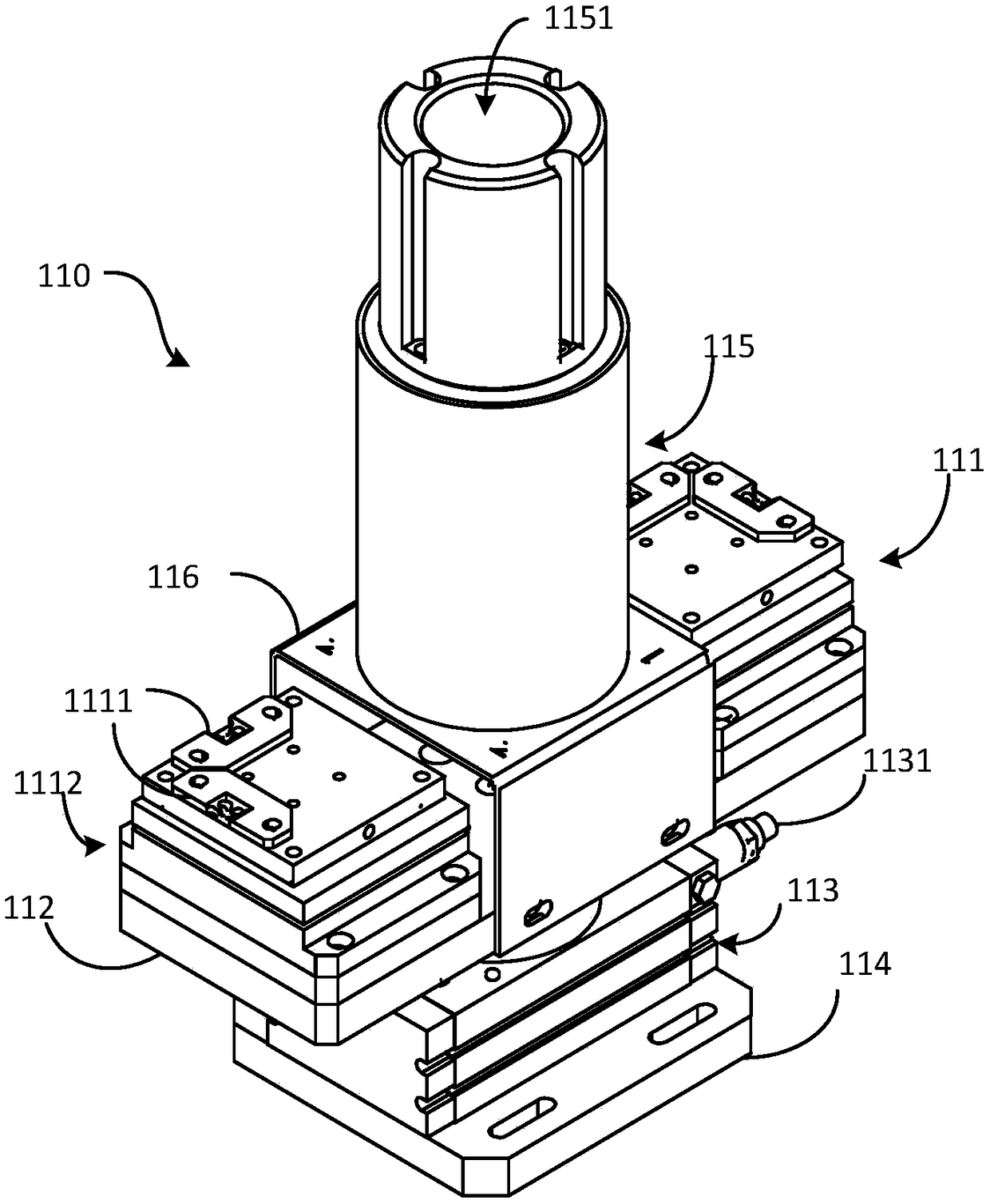

[0026] The following will clearly and completely describe the technical solutions in the embodiments of the present application. Obviously, the described embodiments are only some of the embodiments of the present application, rather than all the embodiments. Based on the embodiments in this application, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the scope of protection of this application.

[0027] It is worth noting that the directional terms mentioned in this application, for example, "upper", "lower", "front", "rear", "left", "right", "inner", "outer", " "side", etc., are only referring to the directions of the attached drawings. Therefore, the direction terms used are for better and clearer description and understanding of the present application, rather than indicating or implying that the referred device or element must have a specific orientation. , are constructed and operate in a particular orienta...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More