Multiply adding up device

A technology of multiply-accumulate and add units, which is applied in the field of multiply-accumulate devices, can solve problems such as being difficult to keep up with the operating frequency of DSP, and achieve the effects of satisfying the limitation of bit width, reducing time delay, and reasonable structure arrangement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] The present invention can be illustrated in detail by the following drawings and descriptions thereof.

[0043] Detailed Description:

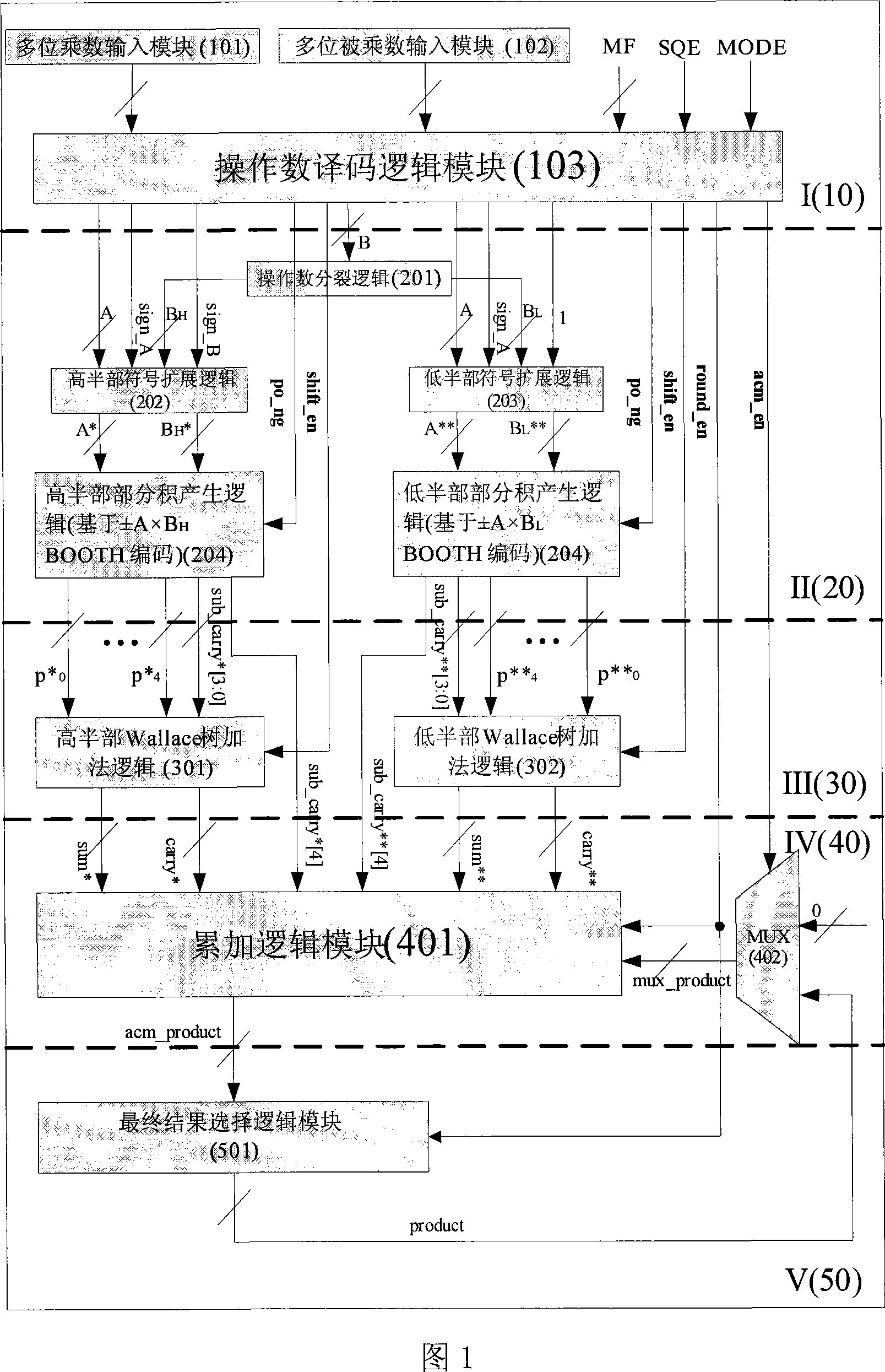

[0044] figure 1:

[0045] Multi-bit data A, B H , B L , one bit of data sign_A, sign_B, po_ng, acm_en, shift_en, round_en is the output of the operand decoding unit module 10.

[0046] multi-bit data p * 0 ,p * 4 ,p ** 0 ,p ** 4 , sub_carry * [3:0], sub_carry ** [3:0], one bit data sub_carry * [4], sub_carry ** [4] Generates the output of the cell module 20 for the partial product.

[0047] Multi-bit data sum* 、carry * 、sum ** 、carry ** is the output of the Wallace tree addition unit module 30.

[0048] The multi-bit data mux_product and acm_product are outputs of the accumulation unit module 40 .

[0049] The multi-bit data product is the output of the final result unit module 50

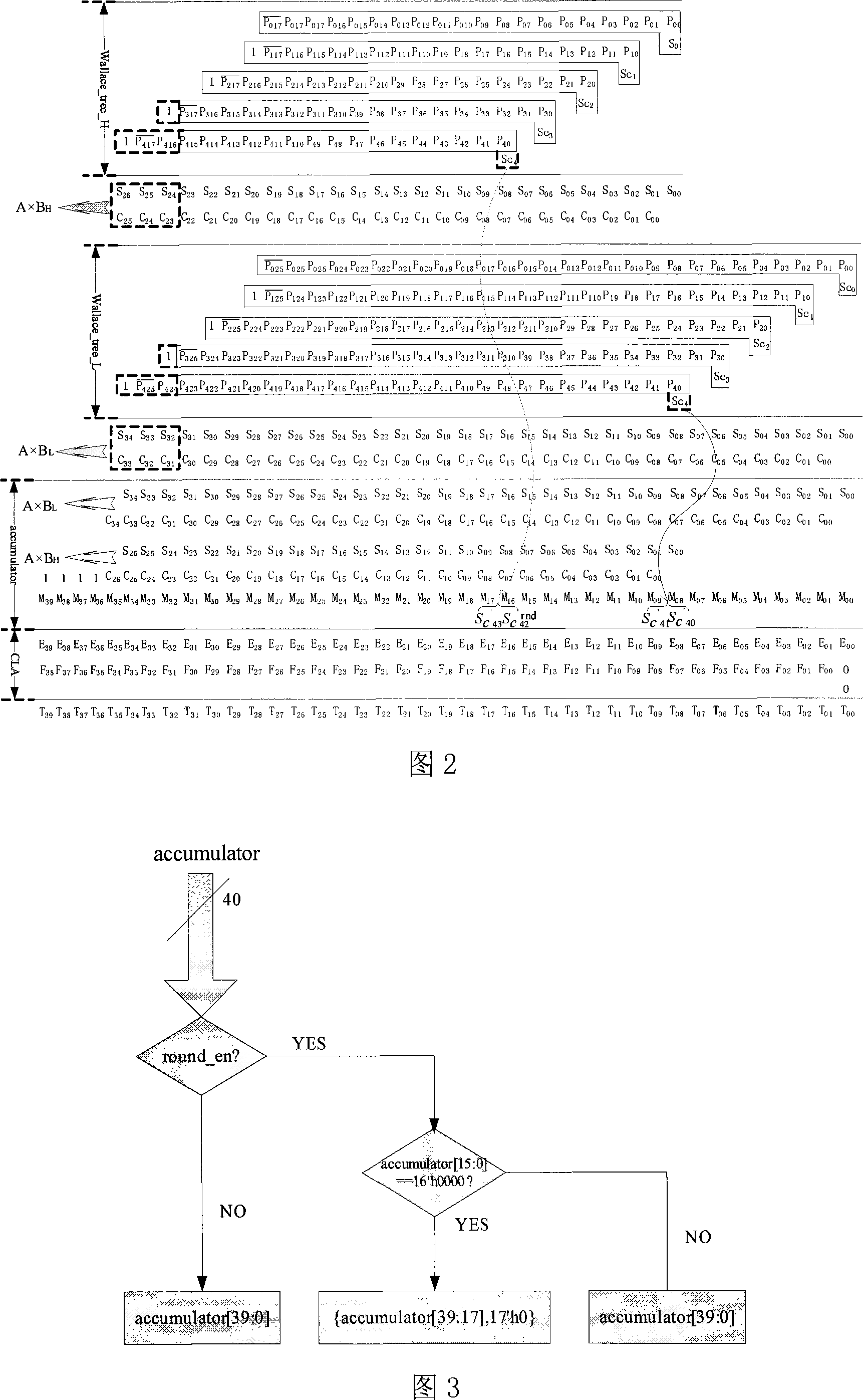

[0050] figure 2:

[0051] For the high half Wallace tree addition logic:

[0052] The specific bit of the partial product of Pxy, whe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More