Semiconductor packaging structure with common type wafer holder

A chip seat and semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid device parts, electric solid devices, etc., can solve the problems of unbalanced mold flow, no structure of general products, lack of fixation around the wafer, etc., to achieve increased integration intensity effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 Embodiment

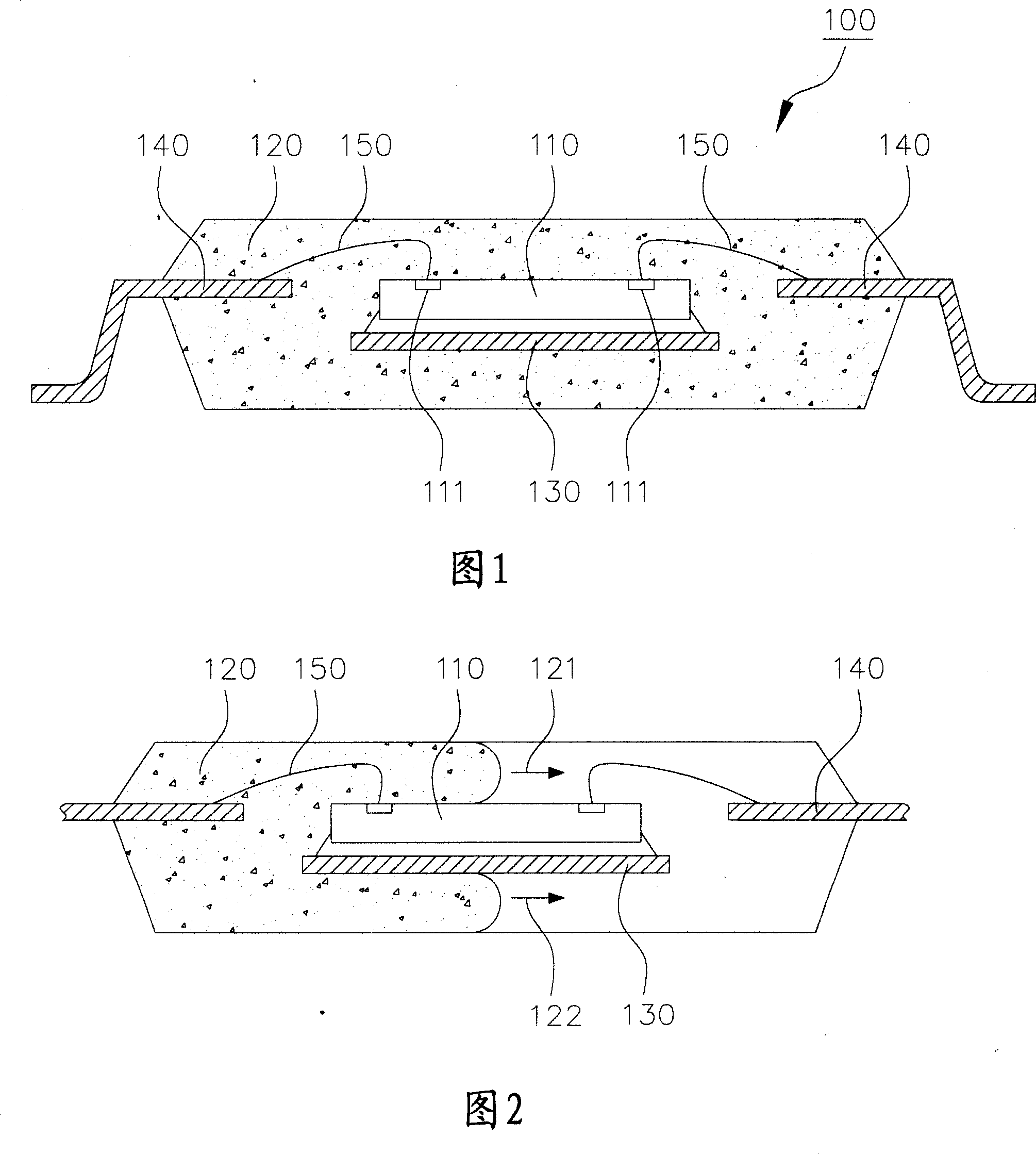

[0057] According to the first embodiment of the present invention, a semiconductor package structure with a common chip holder is disclosed, which can package chips of different sizes in the same lead frame structure without the problem of unbalanced mold flow between upper and lower molds.

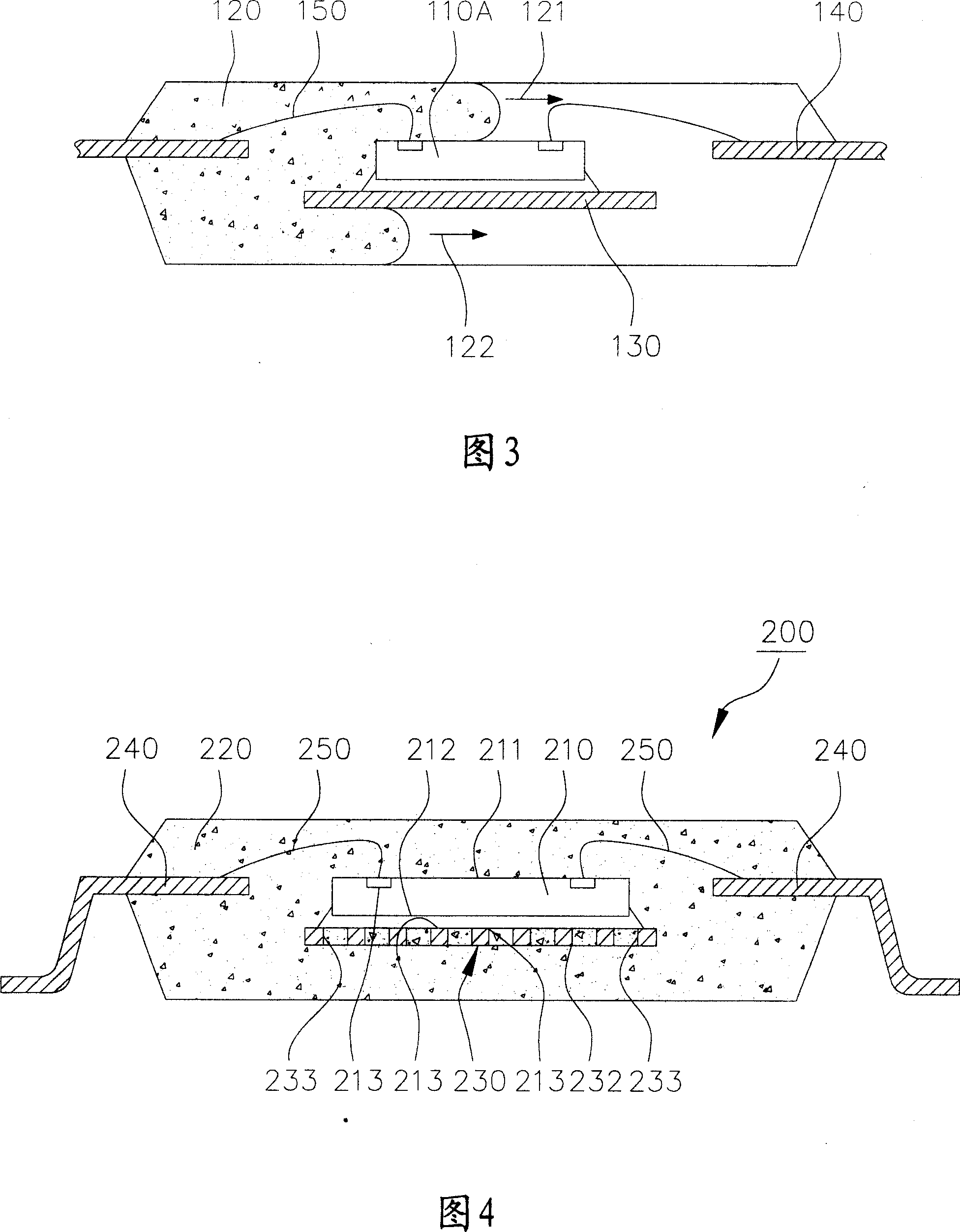

[0058] Please refer to FIG. 4 and FIG. 5. FIG. 4 is a schematic cross-sectional view of a semiconductor package structure with a shared wafer seat according to the first specific embodiment of the present invention. FIG. 5 is a schematic cross-sectional view according to the first specific implementation of the present invention. For example, the schematic diagram of the lead frame of the semiconductor package structure. As shown in FIG. 4 , a semiconductor package structure 200 with a common chip holder mainly includes a lead frame, a chip 210 and a molding compound 220 .

[0059] Please refer to FIG. 5, the above-mentioned lead frame has a shared chip holder 230 and a plurality of pins ...

no. 2 Embodiment

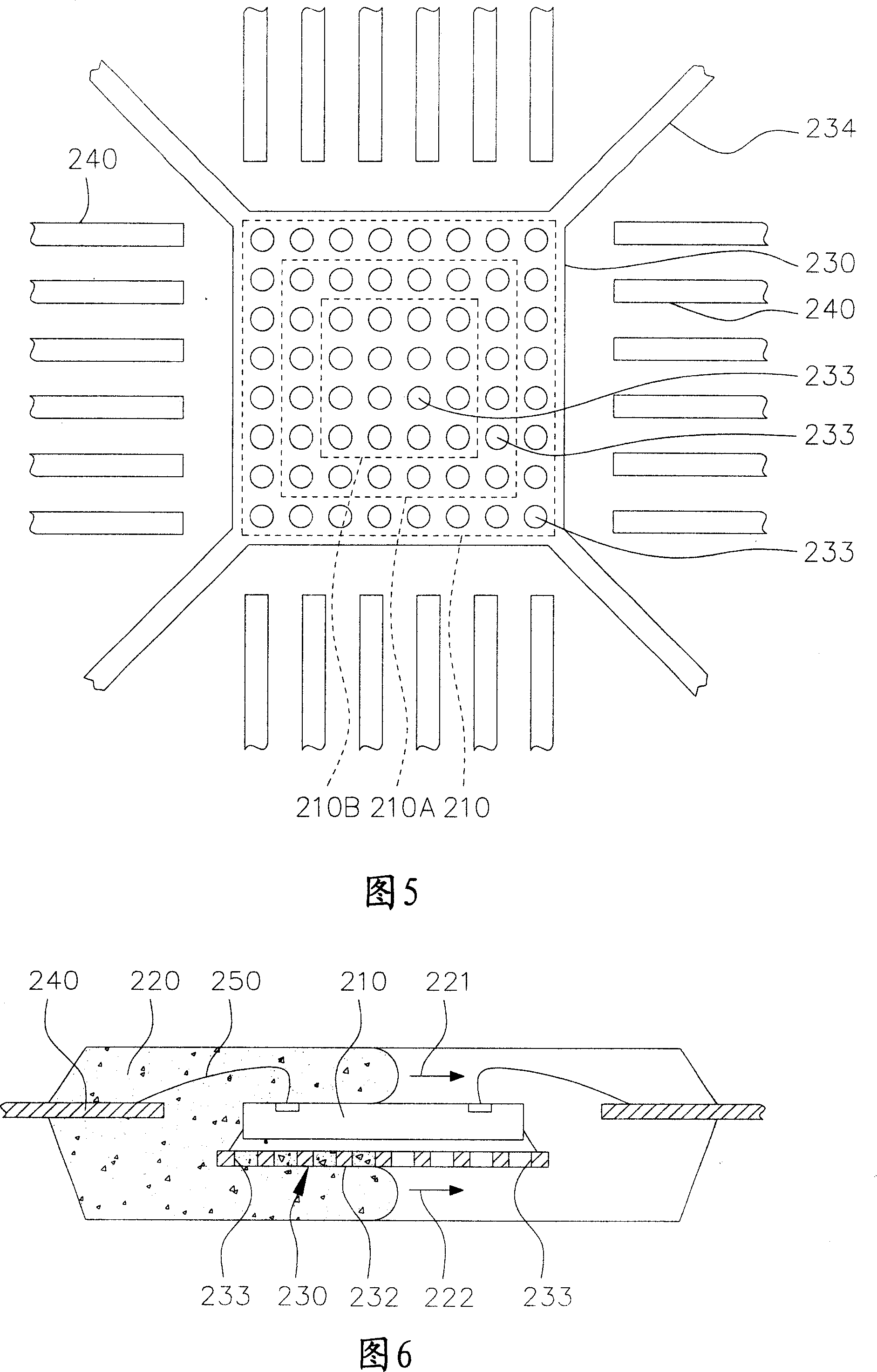

[0066] Please refer to FIG. 10 , which is a schematic diagram of a lead frame of the semiconductor package structure according to a second embodiment of the present invention. In this embodiment, the mold flow bypass holes 333 pass through the upper surface 331 and the lower surface 332 and are formed on the periphery of the shared chip holder 330. In the process, in addition to forming the mold flow bypass holes 333 in stamping, a plurality of selective mold flow bypass holes 333A can be formed on the shared wafer holder 330 at the same time, so that the shared wafer holder 330 330 has mold flow bypass holes arranged in a peripheral arrangement or in a matrix arrangement. The chip 310 is disposed on the upper surface 331 of the shared chip holder 330 , and the plurality of bonding pads 311 of the chip 310 are electrically connected to the pins 340 through a plurality of bonding wires 350 . The molding compound 320 covers the chip 310 and the bonding wires 350 .

[0067] Sin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More